योजक (इलेक्ट्रॉनिक्स): Difference between revisions

No edit summary |

No edit summary |

||

| (10 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{Short description|Digital circuit that produces sums from inputs}} | {{Short description|Digital circuit that produces sums from inputs}} | ||

{{Sidebar arithmetic logic circuits|expand=Components|expand-components=Adder}} | {{Sidebar arithmetic logic circuits|expand=Components|expand-components=Adder}} | ||

एडर | '''एडर''' ऐसा<ref>{{cite book | last=Singh | first=Ajay Kumar | date=2010 | url=https://www.google.com/books/edition/Digital_Vlsi_Design/Gr023E8Kd5QC?hl=en&gbpv=1&dq=adder+summer+circuit&pg=PA321 | title=डिजिटल वीएलएसआई डिजाइन| publisher=Prentice Hall India | page=321 | isbn=9788120341876 | via=Google Books}}</ref> [[डिजिटल सर्किट]] है जो संख्याओं को जोड़ने का कार्य करता है। कई कंप्यूटरों और अन्य प्रकार के [[माइक्रोप्रोसेसर|प्रोसेसरों]] में एयरथमैटिक लॉजिक यूनिट्स (एएलयू) में एडर का [[योग|उपयोग]] किया जाता है। उनका उपयोग प्रोसेसर के अन्य भागों में भी किया जाता है, जहां उनका उपयोग [[पता स्थान|एड्रेस]], [[डेटाबेस सूचकांक|टेबल इंडेक्स]], [[वृद्धि और कमी ऑपरेटरों|इन्क्रीमेंट और डीक्रिमेंट ऑपरेटरों]] और इसी प्रकार के ऑपरेशन को कैलकुलेट करने के लिए किया जाता है। | ||

चूँकि कई संख्याओं के प्रतिनिधित्व के लिए एडर का निर्माण किया जा सकता है, जैसे [[बाइनरी-कोडित दशमलव|बाइनरी-कोडित डेसीमल]] या [[अतिरिक्त -3|एक्सेस-3]], सबसे सरल एडर [[बाइनरी संख्या|बाइनरी संख्याओं]] पर कार्य करते हैं। ऐसे स्तिथि में जहां दो के पूरक या एक के पूरक का उपयोग | चूँकि कई संख्याओं के प्रतिनिधित्व के लिए एडर का निर्माण किया जा सकता है, जैसे [[बाइनरी-कोडित दशमलव|बाइनरी-कोडित डेसीमल]] या [[अतिरिक्त -3|एक्सेस-3]], सबसे सरल एडर [[बाइनरी संख्या|बाइनरी संख्याओं]] पर कार्य करते हैं। ऐसे स्तिथि में जहां दो के पूरक या एक के पूरक का उपयोग नेगेटिव संख्याओं को रिप्रेजेंट करने के लिए किया जा रहा है, एडर को एडर-सब्ट्रैक्टर में मॉडिफाई करना सरल है। अन्य साइंड संख्या रिप्रेजेंटेशन के लिए मूल एडर के निकट अधिक लॉजिक की आवश्यकता होती है। | ||

== बाइनरी एडर == | == बाइनरी एडर == | ||

| Line 9: | Line 9: | ||

=== हाफ एडर === | === हाफ एडर === | ||

[[File:half Adder.svg|right|thumb|हाफ एडर लॉजिक आरेख]] | [[File:half Adder.svg|right|thumb|हाफ एडर लॉजिक आरेख]] | ||

[[File:Halfadder.gif|right|thumb| | [[File:Halfadder.gif|right|thumb|हाफ एडर]]हाफ एडर दो एकल बाइनरी अंक A और B जोड़ता है। इसके दो आउटपुट सम (''S'') और कैरी (''C'') हैं। कैरी सिग्नल बहु-अंकीय जोड़ के अगले अंक में [[पूर्णांक अतिप्रवाह|पूर्णांक ओवरफ्लो]] का प्रतिनिधित्व करता है। योग का मान {{nobreak|2''C'' + ''S''}} सबसे सरल हाफ एडर डिजाइन, दाईं ओर चित्रित, S के लिए [[एक्सओआर गेट|XOR गेट]] और C के लिए गेट सम्मिलित करता है। योग के लिए बूलियन लॉजिक (इस स्तिथि में S) {{nobreak|''A′B'' + ''AB′''}} होगा, जबकि कैरी के लिए (C ) होगा। अपने कैरी आउटपुट को संयोजित करने के लिए OR गेट के अतिरिक्त के साथ, फुल एडर बनाने के लिए दो हाफ एडरों को जोड़ा जा सकता है।<ref name="Lancaster_2004"/>हाफ एडर दो इनपुट बिट्स जोड़ता है कैरी और योग उत्पन्न करता है, जो हाफ एडर के दो आउटपुट हैं। हाफ ऐडर के इनपुट वेरिएबल (कंप्यूटर साइंस) को ऑगेंड और एडेंड बिट कहा जाता है। आउटपुट वैरिएबल योग और कैरी हैं। | ||

हाफ एडर के लिए सत्य तालिका है: | हाफ एडर के लिए सत्य तालिका है: | ||

| Line 28: | Line 28: | ||

|- | |- | ||

|} | |} | ||

[[File:Half adder using NAND gates only.jpg|alt=half adder circuit using NAND gates only|thumb|311x311px|हाफ एडर केवल | [[File:Half adder using NAND gates only.jpg|alt=half adder circuit using NAND gates only|thumb|311x311px|हाफ एडर केवल नैड गेट्स का उपयोग कर रहा है।]] | ||

=== फुल एडर === | === फुल एडर === | ||

| Line 35: | Line 35: | ||

[[File:Fulladder.gif|thumbकील|दाहिना|कार्य में पूर्ण योजक। एक पूर्ण योजक बाइनरी प्रतिनिधित्व में इनपुट में 1s की संख्या देता है।]] | [[File:Fulladder.gif|thumbकील|दाहिना|कार्य में पूर्ण योजक। एक पूर्ण योजक बाइनरी प्रतिनिधित्व में इनपुट में 1s की संख्या देता है।]] | ||

[[File:1-bit full-adder.svg|thumb|right| | [[File:1-bit full-adder.svg|thumb|right|C<sub>in</sub> के साथ 1-बिट पूर्ण एडर के लिए योजनाबद्ध प्रतीक और C<sub>out</sub> बहु-बिट एडर में उनके उपयोग पर बल देने के लिए ब्लॉक के किनारों पर खींचा गया]] | ||

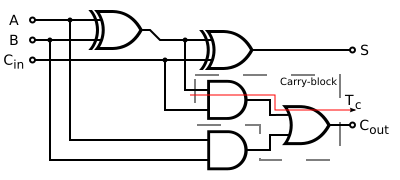

[[File:Full Adder using NAND gates.svg|thumb|right| | [[File:Full Adder using NAND gates.svg|thumb|right|फुल एडर नौ नैड गेट से निर्मित है।]]फुल एडर बाइनरी नंबर जोड़ता है और मानों के साथ-साथ बाहर भी ले जाता है। बिट फुल एडर तीन एक-बिट संख्याएँ जोड़ता है, जिसे प्रायः ''A'', ''B'', और ''C<sub>in</sub>'' के रूप में लिखा जाता है। A, ''B'' और C<sub>''in''</sub> ऑपरेंड हैं, पिछले कम-महत्वपूर्ण चरण से थोड़ा आगे बढ़ाया गया है।<ref name="Mano_1979"/>फुल एडर सामान्यतः एडरों के कैस्केड में घटक होता है, जो 8, 16, 32, आदि बिट बाइनरी संख्याओं को जोड़ता है। सर्किट दो-बिट आउटपुट उत्पन्न करता है। आउटपुट कैरी और योग सामान्यतः सिग्नल C<sub>out</sub> द्वारा दर्शाया जाता है जहाँ S, {{nowrap|2''C''<sub>out</sub> + ''S''}} के योग समान है। | ||

फुल एडर को कई भिन्न-भिन्न विधियों से कार्यान्वित किया जा सकता है जैसे कस्टम [[ट्रांजिस्टर]]- | फुल एडर को कई भिन्न-भिन्न विधियों से कार्यान्वित किया जा सकता है जैसे कस्टम [[ट्रांजिस्टर]]-लेवल सर्किट या अन्य गेट्स से बना है। सबसे सरल कार्यान्वयन इसके साथ है: | ||

{{nowrap|''S'' {{=}} ''A'' ⊕ ''B'' ⊕ ''C''<sub>in</sub>}} तथा | {{nowrap|''S'' {{=}} ''A'' ⊕ ''B'' ⊕ ''C''<sub>in</sub>}} तथा | ||

| Line 47: | Line 47: | ||

इस कार्यान्वयन में, कैरी-आउट आउटपुट से पहले अंतिम OR गेट को परिणामी लॉजिक में परिवर्तित किए बिना XOR गेट द्वारा प्रतिस्थापित किया जा सकता है। ऐसा इसलिए है क्योंकि जब A और B दोनों 1 हैं, तो पद {{nowrap|(''A'' ⊕ ''B'')}} सदैव 0 होता है, और इसलिए {{nowrap|(''C''<sub>in</sub> ⋅ (''A'' ⊕ ''B''))}} केवल 0 हो सकता है। इस प्रकार, अंतिम OR गेट के इनपुट कभी भी दोनों 1 नहीं हो सकते (यह मात्र संयोजन है जिसके लिए OR और XOR आउटपुट भिन्न होते हैं)। | इस कार्यान्वयन में, कैरी-आउट आउटपुट से पहले अंतिम OR गेट को परिणामी लॉजिक में परिवर्तित किए बिना XOR गेट द्वारा प्रतिस्थापित किया जा सकता है। ऐसा इसलिए है क्योंकि जब A और B दोनों 1 हैं, तो पद {{nowrap|(''A'' ⊕ ''B'')}} सदैव 0 होता है, और इसलिए {{nowrap|(''C''<sub>in</sub> ⋅ (''A'' ⊕ ''B''))}} केवल 0 हो सकता है। इस प्रकार, अंतिम OR गेट के इनपुट कभी भी दोनों 1 नहीं हो सकते (यह मात्र संयोजन है जिसके लिए OR और XOR आउटपुट भिन्न होते हैं)। | ||

यदि सर्किट को सरल एकीकृत सर्किट चिप्स का उपयोग करके कार्यान्वित किया जा रहा है, जिसमें प्रति चिप केवल गेट टाइप होता है, तो केवल दो प्रकार के गेटों का उपयोग करना सुविधाजनक होता है। | |||

[[File:Full_Adder_using_NOR_gates.svg|thumb|right|न ही [[पूर्ण योजक| | [[File:Full_Adder_using_NOR_gates.svg|thumb|right|न ही [[पूर्ण योजक|फुल एडर]]]]A और B को हाफ एडर के इनपुट से जोड़कर दो हाफ एडरों से फुल एडर का निर्माण भी किया जा सकता है, फिर इसके योग-आउटपुट S को दूसरे हाफ एडर और C<sub>in</sub> के इनपुट के रूप में लिया जा सकता है। इसके अन्य इनपुट के रूप में, और अंत में दो हाफ एडरों से कैरी आउटपुट OR गेट से जुड़े होते हैं। दूसरे हाफ एडर से योग-आउटपुट फुल एडर का अंतिम योग आउटपुट (S) है OR गेट से आउटपुट अंतिम कैरी आउटपुट (C<sub>out</sub>) है) फुल एडर का महत्वपूर्ण पथ दोनों XOR गेट के माध्यम से चलता है और योग बिट S पर समाप्त होता है। यह मानते हुए कि XOR गेट को पूर्ण होने में 1 डिले होती है, फुल एडर के महत्वपूर्ण पथ द्वारा लगाए गए विलंब के समान है: | ||

:<math>T_\text{FA} = 2 \cdot T_\text{XOR} = 2 D.</math> | :<math>T_\text{FA} = 2 \cdot T_\text{XOR} = 2 D.</math> | ||

कैरी का महत्वपूर्ण पथ ऐडर में XOR गेट से और कैरी-ब्लॉक में 2 गेट (AND और OR) से होकर निकलता है और इसलिए, यदि AND या OR गेट को पूर्ण करने में 1 डिले | कैरी का महत्वपूर्ण पथ ऐडर में XOR गेट से और कैरी-ब्लॉक में 2 गेट (AND और OR) से होकर निकलता है और इसलिए, यदि AND या OR गेट को पूर्ण करने में 1 डिले होता है, तो इसमें डिले होता है | ||

:<math>T_\text{c} = T_\text{XOR} + T_\text{AND} + T_\text{OR} = D + D + D = 3D.</math> | :<math>T_\text{c} = T_\text{XOR} + T_\text{AND} + T_\text{OR} = D + D + D = 3D.</math> | ||

<ref>{{Citation|title=Half Adder and Full Adder Circuits|author-first=Ravi|author-last=Teja|date=2021-04-15|access-date=2021-07-27|url=https://www.electronicshub.org/half-adder-and-full-adder-circuits/#Full_Adder_using_NAND_Gates}}</ref>फुल एडर के लिए सत्य तालिका है: | <ref>{{Citation|title=Half Adder and Full Adder Circuits|author-first=Ravi|author-last=Teja|date=2021-04-15|access-date=2021-07-27|url=https://www.electronicshub.org/half-adder-and-full-adder-circuits/#Full_Adder_using_NAND_Gates}}</ref>फुल एडर के लिए सत्य तालिका है: | ||

| Line 78: | Line 78: | ||

|} | |} | ||

फुल एडर के सभी इनपुटों को इन्वर्ट करने से इसके सभी आउटपुट भी इन्वर्ट हो जाते हैं, जिसका उपयोग फ़ास्ट रिपल-कैरी एडरों के डिज़ाइन में किया जा सकता है, क्योंकि कैरी को इन्वर्ट करने की कोई आवश्यकता नहीं है।<ref name="Fischer"/> | फुल एडर के सभी इनपुटों को इन्वर्ट करने से इसके सभी आउटपुट भी इन्वर्ट हो जाते हैं, जिसका उपयोग फ़ास्ट रिपल-कैरी एडरों के डिज़ाइन में किया जा सकता है, क्योंकि कैरी को इन्वर्ट करने की कोई आवश्यकता नहीं है।<ref name="Fischer"/> | ||

[[File:Inverting_full_adder_CMOS_24T.svg|thumb|[[सीएमओएस]] में | [[File:Inverting_full_adder_CMOS_24T.svg|thumb|[[सीएमओएस]] में एकल-ट्रांजिस्टर कैरी प्रसार विलंब के साथ इनवर्स आउटपुट के साथ फुल एडर<ref name="Fischer"/>]] | ||

=== कई बिट्स का समर्थन करने वाले एडर === | === कई बिट्स का समर्थन करने वाले एडर === | ||

| Line 86: | Line 86: | ||

[[File:RippleCarry2.gif|thumbनेल|दाहिना|दशमलव 4-अंकीय रिपल कैरी ऐडर। एफए = पूर्ण योजक, एचए = आधा योजक।]] | [[File:RippleCarry2.gif|thumbनेल|दाहिना|दशमलव 4-अंकीय रिपल कैरी ऐडर। एफए = पूर्ण योजक, एचए = आधा योजक।]] | ||

N-बिट संख्याओं को जोड़ने के लिए कई फुल एडरों का उपयोग करके लॉजिक | N-बिट संख्याओं को जोड़ने के लिए कई फुल एडरों का उपयोग करके लॉजिक सर्किट बनाना संभव है। प्रत्येक फुल एडर C<sub>in</sub> इनपुट करता है, जो कि C<sub>out</sub> पूर्व एडर के इस प्रकार के एडर को रिपल-कैरी एडर (RCA) कहा जाता है, क्योंकि प्रत्येक बिट रिपल्स को अगले फुल एडर तक ले जाता है। ध्यान दें कि पहले (और केवल पहले) फुल एडर को हाफ एडर द्वारा प्रतिस्थापित किया जा सकता है (यह मानते हुए कि ''C''<sub>in</sub> = 0) पूर्व एडर (Cout n-1) का आउटपुट अगले एडर (Cin) के इनपुट के रूप में पारित हुआ। | ||

रिपल-कैरी एडर का लेआउट सरल है, जो तीव्रता से डिजाइन समय की अनुमति देता है; चूँकि, रिपल-कैरी एडर अपेक्षाकृत स्लो है, क्योंकि प्रत्येक फुल एडर को | रिपल-कैरी एडर का लेआउट सरल है, जो तीव्रता से डिजाइन समय की अनुमति देता है; चूँकि, रिपल-कैरी एडर अपेक्षाकृत स्लो है, क्योंकि प्रत्येक फुल एडर को पूर्व फुल एडर से गणना करने के लिए कैरी बिट की प्रतीक्षा करनी चाहिए। फुल एडर सर्किट के निरीक्षण से गेट विलंब की सरलता से गणना की जा सकती है। प्रत्येक फुल एडर को लॉजिक के तीन स्तरों की आवश्यकता होती है। 32-बिट रिपल-कैरी एडर में, 32 फुल एडर होते हैं, इसलिए महत्वपूर्ण पथ (सबसे व्यर्थ स्थिति) डिले 3 है (इनपुट से पहले एडर में ले जाने के लिए) + 31 × 2 (पश्चात के एडर में प्रसार के लिए) = 65 [[गेट देरी|गेट डिले]] है।<ref name="Adder" />N-बिट कैर्री-रिपल एडर के लिए सबसे व्यर्थ स्थिति डिले के लिए सामान्य समीकरण, योग और कैरी बिट्स दोनों के लिए लेखांकन है<math>T_\text{CRA}(n) = T_\text{HA} + (n-1) \cdot T_\text{c} + T_\text{s} = T_\text{FA} + (n-1) \cdot T_c = 3 D + (n-1) \cdot 2 D = (2n+1) \cdot D.</math> | ||

अल्टरनेटिंग कैरी पोलारिटीज़ और अनुकूलित AND-OR-इनवर्ट गेट्स वाला डिज़ाइन लगभग दोगुना तीव्र हो सकता है।<ref name="Burgess_2011" /><ref name="Fischer">{{Cite web|url=https://sus.ziti.uni-heidelberg.de/Lehre/WS1617_DST/DST_Fischer_06_Einfache_Bloecke_FF.pptx.pdf|title=सरल सर्किट ब्लॉक|accessdate=2021-09-05|archive-url=https://web.archive.org/web/20210905175605/https://sus.ziti.uni-heidelberg.de/Lehre/WS1617_DST/DST_Fischer_06_Einfache_Bloecke_FF.pptx.pdf|archive-date=2021-09-05|last=Fischer|first=P.|publisher=Universität Heidelberg}}</ref>[[File:4-bit carry lookahead adder.svg|thumb|right|कैरी लुकहेड के साथ 4-बिट एडर]] | |||

अल्टरनेटिंग कैरी पोलारिटीज़ और अनुकूलित AND-OR-इनवर्ट गेट्स वाला डिज़ाइन लगभग दोगुना तीव्र हो सकता है।<ref name="Burgess_2011"/><ref name="Fischer">{{Cite web|url=https://sus.ziti.uni-heidelberg.de/Lehre/WS1617_DST/DST_Fischer_06_Einfache_Bloecke_FF.pptx.pdf|title=सरल सर्किट ब्लॉक|accessdate=2021-09-05|archive-url=https://web.archive.org/web/20210905175605/https://sus.ziti.uni-heidelberg.de/Lehre/WS1617_DST/DST_Fischer_06_Einfache_Bloecke_FF.pptx.pdf|archive-date=2021-09-05|last=Fischer|first=P.|publisher=Universität Heidelberg}}</ref>[[File:4-bit carry lookahead adder.svg|thumb|right|कैरी लुकहेड के साथ 4-बिट एडर]] | |||

==== कैरी-लुकहेड एडर ==== | ==== कैरी-लुकहेड एडर ==== | ||

{{main| | {{main|कैरी-लुकहेड एडर}} | ||

कम्प्यूटेशन समय को कम करने के लिए, इंजीनियरों ने [[कैरी-लुकहेड योजक|कैरी-लुकहेड एडर]] (सीएलए) का उपयोग करके दो बाइनरी नंबर जोड़ने के लिए तीव्र विधि तैयार की गई है। वे प्रत्येक बिट स्थिति के लिए दो सिग्नल (P और G) इस पर आधारित है कि क्या कैरी को कम महत्वपूर्ण बिट स्थिति (कम से कम इनपुट 1 है) से प्रचारित किया जाता है, उस बिट स्थिति में उत्पन्न होता है (दोनों इनपुट 1 हैं) ), या उस बिट स्थिति में समाप्त कर (दोनों इनपुट 0 हैं) दिया जाता है। अधिकतम स्थितियों में, P केवल हाफ एडर का योग आउटपुट है और G उसी एडर का आउटपुट है। P और G उत्पन्न होने के पश्चात, प्रत्येक बिट स्थिति के लिए वहन किया जाता है। कुछ उन्नत कैरी-लुकहेड आर्किटेक्चर [[मैनचेस्टर कैरी चेन]], ब्रेंट-कुंग एडर (बीकेए) <ref name="Brent-Kung_1982"/>और कोग्गे-स्टोन एडर (केएसए) हैं।<ref name="Kogge-Stone_1973"/><ref name="ULVD_2015"/> | |||

कुछ अन्य मल्टी-बिट एडर आर्किटेक्चर एडर को ब्लॉक में विभक्त करते हैं। | कुछ अन्य मल्टी-बिट एडर आर्किटेक्चर एडर को ब्लॉक में विभक्त करते हैं। कम्प्यूटेशन समय को अनुकूलित करने के लिए सर्किट के प्रसार विलंब के आधार पर इन ब्लॉकों की लंबाई को भिन्न-भिन्न करना संभव है। इन ब्लॉक आधारित एडरों में [[कैरी-स्किप योजक|कैरी-स्किप एडर]] (या कैरी-बायपास) सम्मिलित है जो प्रत्येक बिट के अतिरिक्त प्रत्येक ब्लॉक के लिए P और G मान निर्धारित करेगा, और [[कैरी-सेलेक्ट ऐडर]] जो योग और कैरी को पूर्व-उत्पन्न करता है ब्लॉक में संभावित कैरी इनपुट (0 या 1) के लिए मान, मल्टीप्लेक्सर्स का उपयोग करके उचित परिणाम का चयन करने के लिए जब कैरी बिट ज्ञात हो। | ||

[[File:64-bit lookahead carry unit.svg|thumb|right|64-बिट एडर]]कई कैरी-लुकहेड एडरों को मिलाकर, और भी बड़े एडर बनाए जा सकते हैं। इसे और भी बड़े एडर बनाने के लिए कई स्तरों पर उपयोग किया जा सकता है। उदाहरण के लिए, | [[File:64-bit lookahead carry unit.svg|thumb|right|64-बिट एडर]]कई कैरी-लुकहेड एडरों को मिलाकर, और भी बड़े एडर बनाए जा सकते हैं। इसे और भी बड़े एडर बनाने के लिए कई स्तरों पर उपयोग किया जा सकता है। उदाहरण के लिए, 64-बिट एडर है जो चार 16-बिट सीएलए का उपयोग करता है जिसमें दो स्तरों के [[अग्रदर्शी वाहक इकाई|लुकहेड केरी यूनिट]] हैं। | ||

अन्य एडर डिज़ाइनों में कैरी-सिलेक्ट एडर, [[सशर्त योग योजक|कंडीशनल सम एडर]], कैरी-स्किप एडर और कैरी-फुल एडर सम्मिलित हैं। | अन्य एडर डिज़ाइनों में कैरी-सिलेक्ट एडर, [[सशर्त योग योजक|कंडीशनल सम एडर]], कैरी-स्किप एडर और कैरी-फुल एडर सम्मिलित हैं। | ||

==== कैरी-सेव एडर्स ==== | ==== कैरी-सेव एडर्स ==== | ||

{{main| | {{main|कैरी-सेव एडर्स}} | ||

यदि एडर | यदि एडर सर्किट तीन या अधिक संख्याओं के योग की गणना करना है, तो कैरी परिणाम का प्रचार न करने से लाभ हो सकता है। इसके अतिरिक्त, तीन-इनपुट एडर का उपयोग किया जाता है, जिससे दो परिणाम उत्पन्न होते हैं: सम और कैरी। कैरी सिग्नल के प्रसार की प्रतीक्षा किए बिना योग और कैरी को पश्चात के 3-नंबर एडर के दो इनपुट में फीड किया जा सकता है। एडर के सभी चरणों के पश्चात, चूँकि, पारंपरिक एडर (जैसे रिपल-कैरी या लुकहेड) का उपयोग अंतिम योग को संयोजित करने और परिणाम ले जाने के लिए किया जाना चाहिए। | ||

===3:2 कम्प्रेसर === | ===3:2 कम्प्रेसर === | ||

फुल एडर को 3:2 | फुल एडर को 3:2 लॉस कंप्रेसर के रूप में देखा जा सकता है: यह तीन बिट इनपुट का योग करता है और परिणाम को दो-बिट संख्या के रूप में रिटर्न होता है; अर्थात्, यह 8 इनपुट मानों को 4 आउटपुट मानों में मैप करता है। इस प्रकार, उदाहरण के लिए, 101 के बाइनरी इनपुट के परिणामस्वरूप आउटपुट {{nobr|1 + 0 + 1 {{=}} 10}} होता है (डेसीमल संख्या 2)। कैरी-आउट परिणाम के बिट का प्रतिनिधित्व करता है, जबकि योग बिट शून्य का प्रतिनिधित्व करता है। इसी प्रकार, हाफ एडर को 2: 2 लॉस कंप्रेसर के रूप में उपयोग किया जा सकता है, चार संभावित इनपुट को तीन संभावित आउटपुट में कंप्रेसर कर सकता है। | ||

ऐसे कंप्रेशर्स का उपयोग तीन या अधिक योगों के योग को गति देने के लिए किया जा सकता है। यदि एडर तीन हैं, तो लेआउट को [[कैरी-सेव योजक|कैरी-सेव एडर]] के रूप में जाना जाता है। यदि एडर चार या अधिक हैं, तो कंप्रेशर्स की अधिक लेयर आवश्यक है, और | ऐसे कंप्रेशर्स का उपयोग तीन या अधिक योगों के योग को गति देने के लिए किया जा सकता है। यदि एडर तीन हैं, तो लेआउट को [[कैरी-सेव योजक|कैरी-सेव एडर]] के रूप में जाना जाता है। यदि एडर चार या अधिक हैं, तो कंप्रेशर्स की अधिक लेयर आवश्यक है, और सर्किट के लिए विभिन्न संभावित डिज़ाइन हैं: सबसे सरल [[दद्दा ट्री]] और [[वालेस का पेड़|वालेस]] [[दद्दा ट्री|ट्री]] हैं। इस प्रकार के सर्किट का उपयोग [[बाइनरी गुणक|बाइनरी मल्टीप्लायर]] में सबसे अधिक किया जाता है, यही कारण है कि इन सर्किट को दद्दा और वालेस मल्टीप्लायर के रूप में भी जाना जाता है। | ||

== क्वांटम एडर == | == क्वांटम एडर == | ||

[[File:Quantum Full Adder.png|thumb|[[टोफोली गेट]] और CNOT गेट्स का उपयोग करते हुए क्वांटम | [[File:Quantum Full Adder.png|thumb|[[टोफोली गेट]] और CNOT गेट्स का उपयोग करते हुए क्वांटम फुल एडर। इस छवि में बिंदीदार वर्ग से घिरा हुआ [[सीएनओटी]]-गेट छोड़ा जा सकता है यदि B आउटपुट को पुनर्स्थापित करने के लिए [[अगणना]] की आवश्यकता नहीं है।]]केवल टोफोली गेट और सीएनओटी [[क्वांटम लॉजिक गेट]] का उपयोग करके, क्वांटम फुल और हाफ-एडर्स का उत्पादन संभव है।<ref>{{cite journal | last=Feynman | first=Richard P. | title=क्वांटम मैकेनिकल कंप्यूटर| journal=Foundations of Physics | publisher=Springer Science and Business Media LLC | volume=16 | issue=6 | year=1986 | issn=0015-9018 | doi=10.1007/bf01886518 | pages=507–531| bibcode=1986FoPh...16..507F | s2cid=122076550 }}</ref><ref>{{cite web|url=https://www.quantum-inspire.com/kbase/full-adder/|title=कोड उदाहरण: क्वांटम पूर्ण योजक|publisher=QuTech (Delft University of Technology (TU Delft) and the Netherlands Organisation for Applied Scientific Research (TNO))}}</ref><ref>{{cite journal|author=Dibyendu Chatterjee, Arijit Roy|journal=[[Progress of Theoretical and Experimental Physics]]|title=एक ट्रांसमोन-आधारित क्वांटम अर्ध-योजक योजना|year=2015|volume=2015|issue=9|doi=10.1093/ptep/ptv122|bibcode=2015PTEP.2015i3A02C|url=https://paperity.org/p/73955611/a-transmon-based-quantum-half-adder-scheme}}</ref> क्लासिकल रिवेर्सिबल कम्प्यूटेशन में समान सर्किट भी प्रारम्भ किए जा सकते हैं, क्योंकि सीएनओटी और टॉफोली दोनों क्लासिकल लॉजिक गेट भी हैं। | ||

चूंकि [[क्वांटम फूरियर रूपांतरण]] में कम [[सर्किट जटिलता| | चूंकि [[क्वांटम फूरियर रूपांतरण|क्वांटम फौरिएर ट्रांसफॉर्म]] में कम [[सर्किट जटिलता|सर्किट कॉम्प्लेक्सिटी]] होती है, इसलिए इसे कुशलता से संख्याओं को जोड़ने के लिए भी उपयोग किया जा सकता है।<ref>{{cite arXiv|last=Draper|first=Thomas G.|eprint=quant-ph/0008033|title=क्वांटम कंप्यूटर पर जोड़|date=7 Aug 2000}}</ref><ref>{{cite journal|last1=Ruiz-Perez|first1=Lidia|last2=Juan Carlos|first2=Garcia-Escartin|title=क्वांटम फूरियर रूपांतरण के साथ क्वांटम अंकगणित|journal=Quantum Information Processing|arxiv=1411.5949v2|date=2 May 2017|volume=16|issue=6|page=152 |doi=10.1007/s11128-017-1603-1|bibcode=2017QuIP...16..152R |s2cid=10948948}}</ref> | ||

== एनालॉग एडर == | == एनालॉग एडर == | ||

जैसे बाइनरी एडर्स में, दो इनपुट | जैसे बाइनरी एडर्स में, दो इनपुट करंट के संयोजन से प्रभावी रूप से उन कर्रेंटस को साथ जोड़ा जाता है। हार्डवेयर की बाधाओं के अंदर, नॉन-बाइनरी सिग्नल (अर्थात 2 से अधिक हायर) के सम को कैलकुलेट करने के लिए जोड़ा जा सकता है। समिंग एम्प्लीफायर के रूप में भी जाना जाता है,<ref>{{cite web | url=https://www.electronics-tutorials.ws/opamp/opamp_4.html | title=सममिंग एम्पलीफायर एक ऑप-एम्प वोल्टेज एडर है| date=22 August 2013 }}</ref> इस टेक्निक का उपयोग अतिरिक्त सर्किट में ट्रांजिस्टर की संख्या को कम करने के लिए किया जा सकता है। | ||

== यह भी देखें == | == यह भी देखें == | ||

* बाइनरी | * बाइनरी मल्टीप्लायर | ||

* | * सब्ट्रैक्टर | ||

* [[इलेक्ट्रॉनिक मिक्सर]] - एनालॉग सिग्नल जोड़ने के लिए | * [[इलेक्ट्रॉनिक मिक्सर]]- एनालॉग सिग्नल जोड़ने के लिए | ||

==संदर्भ== | ==संदर्भ== | ||

| Line 147: | Line 145: | ||

==बाहरी संबंध== | ==बाहरी संबंध== | ||

* [https://www.ecsis.riec.tohoku.ac.jp/topics/amg/i-amg/doc/algorithm Hardware algorithms for arithmetic modules], includes description of several adder layouts with figures. | * [https://www.ecsis.riec.tohoku.ac.jp/topics/amg/i-amg/doc/algorithm Hardware algorithms for arithmetic modules], includes description of several adder layouts with figures. | ||

| Line 173: | Line 154: | ||

{{CPU technologies|state=collapsed}} | {{CPU technologies|state=collapsed}} | ||

{{ | {{DEFAULTSORT:Adder (Electronics)}} | ||

[[Category:Articles with hatnote templates targeting a nonexistent page|Adder (Electronics)]] | |||

[[Category:CS1 errors]] | |||

[[Category:Collapse templates|Adder (Electronics)]] | |||

[[Category:Created On 26/11/2022|Adder (Electronics)]] | |||

[[Category:Lua-based templates|Adder (Electronics)]] | |||

[[Category:Machine Translated Page|Adder (Electronics)]] | |||

[[Category:Navigational boxes| ]] | |||

[[Category:Navigational boxes without horizontal lists|Adder (Electronics)]] | |||

[[Category:Pages using collapsible list without both background and text-align in titlestyle|margin:0;padding:0;text-align:center;width:100% ]] | |||

[[Category:Pages using sidebar with the child parameter|Adder (Electronics)]] | |||

[[Category:Pages with script errors|Adder (Electronics)]] | |||

[[Category:Short description with empty Wikidata description|Adder (Electronics)]] | |||

[[Category:Sidebars with styles needing conversion|Adder (Electronics)]] | |||

[[Category:Template documentation pages|Documentation/doc]] | |||

[[Category:Templates Translated in Hindi|Adder (Electronics)]] | |||

[[Category:Templates Vigyan Ready|Adder (Electronics)]] | |||

[[Category:Templates generating microformats|Adder (Electronics)]] | |||

[[Category:Templates that add a tracking category|Adder (Electronics)]] | |||

[[Category:Templates that are not mobile friendly|Adder (Electronics)]] | |||

[[Category:Templates that generate short descriptions|Adder (Electronics)]] | |||

[[Category:Templates using TemplateData|Adder (Electronics)]] | |||

[[Category:Wikipedia metatemplates|Adder (Electronics)]] | |||

[[Category:एडर्स (इलेक्ट्रॉनिक्स)| ]] | [[Category:एडर्स (इलेक्ट्रॉनिक्स)| ]] | ||

[[Category:बाइनरी अंकगणित|Adder (Electronics)]] | |||

[[Category: | |||

Latest revision as of 11:59, 20 October 2023

| Part of a series on | |||||||

| Arithmetic logic circuits | |||||||

|---|---|---|---|---|---|---|---|

| Quick navigation | |||||||

|

Components

|

|||||||

|

See also |

|||||||

एडर ऐसा[1] डिजिटल सर्किट है जो संख्याओं को जोड़ने का कार्य करता है। कई कंप्यूटरों और अन्य प्रकार के प्रोसेसरों में एयरथमैटिक लॉजिक यूनिट्स (एएलयू) में एडर का उपयोग किया जाता है। उनका उपयोग प्रोसेसर के अन्य भागों में भी किया जाता है, जहां उनका उपयोग एड्रेस, टेबल इंडेक्स, इन्क्रीमेंट और डीक्रिमेंट ऑपरेटरों और इसी प्रकार के ऑपरेशन को कैलकुलेट करने के लिए किया जाता है।

चूँकि कई संख्याओं के प्रतिनिधित्व के लिए एडर का निर्माण किया जा सकता है, जैसे बाइनरी-कोडित डेसीमल या एक्सेस-3, सबसे सरल एडर बाइनरी संख्याओं पर कार्य करते हैं। ऐसे स्तिथि में जहां दो के पूरक या एक के पूरक का उपयोग नेगेटिव संख्याओं को रिप्रेजेंट करने के लिए किया जा रहा है, एडर को एडर-सब्ट्रैक्टर में मॉडिफाई करना सरल है। अन्य साइंड संख्या रिप्रेजेंटेशन के लिए मूल एडर के निकट अधिक लॉजिक की आवश्यकता होती है।

बाइनरी एडर

हाफ एडर

हाफ एडर दो एकल बाइनरी अंक A और B जोड़ता है। इसके दो आउटपुट सम (S) और कैरी (C) हैं। कैरी सिग्नल बहु-अंकीय जोड़ के अगले अंक में पूर्णांक ओवरफ्लो का प्रतिनिधित्व करता है। योग का मान 2C + S सबसे सरल हाफ एडर डिजाइन, दाईं ओर चित्रित, S के लिए XOR गेट और C के लिए गेट सम्मिलित करता है। योग के लिए बूलियन लॉजिक (इस स्तिथि में S) A′B + AB′ होगा, जबकि कैरी के लिए (C ) होगा। अपने कैरी आउटपुट को संयोजित करने के लिए OR गेट के अतिरिक्त के साथ, फुल एडर बनाने के लिए दो हाफ एडरों को जोड़ा जा सकता है।[2]हाफ एडर दो इनपुट बिट्स जोड़ता है कैरी और योग उत्पन्न करता है, जो हाफ एडर के दो आउटपुट हैं। हाफ ऐडर के इनपुट वेरिएबल (कंप्यूटर साइंस) को ऑगेंड और एडेंड बिट कहा जाता है। आउटपुट वैरिएबल योग और कैरी हैं।

हाफ एडर के लिए सत्य तालिका है:

इनपुट आउटपुट A B C S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0

फुल एडर

फुल एडर बाइनरी नंबर जोड़ता है और मानों के साथ-साथ बाहर भी ले जाता है। बिट फुल एडर तीन एक-बिट संख्याएँ जोड़ता है, जिसे प्रायः A, B, और Cin के रूप में लिखा जाता है। A, B और Cin ऑपरेंड हैं, पिछले कम-महत्वपूर्ण चरण से थोड़ा आगे बढ़ाया गया है।[3]फुल एडर सामान्यतः एडरों के कैस्केड में घटक होता है, जो 8, 16, 32, आदि बिट बाइनरी संख्याओं को जोड़ता है। सर्किट दो-बिट आउटपुट उत्पन्न करता है। आउटपुट कैरी और योग सामान्यतः सिग्नल Cout द्वारा दर्शाया जाता है जहाँ S, 2Cout + S के योग समान है।

फुल एडर को कई भिन्न-भिन्न विधियों से कार्यान्वित किया जा सकता है जैसे कस्टम ट्रांजिस्टर-लेवल सर्किट या अन्य गेट्स से बना है। सबसे सरल कार्यान्वयन इसके साथ है:

S = A ⊕ B ⊕ Cin तथा

Cout = (A ⋅ B) + (Cin ⋅ (A ⊕ B)).

इस कार्यान्वयन में, कैरी-आउट आउटपुट से पहले अंतिम OR गेट को परिणामी लॉजिक में परिवर्तित किए बिना XOR गेट द्वारा प्रतिस्थापित किया जा सकता है। ऐसा इसलिए है क्योंकि जब A और B दोनों 1 हैं, तो पद (A ⊕ B) सदैव 0 होता है, और इसलिए (Cin ⋅ (A ⊕ B)) केवल 0 हो सकता है। इस प्रकार, अंतिम OR गेट के इनपुट कभी भी दोनों 1 नहीं हो सकते (यह मात्र संयोजन है जिसके लिए OR और XOR आउटपुट भिन्न होते हैं)।

यदि सर्किट को सरल एकीकृत सर्किट चिप्स का उपयोग करके कार्यान्वित किया जा रहा है, जिसमें प्रति चिप केवल गेट टाइप होता है, तो केवल दो प्रकार के गेटों का उपयोग करना सुविधाजनक होता है।

A और B को हाफ एडर के इनपुट से जोड़कर दो हाफ एडरों से फुल एडर का निर्माण भी किया जा सकता है, फिर इसके योग-आउटपुट S को दूसरे हाफ एडर और Cin के इनपुट के रूप में लिया जा सकता है। इसके अन्य इनपुट के रूप में, और अंत में दो हाफ एडरों से कैरी आउटपुट OR गेट से जुड़े होते हैं। दूसरे हाफ एडर से योग-आउटपुट फुल एडर का अंतिम योग आउटपुट (S) है OR गेट से आउटपुट अंतिम कैरी आउटपुट (Cout) है) फुल एडर का महत्वपूर्ण पथ दोनों XOR गेट के माध्यम से चलता है और योग बिट S पर समाप्त होता है। यह मानते हुए कि XOR गेट को पूर्ण होने में 1 डिले होती है, फुल एडर के महत्वपूर्ण पथ द्वारा लगाए गए विलंब के समान है:

कैरी का महत्वपूर्ण पथ ऐडर में XOR गेट से और कैरी-ब्लॉक में 2 गेट (AND और OR) से होकर निकलता है और इसलिए, यदि AND या OR गेट को पूर्ण करने में 1 डिले होता है, तो इसमें डिले होता है

[4]फुल एडर के लिए सत्य तालिका है:

Inputs Outputs A B Cin Cout S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

फुल एडर के सभी इनपुटों को इन्वर्ट करने से इसके सभी आउटपुट भी इन्वर्ट हो जाते हैं, जिसका उपयोग फ़ास्ट रिपल-कैरी एडरों के डिज़ाइन में किया जा सकता है, क्योंकि कैरी को इन्वर्ट करने की कोई आवश्यकता नहीं है।[5]

कई बिट्स का समर्थन करने वाले एडर

रिप्पल-कैर्री एडर

N-बिट संख्याओं को जोड़ने के लिए कई फुल एडरों का उपयोग करके लॉजिक सर्किट बनाना संभव है। प्रत्येक फुल एडर Cin इनपुट करता है, जो कि Cout पूर्व एडर के इस प्रकार के एडर को रिपल-कैरी एडर (RCA) कहा जाता है, क्योंकि प्रत्येक बिट रिपल्स को अगले फुल एडर तक ले जाता है। ध्यान दें कि पहले (और केवल पहले) फुल एडर को हाफ एडर द्वारा प्रतिस्थापित किया जा सकता है (यह मानते हुए कि Cin = 0) पूर्व एडर (Cout n-1) का आउटपुट अगले एडर (Cin) के इनपुट के रूप में पारित हुआ।

रिपल-कैरी एडर का लेआउट सरल है, जो तीव्रता से डिजाइन समय की अनुमति देता है; चूँकि, रिपल-कैरी एडर अपेक्षाकृत स्लो है, क्योंकि प्रत्येक फुल एडर को पूर्व फुल एडर से गणना करने के लिए कैरी बिट की प्रतीक्षा करनी चाहिए। फुल एडर सर्किट के निरीक्षण से गेट विलंब की सरलता से गणना की जा सकती है। प्रत्येक फुल एडर को लॉजिक के तीन स्तरों की आवश्यकता होती है। 32-बिट रिपल-कैरी एडर में, 32 फुल एडर होते हैं, इसलिए महत्वपूर्ण पथ (सबसे व्यर्थ स्थिति) डिले 3 है (इनपुट से पहले एडर में ले जाने के लिए) + 31 × 2 (पश्चात के एडर में प्रसार के लिए) = 65 गेट डिले है।[6]N-बिट कैर्री-रिपल एडर के लिए सबसे व्यर्थ स्थिति डिले के लिए सामान्य समीकरण, योग और कैरी बिट्स दोनों के लिए लेखांकन है

अल्टरनेटिंग कैरी पोलारिटीज़ और अनुकूलित AND-OR-इनवर्ट गेट्स वाला डिज़ाइन लगभग दोगुना तीव्र हो सकता है।[7][5]

कैरी-लुकहेड एडर

कम्प्यूटेशन समय को कम करने के लिए, इंजीनियरों ने कैरी-लुकहेड एडर (सीएलए) का उपयोग करके दो बाइनरी नंबर जोड़ने के लिए तीव्र विधि तैयार की गई है। वे प्रत्येक बिट स्थिति के लिए दो सिग्नल (P और G) इस पर आधारित है कि क्या कैरी को कम महत्वपूर्ण बिट स्थिति (कम से कम इनपुट 1 है) से प्रचारित किया जाता है, उस बिट स्थिति में उत्पन्न होता है (दोनों इनपुट 1 हैं) ), या उस बिट स्थिति में समाप्त कर (दोनों इनपुट 0 हैं) दिया जाता है। अधिकतम स्थितियों में, P केवल हाफ एडर का योग आउटपुट है और G उसी एडर का आउटपुट है। P और G उत्पन्न होने के पश्चात, प्रत्येक बिट स्थिति के लिए वहन किया जाता है। कुछ उन्नत कैरी-लुकहेड आर्किटेक्चर मैनचेस्टर कैरी चेन, ब्रेंट-कुंग एडर (बीकेए) [8]और कोग्गे-स्टोन एडर (केएसए) हैं।[9][10]

कुछ अन्य मल्टी-बिट एडर आर्किटेक्चर एडर को ब्लॉक में विभक्त करते हैं। कम्प्यूटेशन समय को अनुकूलित करने के लिए सर्किट के प्रसार विलंब के आधार पर इन ब्लॉकों की लंबाई को भिन्न-भिन्न करना संभव है। इन ब्लॉक आधारित एडरों में कैरी-स्किप एडर (या कैरी-बायपास) सम्मिलित है जो प्रत्येक बिट के अतिरिक्त प्रत्येक ब्लॉक के लिए P और G मान निर्धारित करेगा, और कैरी-सेलेक्ट ऐडर जो योग और कैरी को पूर्व-उत्पन्न करता है ब्लॉक में संभावित कैरी इनपुट (0 या 1) के लिए मान, मल्टीप्लेक्सर्स का उपयोग करके उचित परिणाम का चयन करने के लिए जब कैरी बिट ज्ञात हो।

कई कैरी-लुकहेड एडरों को मिलाकर, और भी बड़े एडर बनाए जा सकते हैं। इसे और भी बड़े एडर बनाने के लिए कई स्तरों पर उपयोग किया जा सकता है। उदाहरण के लिए, 64-बिट एडर है जो चार 16-बिट सीएलए का उपयोग करता है जिसमें दो स्तरों के लुकहेड केरी यूनिट हैं।

अन्य एडर डिज़ाइनों में कैरी-सिलेक्ट एडर, कंडीशनल सम एडर, कैरी-स्किप एडर और कैरी-फुल एडर सम्मिलित हैं।

कैरी-सेव एडर्स

यदि एडर सर्किट तीन या अधिक संख्याओं के योग की गणना करना है, तो कैरी परिणाम का प्रचार न करने से लाभ हो सकता है। इसके अतिरिक्त, तीन-इनपुट एडर का उपयोग किया जाता है, जिससे दो परिणाम उत्पन्न होते हैं: सम और कैरी। कैरी सिग्नल के प्रसार की प्रतीक्षा किए बिना योग और कैरी को पश्चात के 3-नंबर एडर के दो इनपुट में फीड किया जा सकता है। एडर के सभी चरणों के पश्चात, चूँकि, पारंपरिक एडर (जैसे रिपल-कैरी या लुकहेड) का उपयोग अंतिम योग को संयोजित करने और परिणाम ले जाने के लिए किया जाना चाहिए।

3:2 कम्प्रेसर

फुल एडर को 3:2 लॉस कंप्रेसर के रूप में देखा जा सकता है: यह तीन बिट इनपुट का योग करता है और परिणाम को दो-बिट संख्या के रूप में रिटर्न होता है; अर्थात्, यह 8 इनपुट मानों को 4 आउटपुट मानों में मैप करता है। इस प्रकार, उदाहरण के लिए, 101 के बाइनरी इनपुट के परिणामस्वरूप आउटपुट 1 + 0 + 1 = 10 होता है (डेसीमल संख्या 2)। कैरी-आउट परिणाम के बिट का प्रतिनिधित्व करता है, जबकि योग बिट शून्य का प्रतिनिधित्व करता है। इसी प्रकार, हाफ एडर को 2: 2 लॉस कंप्रेसर के रूप में उपयोग किया जा सकता है, चार संभावित इनपुट को तीन संभावित आउटपुट में कंप्रेसर कर सकता है।

ऐसे कंप्रेशर्स का उपयोग तीन या अधिक योगों के योग को गति देने के लिए किया जा सकता है। यदि एडर तीन हैं, तो लेआउट को कैरी-सेव एडर के रूप में जाना जाता है। यदि एडर चार या अधिक हैं, तो कंप्रेशर्स की अधिक लेयर आवश्यक है, और सर्किट के लिए विभिन्न संभावित डिज़ाइन हैं: सबसे सरल दद्दा ट्री और वालेस ट्री हैं। इस प्रकार के सर्किट का उपयोग बाइनरी मल्टीप्लायर में सबसे अधिक किया जाता है, यही कारण है कि इन सर्किट को दद्दा और वालेस मल्टीप्लायर के रूप में भी जाना जाता है।

क्वांटम एडर

केवल टोफोली गेट और सीएनओटी क्वांटम लॉजिक गेट का उपयोग करके, क्वांटम फुल और हाफ-एडर्स का उत्पादन संभव है।[11][12][13] क्लासिकल रिवेर्सिबल कम्प्यूटेशन में समान सर्किट भी प्रारम्भ किए जा सकते हैं, क्योंकि सीएनओटी और टॉफोली दोनों क्लासिकल लॉजिक गेट भी हैं।

चूंकि क्वांटम फौरिएर ट्रांसफॉर्म में कम सर्किट कॉम्प्लेक्सिटी होती है, इसलिए इसे कुशलता से संख्याओं को जोड़ने के लिए भी उपयोग किया जा सकता है।[14][15]

एनालॉग एडर

जैसे बाइनरी एडर्स में, दो इनपुट करंट के संयोजन से प्रभावी रूप से उन कर्रेंटस को साथ जोड़ा जाता है। हार्डवेयर की बाधाओं के अंदर, नॉन-बाइनरी सिग्नल (अर्थात 2 से अधिक हायर) के सम को कैलकुलेट करने के लिए जोड़ा जा सकता है। समिंग एम्प्लीफायर के रूप में भी जाना जाता है,[16] इस टेक्निक का उपयोग अतिरिक्त सर्किट में ट्रांजिस्टर की संख्या को कम करने के लिए किया जा सकता है।

यह भी देखें

- बाइनरी मल्टीप्लायर

- सब्ट्रैक्टर

- इलेक्ट्रॉनिक मिक्सर- एनालॉग सिग्नल जोड़ने के लिए

संदर्भ

- ↑ Singh, Ajay Kumar (2010). डिजिटल वीएलएसआई डिजाइन. Prentice Hall India. p. 321. ISBN 9788120341876 – via Google Books.

- ↑ Lancaster, Geoffrey A. (2004). Excel HSC Software Design and Development. Pascal Press. p. 180. ISBN 978-1-74125175-3.

- ↑ Mano, M. Morris (1979). Digital Logic and Computer Design. Prentice-Hall. pp. 119–123. ISBN 978-0-13-214510-7.

- ↑ Teja, Ravi (2021-04-15), Half Adder and Full Adder Circuits, retrieved 2021-07-27

- ↑ 5.0 5.1 5.2 Fischer, P. "सरल सर्किट ब्लॉक" (PDF). Universität Heidelberg. Archived from the original (PDF) on 2021-09-05. Retrieved 2021-09-05.

- ↑ Satpathy, Pinaki (2016). Design and Implementation of Carry Select Adder Using T-Spice. Anchor Academic Publishing. p. 22. ISBN 978-3-96067058-2.

- ↑ Burgess, Neil (2011). Fast Ripple-Carry Adders in Standard-Cell CMOS VLSI. 20th IEEE Symposium on Computer Arithmetic. pp. 103–111.

- ↑ Brent, Richard Peirce; Kung, Hsiang Te (March 1982). "A Regular Layout for Parallel Adders". IEEE Transactions on Computers. C-31 (3): 260–264. doi:10.1109/TC.1982.1675982. ISSN 0018-9340. S2CID 17348212. Archived from the original on September 24, 2017.

- ↑ Kogge, Peter Michael; Stone, Harold S. (August 1973). "A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equations". IEEE Transactions on Computers. C-22 (8): 786–793. doi:10.1109/TC.1973.5009159. S2CID 206619926.

- ↑ Reynders, Nele; Dehaene, Wim (2015). Ultra-Low-Voltage Design of Energy-Efficient Digital Circuits. doi:10.1007/978-3-319-16136-5. ISBN 978-3-319-16135-8. ISSN 1872-082X. LCCN 2015935431.

{{cite book}}:|journal=ignored (help) - ↑ Feynman, Richard P. (1986). "क्वांटम मैकेनिकल कंप्यूटर". Foundations of Physics. Springer Science and Business Media LLC. 16 (6): 507–531. Bibcode:1986FoPh...16..507F. doi:10.1007/bf01886518. ISSN 0015-9018. S2CID 122076550.

- ↑ "कोड उदाहरण: क्वांटम पूर्ण योजक". QuTech (Delft University of Technology (TU Delft) and the Netherlands Organisation for Applied Scientific Research (TNO)).

- ↑ Dibyendu Chatterjee, Arijit Roy (2015). "एक ट्रांसमोन-आधारित क्वांटम अर्ध-योजक योजना". Progress of Theoretical and Experimental Physics. 2015 (9). Bibcode:2015PTEP.2015i3A02C. doi:10.1093/ptep/ptv122.

- ↑ Draper, Thomas G. (7 Aug 2000). "क्वांटम कंप्यूटर पर जोड़". arXiv:quant-ph/0008033.

- ↑ Ruiz-Perez, Lidia; Juan Carlos, Garcia-Escartin (2 May 2017). "क्वांटम फूरियर रूपांतरण के साथ क्वांटम अंकगणित". Quantum Information Processing. 16 (6): 152. arXiv:1411.5949v2. Bibcode:2017QuIP...16..152R. doi:10.1007/s11128-017-1603-1. S2CID 10948948.

- ↑ "सममिंग एम्पलीफायर एक ऑप-एम्प वोल्टेज एडर है". 22 August 2013.

अग्रिम पठन

- Liu, Tso-Kai; Hohulin, Keith R.; Shiau, Lih-Er; Muroga, Saburo (January 1974). "Optimal One-Bit Full-Adders with Different Types of Gates". IEEE Transactions on Computers. Bell Laboratories: IEEE. C-23 (1): 63–70. doi:10.1109/T-C.1974.223778. ISSN 0018-9340. S2CID 7746693.

- Lai, Hung Chi; Muroga, Saburo (September 1979). "Minimum Binary Parallel Adders with NOR (NAND) Gates". IEEE Transactions on Computers. IEEE. C-28 (9): 648–659. doi:10.1109/TC.1979.1675433. S2CID 23026844.

- Mead, Carver; Conway, Lynn (1980) [December 1979]. Introduction to VLSI Systems (1 ed.). Reading, MA, USA: Addison-Wesley. Bibcode:1980aw...book.....M. ISBN 978-0-20104358-7. Retrieved 2018-05-12.

- Davio, Marc; Dechamps, Jean-Pierre; Thayse, André (1983). Digital Systems, with algorithm implementation (1 ed.). Philips Research Laboratory, Brussels, Belgium: John Wiley & Sons, a Wiley-Interscience Publication. ISBN 978-0-471-10413-1. LCCN 82-2710.

- Gosling, John (January 1971). "Review of High-Speed Addition Techniques". Proc. IEE. 188 (1): 29–35. doi:10.1049/piee.1971.0004.

बाहरी संबंध

- Hardware algorithms for arithmetic modules, includes description of several adder layouts with figures.

- 8-bit Full Adder and Subtractor, a demonstration of an interactive Full Adder built in JavaScript solely for learning purposes.

- Interactive Full Adder Simulation (requires Java), Interactive Full Adder circuit constructed with Teahlab's online circuit simulator.

- Interactive Half Adder Simulation (requires Java), Half Adder circuit built with Teahlab's circuit simulator.

- 4-bit Full Adder Simulation built in Verilog, and the accompanying Ripple Carry Full Adder Video Tutorial

- Shirriff, Ken (November 2020). "Reverse-engineering the carry-lookahead circuit in the Intel 8008 processor".