एकीकृत परिपथ: Difference between revisions

(Created page with "{{short description|Electronic circuit formed on a small, flat piece of semiconductor material}} {{Redirect|Silicon chip|the electronics magazine|Silicon Chip}} {{Redirect|Mic...") |

No edit summary |

||

| Line 4: | Line 4: | ||

{{Use dmy dates|date=October 2020}} | {{Use dmy dates|date=October 2020}} | ||

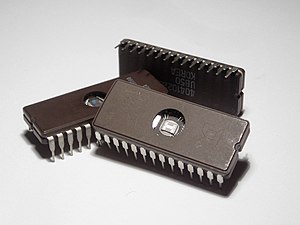

[[File:Microchips.jpg|thumb| | [[File:Microchips.jpg|thumb|EPROM | इरेज़ेबल प्रोग्रामेबल रीड-ओनली मेमोरी (EPROM) ड्यूल इन-लाइन पैकेज में इंटीग्रेटेड सर्किट। इन सेमीकंडक्टर पैकेज में एक पारदर्शी विंडो होती है जो अंदर डाई (एकीकृत सर्किट) दिखाती है। चिप को पराबैंगनी प्रकाश में उजागर करके मेमोरी को मिटाने के लिए विंडो का उपयोग किया जाता है।]] | ||

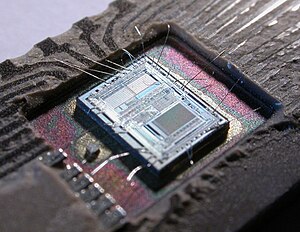

[[File:EPROM Microchip SuperMacro.jpg|right|thumb| | [[File:EPROM Microchip SuperMacro.jpg|right|thumb|EPROM मेमोरी माइक्रोचिप से इंटीग्रेटेड सर्किट, मेमोरी ब्लॉक्स, सपोर्टिंग सर्किट्री और फाइन सिल्वर वायर्स जो इंटीग्रेटेड सर्किट को पैकेजिंग के लेग्स से जोड़ते हैं, दिखाते हैं]] | ||

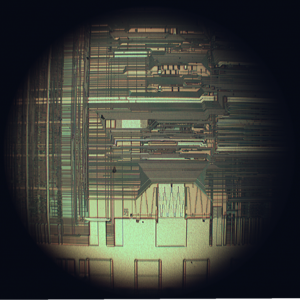

[[File:Siliconchip by shapeshifter.png|right|thumb| | [[File:Siliconchip by shapeshifter.png|right|thumb|पॉलीसिलिकॉन (गुलाबी), कुओं (ग्रेश), और सब्सट्रेट (हरा) के नीचे प्लैनराइज्ड कॉपर इंटरकनेक्ट की चार परतों के माध्यम से एक एकीकृत सर्किट का आभासी विवरण]] | ||

एक एकीकृत | एक एकीकृत परिपथ या अखंड एकीकृत परिपथ (जिसे आईसी, एक चिप या माइक्रोचिप भी कहा जाता है) अर्धचालक सामग्री के एक छोटे से फ्लैट टुकड़े (या चिप) पर इलेक्ट्रॉनिक सर्किट का एक सेट है, आमतौर पर सिलिकॉन। छोटे MOSFETs (धातु-ऑक्साइड-अर्धचालक क्षेत्र-प्रभाव ट्रांजिस्टर) की ट्रांजिस्टर गणना एक छोटी चिप में एकीकृत होती है। इसका परिणाम सर्किट में होता है जो असतत इलेक्ट्रॉनिक घटकों के निर्माण की तुलना में छोटे, तेज और कम खर्चीले होते हैं। एकीकृत सर्किट डिजाइन के लिए आईसी की बड़े पैमाने पर उत्पादन क्षमता, विश्वसनीयता और बिल्डिंग-ब्लॉक दृष्टिकोण ने असतत ट्रांजिस्टर का उपयोग करके डिजाइन के स्थान पर मानकीकृत आईसी को तेजी से अपनाना सुनिश्चित किया है। IC अब लगभग सभी इलेक्ट्रॉनिक उपकरणों में उपयोग किया जाता है और इसने इलेक्ट्रॉनिक्स की दुनिया में क्रांति ला दी है। कंप्यूटर, मोबाइल फोन और अन्य घरेलू उपकरण अब आधुनिक समाज की संरचना के अविभाज्य अंग हैं, जो आधुनिक कंप्यूटर प्रोसेसर और माइक्रोकंट्रोलर जैसे छोटे आकार और कम लागत के आईसी द्वारा संभव बनाया गया है। | ||

धातु-ऑक्साइड-सिलिकॉन (एमओएस) सेमीकंडक्टर डिवाइस निर्माण में तकनीकी प्रगति द्वारा बहुत बड़े पैमाने पर एकीकरण को व्यावहारिक बनाया गया था। 1960 के दशक में उनकी उत्पत्ति के बाद से, चिप्स के आकार, गति और क्षमता में काफी प्रगति हुई है, तकनीकी विकास द्वारा संचालित है जो एक ही आकार के चिप्स पर अधिक से अधिक MOS ट्रांजिस्टर फिट करते हैं - एक आधुनिक चिप में एक में कई अरबों MOS ट्रांजिस्टर हो सकते हैं। मानव नाखून के आकार का क्षेत्रफल। मोटे तौर पर मूर के नियम का पालन करते हुए ये प्रगति, आज के कंप्यूटर चिप्स की क्षमता का लाखों गुना और 1970 के दशक की शुरुआत के कंप्यूटर चिप्स की गति से हजारों गुना अधिक है। | |||

असतत सर्किट पर आईसी के दो मुख्य लाभ हैं: लागत और प्रदर्शन। लागत कम है क्योंकि चिप्स, उनके सभी घटकों के साथ, एक समय में एक ट्रांजिस्टर के निर्माण के बजाय फोटोलिथोग्राफी द्वारा एक इकाई के रूप में मुद्रित होते हैं। इसके अलावा, पैक किए गए आईसी असतत सर्किट की तुलना में बहुत कम सामग्री का उपयोग करते हैं। प्रदर्शन उच्च है क्योंकि आईसी के घटक जल्दी से स्विच करते हैं और उनके छोटे आकार और निकटता के कारण तुलनात्मक रूप से कम बिजली की खपत करते हैं। आईसी का मुख्य नुकसान उन्हें डिजाइन करने और आवश्यक फोटोमास्क बनाने की उच्च लागत है। इस उच्च प्रारंभिक लागत का मतलब है कि आईसी केवल व्यावसायिक रूप से व्यवहार्य हैं जब पैमाने की अर्थव्यवस्थाएं प्रत्याशित हैं। | |||

== शब्दावली == | == शब्दावली == | ||

एक एकीकृत सर्किट के रूप में परिभाषित किया गया है:<ref>{{cite web |url=http://www.jedec.org/standards-documents/dictionary/terms/integrated-circuit-ic |title=Integrated circuit (IC) |publisher=[[JEDEC]]}}</ref> < | एक एकीकृत सर्किट के रूप में परिभाषित किया गया है:<ref>{{cite web |url=http://www.jedec.org/standards-documents/dictionary/terms/integrated-circuit-ic |title=Integrated circuit (IC) |publisher=[[JEDEC]]}}</ref> <blockquote>एक सर्किट जिसमें सभी या कुछ सर्किट तत्व अविभाज्य रूप से जुड़े हुए हैं और विद्युत रूप से जुड़े हुए हैं ताकि इसे निर्माण और वाणिज्य के उद्देश्यों के लिए अविभाज्य माना जा सके।</blockquote> इस परिभाषा को पूरा करने वाले सर्किट कई अलग-अलग उपयोग करके बनाए जा सकते हैं पतली फिल्म ट्रांजिस्टर, मोटी फिल्म प्रौद्योगिकी | मोटी फिल्म प्रौद्योगिकियों, या संकर एकीकृत सर्किट सहित प्रौद्योगिकियों। हालांकि, सामान्य उपयोग में एकीकृत सर्किट एकल-टुकड़ा सर्किट निर्माण को संदर्भित करने के लिए आया है जिसे मूल रूप से एक मोनोलिथिक एकीकृत सर्किट के रूप में जाना जाता है, जिसे अक्सर सिलिकॉन के एक टुकड़े पर बनाया जाता है।<ref>{{cite web |title=The first monolithic integrated circuits |url=http://homepages.nildram.co.uk/~wylie/ICs/monolith.htm |quote=Nowadays when people say 'integrated circuit' they usually mean a monolithic IC, where the entire circuit is constructed in a single piece of silicon. |author=Wylie, Andrew |year=2009 |access-date=14 March 2011}}</ref><ref>{{cite book| last1 = Horowitz| first1 = Paul| author-link1 = Paul Horowitz| last2 = Hill| first2 = Winfield| author-link2 = Winfield Hill| title = The Art of Electronics| edition = 2nd| year = 1989| publisher = Cambridge University Press| isbn = 978-0-521-37095-0| page = [https://archive.org/details/artofelectronics00horo/page/61 61]| quote = Integrated circuits, which have largely replaced circuits constructed from discrete transistors, are themselves merely arrays of transistors and other components built from a single chip of semiconductor material.| url = https://archive.org/details/artofelectronics00horo/page/61}}</ref> | ||

== इतिहास == | == इतिहास == | ||

[[File:Kilby solid circuit.jpg|thumb|right|1958 से जैक किल्बी का मूल हाइब्रिड इंटीग्रेटेड सर्किट। यह पहला | [[File:Kilby solid circuit.jpg|thumb|right|1958 से जैक किल्बी का मूल हाइब्रिड इंटीग्रेटेड सर्किट। यह पहला इंटीग्रेटेड सर्किट था, और इसे जर्मेनियम से बनाया गया था।]] | ||

एक | 1920 के दशक से लोवे 3NF वैक्यूम ट्यूब एक उपकरण (जैसे आधुनिक IC) में कई घटकों के संयोजन का एक प्रारंभिक प्रयास था। आईसी के विपरीत, इसे कर से बचने के उद्देश्य से डिजाइन किया गया था, जैसा कि जर्मनी में, रेडियो रिसीवर के पास एक कर था जो एक रेडियो रिसीवर के कितने ट्यूब धारकों के आधार पर लगाया जाता था। इसने रेडियो रिसीवर्स को सिंगल ट्यूब होल्डर रखने की अनुमति दी। | ||

एक एकीकृत सर्किट की | एक एकीकृत सर्किट की प्रारंभिक अवधारणा 1949 में वापस आती है, जब जर्मन इंजीनियर वर्नर जैकोबिक<ref name="computerhistory-ic">{{cite web|url=https://www.computerhistory.org/atchm/who-invented-the-ic/|title=Who Invented the IC? |department=@CHM Blog |publisher=Computer History Museum |date=20 August 2014}}</ref> (सीमेंस एजी | सीमेंस एजी)<ref>{{cite web|url=http://integratedcircuithelp.com/invention.html |title=Integrated circuits help Invention |publisher=Integratedcircuithelp.com |access-date=2012-08-13}}</ref> एक एकीकृत-सर्किट-जैसे अर्धचालक प्रवर्धक उपकरण के लिए पेटेंट दायर किया<ref name="jacobi1949">{{patent|DE|833366|W. Jacobi/SIEMENS AG: "Halbleiterverstärker" priority filing on 14 April 1949, published on 15 May 1952.}}</ref> तीन-चरण एम्पलीफायर व्यवस्था में एक सामान्य सब्सट्रेट पर पांच ट्रांजिस्टर दिखा रहा है। जैकोबी ने अपने पेटेंट के विशिष्ट औद्योगिक अनुप्रयोगों के रूप में छोटे और सस्ते श्रवण यंत्रों का खुलासा किया। उनके पेटेंट के तत्काल व्यावसायिक उपयोग की सूचना नहीं मिली है। | ||

अवधारणा का एक | अवधारणा का एक अन्य प्रारंभिक प्रस्तावक जेफ्री डमर (1909-2002) था, जो ब्रिटिश रक्षा मंत्रालय (यूनाइटेड किंगडम) के रॉयल रडार प्रतिष्ठान के लिए काम कर रहे एक रडार वैज्ञानिक थे। डमर ने 7 मई 1952 को वाशिंगटन, डीसी | वाशिंगटन, डीसी में गुणवत्ता इलेक्ट्रॉनिक घटकों में प्रगति पर संगोष्ठी में जनता के लिए विचार प्रस्तुत किया।<ref>[http://www.epn-online.com/page/22909/the-hapless-tale-of-geoffrey-dummer-this-is-the-sad-.html "The Hapless Tale of Geoffrey Dummer"] {{webarchive|url=https://web.archive.org/web/20130511181443/http://www.epn-online.com/page/22909/the-hapless-tale-of-geoffrey-dummer-this-is-the-sad-.html |date=11 May 2013 }} (n.d.) (HTML), ''Electronic Product News'', accessed 8 July 2008.</ref> उन्होंने अपने विचारों को प्रचारित करने के लिए सार्वजनिक रूप से कई संगोष्ठियां दीं और 1956 में इस तरह के एक सर्किट के निर्माण का असफल प्रयास किया। 1953 और 1957 के बीच, सिडनी डार्लिंगटन और यासुओ तारुई (इलेक्ट्रोटेक्निकल लेबोरेटरी) ने समान चिप डिजाइनों का प्रस्ताव रखा, जहां कई ट्रांजिस्टर एक सामान्य सक्रिय क्षेत्र साझा कर सकते थे, लेकिन वहां उन्हें एक दूसरे से अलग करने के लिए कोई पी-एन जंक्शन अलगाव नहीं था।<ref name="computerhistory-ic"/> | ||

मोनोलिथिक इंटीग्रेटेड सर्किट चिप को कर्ट लेहोवेक द्वारा | मोनोलिथिक इंटीग्रेटेड सर्किट चिप को जीन होर्नी द्वारा प्लानर प्रक्रिया के आविष्कारों और कर्ट लेहोवेक द्वारा पी-एन जंक्शन अलगाव द्वारा सक्षम किया गया था। होर्नी का आविष्कार सतह पर निष्क्रियता पर मोहम्मद एम। अटाला के काम के साथ-साथ फुलर और डिट्ज़ेनबर्गर के काम पर बोरॉन और फास्फोरस अशुद्धियों के सिलिकॉन में प्रसार, कार्ल फ्रॉश और लिंकन डेरिक के सतह संरक्षण पर काम और चिह-तांग साह के प्रसार पर काम पर बनाया गया था। ऑक्साइड द्वारा मास्किंग।<ref>{{Cite book|last=Saxena|first=Arjum|title=Invention of Integrated Circuits: Untold Important Facts|publisher=World Scientific|year=2009|pages=95–103}}</ref> | ||

=== | === प्रथम एकीकृत परिपथ === | ||

{{Main|Invention of the integrated circuit}} | {{Main|Invention of the integrated circuit}} | ||

{{See also|Planar process|p–n junction isolation|Surface passivation}} | {{See also|Planar process|p–n junction isolation|Surface passivation}} | ||

[[File:Robert Noyce with Motherboard 1959.png|thumb|रॉबर्ट | [[File:Robert Noyce with Motherboard 1959.png|thumb|रॉबर्ट नॉयस ने 1959 में पहले मोनोलिथिक इंटीग्रेटेड सर्किट का आविष्कार किया था। चिप को सिलिकॉन से बनाया गया था।]] | ||

आईसी के लिए एक अग्रदूत विचार छोटे सिरेमिक | आईसी के लिए एक अग्रदूत विचार छोटे सिरेमिक सबस्ट्रेट्स (तथाकथित माइक्रोमोड्यूल) बनाना था,<ref name=micromodules/>प्रत्येक में एक छोटा सा घटक होता है। घटकों को तब एकीकृत किया जा सकता है और एक द्विआयामी या त्रिआयामी कॉम्पैक्ट ग्रिड में तारित किया जा सकता है। यह विचार, जो 1957 में बहुत आशाजनक लग रहा था, अमेरिकी सेना को जैक किल्बी द्वारा प्रस्तावित किया गया था<ref name="micromodules" />और अल्पकालिक माइक्रोमॉड्यूल प्रोग्राम (1951 के प्रोजेक्ट टिंकर्टॉय के समान) का नेतृत्व किया।<ref name= micromodules >{{Cite web|url=http://www.eetimes.com/special/special_issues/millennium/milestones/kilby.html|title=Micromodules: the ultimate package|last=Rostky|first=George|website=EE Times|archive-url=https://web.archive.org/web/20100107111717/http://www.eetimes.com/special/special_issues/millennium/milestones/kilby.html|archive-date=2010-01-07|access-date=2018-04-23}}</ref><ref>{{Cite web|url=http://www.chipsetc.com/the-rca-micromodule.html|title=The RCA Micromodule|website=Vintage Computer Chip Collectibles, Memorabilia & Jewelry|access-date=2018-04-23}}</ref><ref>{{Cite book|url=https://books.google.com/books?id=tdCjBQAAQBAJ&q=micromodule&pg=PA392|title=American Microelectronics Data Annual 1964–65|last1=Dummer|first1=G.W.A.|last2=Robertson|first2=J. Mackenzie|date=2014-05-16|publisher=Elsevier|isbn=978-1-4831-8549-1|pages=392–397, 405–406}}</ref> हालांकि, जैसे-जैसे परियोजना गति प्राप्त कर रही थी, किल्बी एक नए, क्रांतिकारी डिजाइन के साथ आया: आईसी। | ||

टेक्सास इंस्ट्रूमेंट्स द्वारा नियोजित, किल्बी ने जुलाई 1958 में एकीकृत सर्किट से संबंधित अपने प्रारंभिक विचारों को दर्ज किया, 12 सितंबर 1958 को एक एकीकृत सर्किट के पहले कामकाजी उदाहरण | टेक्सास इंस्ट्रूमेंट्स द्वारा नव नियोजित, किल्बी ने जुलाई 1958 में एकीकृत सर्किट से संबंधित अपने प्रारंभिक विचारों को दर्ज किया, 12 सितंबर 1958 को एक एकीकृत सर्किट के पहले कामकाजी उदाहरण को सफलतापूर्वक प्रदर्शित किया।<ref name="TIJackBuilt">[http://www.ti.com/corp/docs/kilbyctr/jackbuilt.shtml ''The Chip that Jack Built''], (c. 2008), (HTML), Texas Instruments, Retrieved 29 May 2008.</ref> 6 फरवरी 1959 के अपने पेटेंट आवेदन में,<ref>Kilby, Jack S. "Miniaturized Electronic Circuits", {{US Patent|3138743}}, filed 6 February 1959, issued 23 June 1964.</ref> किल्बी ने अपने नए उपकरण को सेमीकंडक्टर सामग्री का एक निकाय बताया... जिसमें इलेक्ट्रॉनिक सर्किट के सभी घटक पूरी तरह से एकीकृत हैं।<ref>{{cite book| last = Winston| first = Brian| title = Media Technology and Society: A History: From the Telegraph to the Internet| url = https://books.google.com/books?id=gfeCXlElJTwC&pg=PA221| year = 1998| publisher = Routledge| isbn = 978-0-415-14230-4| page = 221 }}</ref> नए आविष्कार के लिए पहला ग्राहक अमेरिकी वायु सेना था।<ref>{{cite web|url=http://www.ti.com/corp/docs/company/history/timeline/defense/1960/docs/61-first_ic.htm |title=Texas Instruments – 1961 First IC-based computer |publisher=Ti.com |access-date=2012-08-13}}</ref> किल्बी ने एकीकृत सर्किट के आविष्कार में अपने हिस्से के लिए भौतिकी में 2000 का नोबेल पुरस्कार जीता।<ref>[http://nobelprize.org/nobel_prizes/physics/laureates/2000/press.html "The Nobel Prize in Physics 2000"], nobelprize.org (10 October 2000)</ref> हालांकि, किल्बी का आविष्कार एक मोनोलिथिक इंटीग्रेटेड सर्किट (मोनोलिथिक आईसी) चिप के बजाय एक हाइब्रिड इंटीग्रेटेड सर्किट (हाइब्रिड आईसी) था।<ref name="Saxena140">{{cite book |last1=Saxena |first1=Arjun N. |title=Invention of Integrated Circuits: Untold Important Facts |date=2009 |publisher=[[World Scientific]] |isbn=9789812814456 |page=140 |url=https://books.google.com/books?id=-3lpDQAAQBAJ&pg=PA140}}</ref> किल्बी के आईसी में बाहरी तार कनेक्शन थे, जिससे बड़े पैमाने पर उत्पादन करना मुश्किल हो गया।<ref name="nasa">{{cite web |title=Integrated circuits |url=https://www.hq.nasa.gov/alsj/ic-pg3.html |website=[[NASA]] |access-date=13 August 2019}}</ref> | ||

किल्बी के | किल्बी के आधे साल बाद, फेयरचाइल्ड सेमीकंडक्टर में रॉबर्ट नॉयस ने पहली सच्ची मोनोलिथिक आईसी चिप का आविष्कार किया।<ref name="computerhistory1959">{{cite web |title=1959: Practical Monolithic Integrated Circuit Concept Patented |url=https://www.computerhistory.org/siliconengine/practical-monolithic-integrated-circuit-concept-patented/ |website=[[Computer History Museum]] |access-date=13 August 2019}}</ref><ref name="nasa"/>यह एकीकृत सर्किट की एक नई किस्म थी, जो किल्बी के कार्यान्वयन से अधिक व्यावहारिक थी। नॉयस का डिजाइन सिलिकॉन से बना था, जबकि किल्बी की चिप जर्मेनियम से बनी थी। नॉयस के मोनोलिथिक आईसी ने सभी घटकों को सिलिकॉन की एक चिप पर रखा और उन्हें तांबे की लाइनों से जोड़ा।<ref name="nasa"/>नॉयस का मोनोलिथिक आईसी प्लानर प्रक्रिया का उपयोग करके सेमीकंडक्टर डिवाइस फैब्रिकेशन था, जिसे 1959 की शुरुआत में उनके सहयोगी जीन होर्नी ने विकसित किया था। आधुनिक आईसी चिप्स नॉयस के मोनोलिथिक आईसी पर आधारित हैं,<ref name="computerhistory1959"/><ref name="nasa"/>किल्बी के हाइब्रिड आईसी के बजाय।<ref name="Saxena140"/> | ||

नासा का अपोलो कार्यक्रम 1961 और 1965 के बीच एकीकृत | नासा का अपोलो कार्यक्रम 1961 और 1965 के बीच एकीकृत परिपथों का सबसे बड़ा एकल उपभोक्ता था।<ref name="eldon">Hall, | ||

Eldon C. (1996). | Eldon C. (1996). | ||

[https://books.google.com/books?id=G8Dml1x55r0C "Journey to the Moon: The History of the Apollo Guidance Computer"]. American Institute of Aeronautics and Astronautics. pp. 18–19. {{ISBN|9781563471858}} | [https://books.google.com/books?id=G8Dml1x55r0C "Journey to the Moon: The History of the Apollo Guidance Computer"]. American Institute of Aeronautics and Astronautics. pp. 18–19. {{ISBN|9781563471858}} | ||

| Line 43: | Line 43: | ||

=== | === टीटीएल एकीकृत परिपथ === | ||

{{Main|Transistor–transistor logic}} | {{Main|Transistor–transistor logic}} | ||

ट्रांजिस्टर - | ट्रांजिस्टर-ट्रांजिस्टर लॉजिक (TTL) को जेम्स एल. बुई द्वारा 1960 के दशक की शुरुआत में TRW Inc. में विकसित किया गया था। TTL 1970 से 1980 के दशक के दौरान प्रमुख एकीकृत सर्किट तकनीक बन गया।<ref>{{cite web |title=Computer Pioneers – James L. Buie |url=https://history.computer.org/pioneers/buie.html |website=[[IEEE Computer Society]] |access-date=25 May 2020}}</ref> | ||

टीटीएल एकीकृत सर्किट | दर्जनों टीटीएल एकीकृत सर्किट मिनीकंप्यूटर और मेनफ्रेम कंप्यूटर की केंद्रीय प्रसंस्करण इकाई के निर्माण का एक मानक तरीका था। आईबीएम 360 मेनफ्रेम, पीडीपी-11 मिनीकंप्यूटर और डेस्कटॉप डेटापॉइंट 2200 जैसे कंप्यूटर बाइपोलर जंक्शन ट्रांजिस्टर इंटीग्रेटेड सर्किट से बनाए गए थे।<ref name="tmx_shirriff" />या तो टीटीएल या इससे भी तेज एमिटर-कपल्ड लॉजिक (ईसीएल)। | ||

=== | === एमओएस इंटीग्रेटेड सर्किट === | ||

{{See|MOSFET applications#MOS integrated circuit}} | {{See|MOSFET applications#MOS integrated circuit}} | ||

{{See also|List of semiconductor scale examples|Mixed-signal integrated circuit|Moore's law|Three-dimensional integrated circuit|Transistor count|Very Large Scale Integration}} | {{See also|List of semiconductor scale examples|Mixed-signal integrated circuit|Moore's law|Three-dimensional integrated circuit|Transistor count|Very Large Scale Integration}} | ||

लगभग सभी आधुनिक | लगभग सभी आधुनिक IC चिप्स मेटल-ऑक्साइड-सेमीकंडक्टर (MOS) इंटीग्रेटेड सर्किट हैं, जो MOSFETs (मेटल-ऑक्साइड-सिलिकॉन फील्ड-इफेक्ट ट्रांजिस्टर) से निर्मित होते हैं।<ref name="Kuo">{{cite journal |last1=Kuo |first1=Yue |title=Thin Film Transistor Technology—Past, Present, and Future |journal=The Electrochemical Society Interface |date=1 January 2013 |volume=22 |issue=1 |pages=55–61 |doi=10.1149/2.F06131if |bibcode=2013ECSIn..22a..55K |url=https://www.electrochem.org/dl/interface/spr/spr13/spr13_p055_061.pdf }}</ref> MOSFET (जिसे MOS ट्रांजिस्टर के रूप में भी जाना जाता है), जिसका आविष्कार मोहम्मद एम। अटाला और डॉन कहंग ने 1959 में बेल लैब्स में किया था।<ref>{{cite web |title=1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated |url=https://www.computerhistory.org/siliconengine/metal-oxide-semiconductor-mos-transistor-demonstrated/ |website=[[Computer History Museum]]}}</ref> बहुत बड़े पैमाने पर एकीकरण | उच्च-घनत्व एकीकृत परिपथों का निर्माण करना संभव बना दिया।<ref name="computerhistory-transistor">{{cite web |title=Who Invented the Transistor? |author=Laws, David |url=https://www.computerhistory.org/atchm/who-invented-the-transistor/ |website=[[Computer History Museum]] |date=4 December 2013 }}</ref> द्विध्रुवी ट्रांजिस्टर के विपरीत, जिसमें एक चिप पर ट्रांजिस्टर के पी-एन जंक्शन अलगाव के लिए कई चरणों की आवश्यकता होती है, एमओएसएफईटी को ऐसे चरणों की आवश्यकता नहीं होती है, लेकिन आसानी से एक दूसरे से अलग किया जा सकता है।<ref name="Bassett53">{{cite book |last1=Bassett |first1=Ross Knox |title=To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology |date=2002 |publisher=[[Johns Hopkins University Press]] |isbn=978-0-8018-6809-2 |pages=53–4 |url=https://books.google.com/books?id=Qge1DUt7qDUC&pg=PA53}}</ref> 1961 में डॉन कहंग ने एकीकृत सर्किट के लिए इसके लाभ की ओर इशारा किया था।<ref name="Bassett22">{{cite book |last1=Bassett |first1=Ross Knox |title=To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology |date=2007 |publisher=[[Johns Hopkins University Press]] |isbn=9780801886393 |pages=22–25 |url=https://books.google.com/books?id=UUbB3d2UnaAC&pg=PA22}}</ref> IEEE मील के पत्थर की सूची में 1958 में Kilby द्वारा पहला एकीकृत सर्किट शामिल है,<ref>{{cite web |url=http://www.ieeeghn.org/wiki/index.php/Milestones:First_Semiconductor_Integrated_Circuit_%28IC%29,_1958 |title=Milestones:First Semiconductor Integrated Circuit (IC), 1958 |work=IEEE Global History Network |publisher=IEEE |access-date=3 August 2011}}</ref> 1959 में होर्नी की प्लानर प्रक्रिया और नॉयस का प्लानर आईसी, और 1959 में अटाला और कहंग द्वारा एमओएसएफईटी।<ref>{{Cite web|url=https://ethw.org/Milestones:List_of_IEEE_Milestones|title=Milestones:List of IEEE Milestones – Engineering and Technology History Wiki|website=ethw.org|date=9 December 2020 }}</ref> | ||

सबसे पहले प्रायोगिक MOS IC का निर्माण किया जाने वाला 16-ट्रांजिस्टर चिप था जिसे 1962 में RCA में फ्रेड हेमैन और स्टीवन हॉफस्टीन द्वारा बनाया गया था।<ref name="computerhistory-digital">{{cite web |title=Tortoise of Transistors Wins the Race – CHM Revolution |url=https://www.computerhistory.org/revolution/digital-logic/12/279 |website=[[Computer History Museum]] |access-date=22 July 2019}}</ref> जनरल माइक्रोइलेक्ट्रॉनिक ने बाद में 1964 में पहला वाणिज्यिक MOS एकीकृत सर्किट पेश किया,<ref name="computerhistory1964">{{cite web|url=http://www.computerhistory.org/semiconductor/timeline/1964-Commecial.html|title=1964 – First Commercial MOS IC Introduced|website=[[Computer History Museum]]}}</ref> रॉबर्ट नॉर्मन द्वारा विकसित एक 120-ट्रांजिस्टर शिफ्ट रजिस्टर।<ref name="computerhistory-digital"/>1964 तक, एमओएस चिप्स द्विध्रुवी जंक्शन ट्रांजिस्टर चिप्स की तुलना में उच्च ट्रांजिस्टर घनत्व और कम विनिर्माण लागत तक पहुंच गए थे। मूर के नियम द्वारा अनुमानित दर से एमओएस चिप्स जटिलता में और बढ़ गए, जिससे 1960 के दशक के अंत तक एक एकल एमओएस चिप पर सैकड़ों ट्रांजिस्टर के साथ बड़े पैमाने पर एकीकरण (एलएसआई) हो गया।<ref name="ieee">{{cite journal |last1=Shirriff |first1=Ken |title=The Surprising Story of the First Microprocessors |journal=[[IEEE Spectrum]] |volume=53 |issue=9 |pages=48–54 |date=30 August 2016 |publisher=[[Institute of Electrical and Electronics Engineers]] |url=https://spectrum.ieee.org/tech-history/silicon-revolution/the-surprising-story-of-the-first-microprocessors|doi=10.1109/MSPEC.2016.7551353 |s2cid=32003640 }}</ref> | |||

रॉबर्ट | 1967 में बेल लैब्स में रॉबर्ट केर्विन, डोनाल्ड एल. क्लेन और जॉन सरेस द्वारा स्व-संरेखित गेट (सिलिकॉन-गेट) MOSFET के विकास के बाद,<ref>{{cite web |title=1968: Silicon Gate Technology Developed for ICs |url=https://www.computerhistory.org/siliconengine/silicon-gate-technology-developed-for-ics/ |website=[[Computer History Museum]] |access-date=22 July 2019}}</ref> स्व-संरेखित गेटों के साथ पहली सिलिकॉन-गेट एमओएस आईसी तकनीक, सभी आधुनिक सीएमओएस एकीकृत सर्किटों का आधार, 1968 में फेडेरिको फागिन द्वारा फेयरचाइल्ड सेमीकंडक्टर में विकसित किया गया था।<ref>{{cite web |title=1968: Silicon Gate Technology Developed for ICs |url=https://www.computerhistory.org/siliconengine/silicon-gate-technology-developed-for-ics/ |website=The Silicon Engine |publisher=[[Computer History Museum]] |access-date=13 October 2019}}</ref> कंप्यूटिंग के लिए एमओएस एलएसआई चिप्स का आवेदन पहले माइक्रोप्रोसेसरों का आधार था, क्योंकि इंजीनियरों ने यह पहचानना शुरू कर दिया था कि एक एकल एमओएस एलएसआई चिप पर एक पूर्ण कंप्यूटर प्रोसेसर शामिल हो सकता है। इसके कारण 1970 के दशक की शुरुआत में माइक्रोप्रोसेसर और माइक्रोकंट्रोलर का आविष्कार हुआ।<ref name="ieee"/>1970 के दशक की शुरुआत में, MOS इंटीग्रेटेड सर्किट टेक्नोलॉजी ने एक चिप पर 10,000 से अधिक ट्रांजिस्टर के बहुत बड़े पैमाने पर एकीकरण (VLSI) को सक्षम किया।<ref>{{cite journal |last1=Hittinger |first1=William C. |title=Metal–Oxide–Semiconductor Technology |journal=Scientific American |date=1973 |volume=229 |issue=2 |pages=48–59 |jstor=24923169 |doi=10.1038/scientificamerican0873-48 |bibcode=1973SciAm.229b..48H }}</ref> | ||

सबसे पहले, एमओएस-आधारित | सबसे पहले, एमओएस-आधारित कंप्यूटर केवल तभी समझ में आते थे जब उच्च घनत्व की आवश्यकता होती थी, जैसे एयरोस्पेस और पॉकेट कैलकुलेटर। पूरी तरह से टीटीएल से निर्मित कंप्यूटर, जैसे कि 1970 डेटापॉइंट 2200, 1972 के इंटेल 8008 जैसे सिंगल-चिप एमओएस माइक्रोप्रोसेसरों की तुलना में 1980 के दशक की शुरुआत तक बहुत तेज और अधिक शक्तिशाली थे।<ref name="tmx_shirriff">केन शिरिफ। [https://www.righto.com/2015/05/the-texas-instruments-tmx-1795-first.html टेक्सास इंस्ट्रूमेंट्स टीएमएक्स 1795: (लगभग) पहले, भूल गए माइक्रोप्रोसेसर]। 2015.</ref> | ||

आईसी प्रौद्योगिकी में | आईसी प्रौद्योगिकी में प्रगति, मुख्य रूप से सेमीकंडक्टर डिवाइस फैब्रिकेशन और बड़े चिप्स, ने एक एकीकृत सर्किट में एमओएस ट्रांजिस्टर की ट्रांजिस्टर गिनती को हर दो साल में दोगुना करने की अनुमति दी है, एक प्रवृत्ति जिसे मूर के नियम के रूप में जाना जाता है। मूर ने मूल रूप से कहा था कि यह हर साल दोगुना हो जाएगा, लेकिन उन्होंने 1975 में हर दो साल में दावे को बदल दिया। | ||

रेफरी>{{Cite web|url=https://www.cnet.com/news/moores-law-to-roll-on-for-another-decade/|title=Moore's Law to roll on for another decade|last=Kanellos|first=Michael|website=CNET|date=February 11, 2003}}</ref> इस बढ़ी हुई क्षमता का उपयोग लागत घटाने और कार्यक्षमता बढ़ाने के लिए किया गया है। सामान्य तौर पर, जैसे-जैसे सुविधा का आकार सिकुड़ता जाता है, IC के संचालन के लगभग हर पहलू में सुधार होता है। डेनार्ड स्केलिंग (MOSFET स्केलिंग) द्वारा परिभाषित संबंधों के माध्यम से, प्रति ट्रांजिस्टर की लागत और प्रति ट्रांजिस्टर कम-शक्ति वाले इलेक्ट्रॉनिक्स कम हो जाते हैं, जबकि कंप्यूटर मेमोरी और क्लॉक रेट बढ़ जाते हैं। रेफरी>{{cite news |author=Davari, Bijan, Robert H. Dennard, and Ghavam G. Shahidi |title=CMOS scaling for high performance and low power-the next ten years |journal=Proceedings of the IEEE |volume=83 |issue=4 |year=1995 |pages=595–606 |url=http://www.cisl.columbia.edu/courses/spring-2002/ee6930/papers/high_perform_scaling.pdf}}</ref> क्योंकि गति, क्षमता और बिजली की खपत का लाभ अंतिम उपयोगकर्ता के लिए स्पष्ट है, निर्माताओं के बीच महीन ज्यामिति का उपयोग करने के लिए भयंकर प्रतिस्पर्धा है। इन वर्षों में, ट्रांजिस्टर का आकार 1970 के दशक की शुरुआत में दसियों माइक्रोन से घटकर 2017 में 10 नैनोमीटर हो गया है रेफरी>{{Cite web|url=https://news.samsung.com/global/qualcomm-and-samsung-collaborate-on-10nm-process-technology-for-the-latest-snapdragon-835-mobile-processor|title=Qualcomm and Samsung Collaborate on 10nm Process Technology for the Latest Snapdragon 835 Mobile Processor|website=news.samsung.com|access-date=2017-02-11}}</ref> प्रति यूनिट क्षेत्र में ट्रांजिस्टरों में एक लाख गुना वृद्धि के साथ। 2016 तक, विशिष्ट चिप क्षेत्र कुछ वर्ग मिलीमीटर से लेकर लगभग 600 मिमी . तक होते हैं<sup>2</sup>, प्रति मिमी . 25 मिलियन तक ट्रांजिस्टर के साथ<sup>2</सुप>.<ref name=Pascal>{{cite web |url=https://devblogs.nvidia.com/parallelforall/inside-pascal/ |title=Inside Pascal: NVIDIA's Newest Computing Platform|date=2016-04-05}}. 15,300,000,000 transistors in 610 mm<sup>2</sup>.</ref> | |||

फीचर साइज में अपेक्षित सिकुड़न और संबंधित क्षेत्रों में आवश्यक प्रगति का अनुमान इंटरनेशनल टेक्नोलॉजी रोडमैप फॉर सेमीकंडक्टर्स (ITRS) द्वारा कई वर्षों से लगाया गया था। अंतिम आईटीआरएस 2016 में जारी किया गया था, और इसे उपकरणों और प्रणालियों के लिए अंतर्राष्ट्रीय रोडमैप द्वारा प्रतिस्थापित किया जा रहा है।<ref>{{cite web |title=International Roadmap for Devices and Systems |publisher=IEEE |year=2016 |url=http://rebootingcomputing.ieee.org/images/files/pdf/rc_irds.pdf}}</ref> | |||

प्रारंभ में, | प्रारंभ में, IC सख्ती से इलेक्ट्रॉनिक उपकरण थे। छोटे आकार और कम लागत के समान लाभ प्राप्त करने के प्रयास में आईसी की सफलता ने अन्य प्रौद्योगिकियों के एकीकरण को प्रेरित किया है। इन तकनीकों में यांत्रिक उपकरण, प्रकाशिकी और सेंसर शामिल हैं। | ||

* चार्ज-युग्मित डिवाइस, और | * चार्ज-युग्मित डिवाइस, और निकट से संबंधित सक्रिय-पिक्सेल सेंसर, ऐसे चिप्स हैं जो प्रकाश के प्रति संवेदनशील होते हैं। उन्होंने बड़े पैमाने पर वैज्ञानिक, चिकित्सा और उपभोक्ता अनुप्रयोगों में फोटोग्राफिक फिल्म को बदल दिया है। इन उपकरणों के अरबों अब हर साल सेलफोन, टैबलेट और डिजिटल कैमरों जैसे अनुप्रयोगों के लिए उत्पादित किए जाते हैं। आईसी के इस उप-क्षेत्र ने 2009 में नोबेल पुरस्कार जीता।<ref name= CcdNobel >{{citation | title = The Nobel Prize in Physics 2009 | url = http://nobelprize.org/nobel_prizes/physics/laureates/2009/index.html | publisher = Nobel Foundation | date = 2009-10-06 | access-date = 2009-10-06}}.</ref> | ||

* बिजली द्वारा संचालित बहुत छोटे यांत्रिक उपकरणों को चिप्स पर एकीकृत किया जा सकता है, एक तकनीक जिसे माइक्रोइलेक्ट्रोमैकेनिकल सिस्टम के रूप में जाना जाता | * बिजली द्वारा संचालित बहुत छोटे यांत्रिक उपकरणों को चिप्स पर एकीकृत किया जा सकता है, एक तकनीक जिसे माइक्रोइलेक्ट्रोमैकेनिकल सिस्टम के रूप में जाना जाता है। इन उपकरणों को 1980 के दशक के अंत में विकसित किया गया था<ref>{{cite conference |title=A decade of MEMS and its future |author=Fujita, H. |conference= Tenth Annual International Workshop on Micro Electro Mechanical Systems |year=1997 |doi=10.1109/MEMSYS.1997.581729 }}</ref> और विभिन्न प्रकार के वाणिज्यिक और सैन्य अनुप्रयोगों में उपयोग किया जाता है। उदाहरणों में डीएलपी प्रोजेक्टर, इंकजेट प्रिंटर, और एक्सेलेरोमीटर और एमईएमएस गायरोस्कोप शामिल हैं जिनका उपयोग ऑटोमोबाइल एयरबैग को तैनात करने के लिए किया जाता है। | ||

* 2000 के दशक की शुरुआत से, सिलिकॉन चिप्स में ऑप्टिकल कार्यक्षमता (ऑप्टिकल कंप्यूटिंग) के एकीकरण को अकादमिक अनुसंधान और उद्योग दोनों में सक्रिय रूप से आगे बढ़ाया गया है, जिसके परिणामस्वरूप ऑप्टिकल उपकरणों (मॉड्यूलेटर, डिटेक्टर, रूटिंग) के संयोजन वाले सिलिकॉन आधारित एकीकृत ऑप्टिकल ट्रांसीवर का सफल व्यावसायीकरण हुआ है। CMOS आधारित इलेक्ट्रॉनिक्स के साथ।<ref>{{cite journal|author = Narasimha, A. |title = A 40-Gb/s QSFP optoelectronic transceiver in a 0.13 µm CMOS silicon-on-insulator technology|year = 2008|journal = Proceedings of the Optical Fiber Communication Conference (OFC)|page = OMK7|url=http://www.opticsinfobase.org/abstract.cfm?URI=OFC-2008-OMK7|display-authors=etal}}</ref> प्रकाश का उपयोग करने वाले फोटोनिक एकीकृत परिपथों को भी विकसित किया जा रहा है, जो भौतिकी के उभरते हुए क्षेत्र का उपयोग करके फोटोनिक्स के रूप में जाना जाता है। | |||

* | * इम्प्लांट (दवा) या अन्य बायोइलेक्ट्रॉनिक उपकरणों में सेंसर अनुप्रयोगों के लिए एकीकृत सर्किट भी विकसित किए जा रहे हैं।<ref name= Birkholz2015>{{cite journal | url = https://www.researchgate.net/publication/282052331 | title = Technology modules from micro- and nano-electronics for the life sciences | journal = WIREs Nanomed. Nanobiotech. | volume = 8 |issue=3 | pages = 355–377 | year = 2016 | doi = 10.1002/wnan.1367 |pmid=26391194 | last1 = Birkholz | first1 = M. | last2 = Mai | first2 = A. | last3 = Wenger | first3 = C. | last4 = Meliani | first4 = C. | last5 = Scholz | first5 = R. }}</ref> ऐसे बायोजेनिक वातावरण में विशेष सीलिंग तकनीकों को लागू किया जाना चाहिए ताकि उजागर अर्धचालक पदार्थों के क्षरण या बायोडिग्रेडेशन से बचा जा सके।<ref name="Graham2011">{{cite journal | title = Commercialisation of CMOS Integrated Circuit Technology in Multi-Electrode Arrays for Neuroscience and Cell-Based Biosensors | journal = Sensors | volume = 11 |issue=5 | pages = 4943–4971 | year = 2011 | doi = 10.3390/s110504943 |pmid=22163884 |pmc=3231360 | last1 = Graham | first1 = Anthony H. D. | last2 = Robbins | first2 = Jon | last3 = Bowen | first3 = Chris R. | last4 = Taylor | first4 = John | bibcode = 2011Senso..11.4943G | doi-access = free }}</ref> | ||

{{As of|2018}}, सभी ट्रांजिस्टर के विशाल बहुमत एक फ्लैट दो-आयामी प्लानर प्रक्रिया में सिलिकॉन की चिप के एक तरफ एक | {{As of|2018}}, सभी ट्रांजिस्टर के विशाल बहुमत MOSFETs हैं जो एक फ्लैट दो-आयामी प्लानर प्रक्रिया में सिलिकॉन की एक चिप के एक तरफ एक परत में निर्मित होते हैं। शोधकर्ताओं ने कई आशाजनक विकल्पों के प्रोटोटाइप तैयार किए हैं, जैसे: | ||

* | * त्रि-आयामी एकीकृत सर्किट (3DIC) बनाने के लिए ट्रांजिस्टर की कई परतों को ढेर करने के लिए विभिन्न दृष्टिकोण, जैसे कि थ्रू-सिलिकॉन थ्रू, मोनोलिथिक 3D,<ref>Or-Bach, Zvi (December 23, 2013). [http://semimd.com/blog/2013/12/23/why-soi-is-the-future-technology-of-semiconductors/ "Why SOI is the Future Technology of Semiconductors"]. semimd.com {{Webarchive|url=https://web.archive.org/web/20141129104851/http://semimd.com/blog/2013/12/23/why-soi-is-the-future-technology-of-semiconductors/ |date=29 November 2014 }}. | ||

2013.</ref> स्टैक्ड वायर बॉन्डिंग,<ref> | 2013.</ref> स्टैक्ड वायर बॉन्डिंग,<ref> | ||

[https://sst.semiconductor-digest.com/chipworks_real_chips_blog/2010/09/13/samsungs-eight-stack-flash-shows-up-in-apples-iphone-4/ "Samsung’s Eight-Stack Flash Shows up in Apple’s iPhone 4"]. sst.semiconductor-digest.com. | [https://sst.semiconductor-digest.com/chipworks_real_chips_blog/2010/09/13/samsungs-eight-stack-flash-shows-up-in-apples-iphone-4/ "Samsung’s Eight-Stack Flash Shows up in Apple’s iPhone 4"]. sst.semiconductor-digest.com. | ||

September 13, 2010.</ref> और अन्य | September 13, 2010.</ref> और अन्य तरीके। | ||

* अन्य सामग्रियों से निर्मित ट्रांजिस्टर: | * अन्य सामग्रियों से निर्मित ट्रांजिस्टर: ग्रेफीन ट्रांजिस्टर, मोलिब्डेनाइट#सेमीकंडक्टर, कार्बन नैनोट्यूब फील्ड-इफेक्ट ट्रांजिस्टर, गैलियम नाइट्राइड ट्रांजिस्टर, ट्रांजिस्टर जैसे नैनोवायर#इलेक्ट्रॉनिक उपकरण, ऑर्गेनिक फील्ड-इफेक्ट ट्रांजिस्टर, आदि। | ||

* सिलिकॉन के एक छोटे से गोले की पूरी सतह पर ट्रांजिस्टर | * सिलिकॉन के एक छोटे से गोले की पूरी सतह पर ट्रांजिस्टर बनाना।<ref>{{cite journal|url=http://www.natureinterface.com/e/ni07/P058-059/|title=Spherical semiconductor radio temperature sensor|journal=Nature Interface|year=2002|pages=58–59|volume=7|author=Yamatake Corporation|archive-url=https://web.archive.org/web/20090107144008/http://www.natureinterface.com/e/ni07/P058-059/|archive-date=7 January 2009}}</ref><ref> | ||

{{Citation | {{Citation | ||

| last = Takeda | | last = Takeda | ||

| Line 80: | Line 80: | ||

}} | }} | ||

</ref> | </ref> | ||

* सब्सट्रेट | * सब्सट्रेट में संशोधन, आमतौर पर ट्रांजिस्टर बनाने के लिए#लचीले प्रदर्शन या अन्य लचीले इलेक्ट्रॉनिक्स के लिए लचीले ट्रांजिस्टर, संभवतः एक रोल-अवे कंप्यूटर की ओर ले जाते हैं। | ||

जैसा कि कभी छोटे ट्रांजिस्टर का निर्माण करना अधिक कठिन हो जाता है, कंपनियां मल्टी-चिप मॉड्यूल, | जैसा कि कभी छोटे ट्रांजिस्टर का निर्माण करना अधिक कठिन हो जाता है, कंपनियां मल्टी-चिप मॉड्यूल, त्रि-आयामी एकीकृत सर्किट, पैकेज पर पैकेज, उच्च बैंडविड्थ मेमोरी और थ्रू-सिलिकॉन विअस का उपयोग प्रदर्शन को बढ़ाने और आकार को कम करने के लिए कर रही हैं। ट्रांजिस्टर के आकार को कम करें। ऐसी तकनीकों को सामूहिक रूप से उन्नत पैकेजिंग के रूप में जाना जाता है।<ref>{{Cite web|url=https://semiengineering.com/knowledge_centers/packaging/advanced-packaging/|title=Advanced Packaging}}</ref> उन्नत पैकेजिंग को मुख्य रूप से 2.5D और 3D पैकेजिंग में विभाजित किया गया है। 2.5D मल्टी-चिप मॉड्यूल जैसे दृष्टिकोणों का वर्णन करता है जबकि 3D उन दृष्टिकोणों का वर्णन करता है जहां एक तरह से या किसी अन्य तरीके से ढेर हो जाते हैं, जैसे पैकेज पर पैकेज और उच्च बैंडविड्थ मेमोरी। सभी दृष्टिकोणों में एक पैकेज में 2 या अधिक मर जाते हैं।<ref>{{Cite web|url=https://semiengineering.com/knowledge_centers/packaging/advanced-packaging/2-5d-ic/|title=2.5D|work=Semiconductor Engineering}}</ref><ref>{{Cite web|url=https://semiengineering.com/knowledge_centers/packaging/advanced-packaging/3d-ics/|title=3D ICs|work=Semiconductor Engineering}}</ref><ref>[https://en.wikichip.org/wiki/chiplet Wikichip (2018) Chiplet]. wikichip.org cites IEDM 2017, Dr. Lisa Su accessdate=2019-05-26</ref><ref>{{Cite magazine|url=https://www.wired.com/story/keep-pace-moores-law-chipmakers-turn-chiplets/|title=To Keep Pace With Moore's Law, Chipmakers Turn to 'Chiplets'|magazine=Wired|date=11 June 2018}}</ref><ref>Schodt, Christopher (April 16, 2019) [https://www.engadget.com/2019/04/16/upscaled-cpu-chiplet/ Upscaled: This is the year of the CPU ‘chiplet’]. ''End Gadget''</ref> वैकल्पिक रूप से, 3D NAND जैसे दृष्टिकोण एक ही डाई पर कई परतों को ढेर कर देते हैं। | ||

== डिजाइन == | == डिजाइन == | ||

{{main|Electronic design automation|Hardware description language|Integrated circuit design}} | {{main|Electronic design automation|Hardware description language|Integrated circuit design}} | ||

एक जटिल एकीकृत सर्किट को | एकीकृत सर्किट डिजाइन और एक जटिल एकीकृत सर्किट को विकसित करने की लागत काफी अधिक है, आमतौर पर कई दसियों मिलियन डॉलर में।<ref>{{cite web |title=FinFET Rollout Slower Than Expected |url=http://semiengineering.com/finfet-rollout-slower-than-expected/ |publisher=Semiconductor Engineering |date=16 April 2015 |author=LaPedus, Mark }}</ref><ref>{{Cite journal|last=Basu|first=Joydeep|date=2019-10-09|title=From Design to Tape-out in SCL 180 nm CMOS Integrated Circuit Fabrication Technology|journal=IETE Journal of Education|volume=60|issue=2|pages=51–64|doi=10.1080/09747338.2019.1657787|arxiv=1908.10674|s2cid=201657819}}</ref> इसलिए, यह केवल उच्च उत्पादन मात्रा के साथ एकीकृत सर्किट उत्पादों का उत्पादन करने के लिए आर्थिक समझ में आता है, इसलिए गैर-आवर्ती इंजीनियरिंग (एनआरई) लागत आम तौर पर लाखों उत्पादन इकाइयों में फैली हुई है। | ||

आधुनिक | आधुनिक सेमीकंडक्टर चिप्स में अरबों घटक होते हैं, और हाथ से डिज़ाइन किए जाने के लिए बहुत जटिल होते हैं। डिज़ाइनर की सहायता के लिए सॉफ़्टवेयर उपकरण आवश्यक हैं। इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन (EDA), जिसे इलेक्ट्रॉनिक कंप्यूटर एडेड डिज़ाइन | कंप्यूटर एडेड डिज़ाइन (ECAD) भी कहा जाता है,<ref>{{cite web|title=About the EDA Industry|url=http://www.edac.org/industry|publisher=[[Electronic Design Automation Consortium]]|access-date=29 July 2015|url-status=dead|archive-url=https://web.archive.org/web/20150802073506/http://www.edac.org/industry|archive-date=2 August 2015}}</ref> एकीकृत सर्किट सहित इलेक्ट्रॉनिक्स डिजाइन करने के लिए सॉफ्टवेयर टूल्स की एक श्रेणी है। उपकरण एक डिजाइन प्रवाह (ईडीए) में एक साथ काम करते हैं जो इंजीनियर पूरे अर्धचालक चिप्स को डिजाइन और विश्लेषण करने के लिए उपयोग करते हैं। | ||

== प्रकार == | == प्रकार == | ||

[[File:AD570JD.jpg|thumb| | [[File:AD570JD.jpg|thumb|दोहरी इन-लाइन पैकेज में ए-टू-डी कनवर्टर आईसी]] | ||

इंटीग्रेटेड सर्किट को मोटे तौर पर एनालॉग सर्किट में वर्गीकृत किया जा सकता है,<ref>{{cite book |title=Analysis and Design of Analog Integrated Circuits |author1=Gray, Paul R. |author2=Hurst, Paul J. |author3=Lewis, Stephen H. |author4=Meyer, Robert G. |isbn=978-0-470-24599-6 |publisher=Wiley |year=2009 }}</ref> डिजिटल सर्किट<ref>{{cite book |title=Digital Integrated Circuits |author1=Rabaey, Jan M. |author2=Chandrakasan, Anantha |author3=Nikolic, Borivoje |isbn=978-0-13-090996-1 |publisher=Pearson |year=2003 |url=https://archive.org/details/agilesoftwaredev00robe |edition=2nd }}</ref> और मिश्रित-संकेत एकीकृत परिपथ,<ref>{{cite book |title=CMOS: Mixed-Signal Circuit Design |author=Baker, Jacob |publisher=Wiley |isbn=978-0-470-29026-2 |year=2008}}</ref> एक ही आईसी पर एनालॉग और डिजिटल सिग्नलिंग से मिलकर। | |||

डिजिटल एकीकृत सर्किट में अरबों हो सकते हैं<ref name=Pascal/>लॉजिक गेट्स, फ्लिप-फ्लॉप (इलेक्ट्रॉनिक्स) | | डिजिटल एकीकृत सर्किट में अरबों हो सकते हैं<ref name=Pascal/>लॉजिक गेट्स, फ्लिप-फ्लॉप (इलेक्ट्रॉनिक्स) | फ्लिप-फ्लॉप, मल्टीप्लेक्सर्स, और अन्य सर्किट कुछ वर्ग मिलीमीटर में। इन सर्किटों का छोटा आकार बोर्ड-स्तरीय एकीकरण की तुलना में उच्च गति, कम बिजली अपव्यय और कम विनिर्माण लागत की अनुमति देता है। ये डिजिटल आईसी, आमतौर पर माइक्रोप्रोसेसर, डिजिटल सिग्नल प्रोसेसर और माइक्रोकंट्रोलर, बाइनरी नंबर को संसाधित करने के लिए बूलियन बीजगणित का उपयोग करते हैं। एक और शून्य संकेत। | ||

[[File:Intel 8742 153056995.jpg|right|thumb|एक | [[File:Intel 8742 153056995.jpg|right|thumb|एक Intel Intel MCS-48 से डाई (एकीकृत सर्किट), एक 8-बिट NMOS लॉजिक माइक्रोकंट्रोलर जिसमें 12 मेगाहर्ट्ज पर चलने वाला CPU, 128 बाइट्स RAM, EPROM के 2048 बाइट्स और इनपुट/आउटपुट|I/O शामिल हैं। एक ही चिप]] | ||

सबसे उन्नत एकीकृत | सबसे उन्नत एकीकृत परिपथों में माइक्रोप्रोसेसर या प्रोसेसर कोर हैं, जिनका उपयोग पर्सनल कंप्यूटर, सेल-फोन, माइक्रोवेव ओवन आदि में किया जाता है। कई कोर को एक आईसी या चिप में एक साथ एकीकृत किया जा सकता है। डिजिटल कंप्यूटर मेमोरी और एप्लिकेशन-विशिष्ट एकीकृत सर्किट (एएसआईसी) एकीकृत सर्किट के अन्य परिवारों के उदाहरण हैं। | ||

1980 के दशक में, | 1980 के दशक में, प्रोग्राम करने योग्य लॉजिक डिवाइस विकसित किए गए थे। इन उपकरणों में सर्किट होते हैं जिनके तार्किक कार्य और कनेक्टिविटी को एकीकृत सर्किट निर्माता द्वारा तय किए जाने के बजाय उपयोगकर्ता द्वारा प्रोग्राम किया जा सकता है। यह एक चिप को विभिन्न एलएसआई-प्रकार के कार्यों जैसे लॉजिक गेट्स, योजक (इलेक्ट्रॉनिक्स) और प्रोसेसर रजिस्टर करने के लिए प्रोग्राम करने की अनुमति देता है। प्रोग्राममेबिलिटी विभिन्न रूपों में आती है - डिवाइस जो प्रोग्रामेबल रीड-ओनली मेमोरी हो सकते हैं, वे डिवाइस जिन्हें मिटाया जा सकता है और फिर ईपीरोम को फिर से प्रोग्राम किया जा सकता है, वे डिवाइस जिन्हें फ्लैश मेमोरी का उपयोग करके (पुनः) प्रोग्राम किया जा सकता है, और फील्ड-प्रोग्रामेबल गेट एरेज़ (एफपीजीए) जो ऑपरेशन के दौरान सहित किसी भी समय प्रोग्राम किया जा सकता है। वर्तमान FPGAs (2016 तक) लाखों गेटों के बराबर लागू कर सकते हैं और 1 हर्ट्ज़ तक की घड़ी की दर से काम कर सकते हैं।<ref name="Altera">{{cite news | ||

|url = https://www.altera.com/en_US/pdfs/literature/hb/stratix-10/s10-overview.pdf | |url = https://www.altera.com/en_US/pdfs/literature/hb/stratix-10/s10-overview.pdf | ||

|title = Stratix 10 Device Overview | |title = Stratix 10 Device Overview | ||

| Line 105: | Line 105: | ||

|date = 12 December 2015 | |date = 12 December 2015 | ||

}}</ref> | }}</ref> | ||

एनालॉग आईसी, जैसे सेंसर, पावर | एनालॉग आईसी, जैसे सेंसर, पावर नेटवर्क डिज़ाइन (आईसी), और ऑपरेशनल एम्पलीफायर्स (ऑप-एम्प्स), निरंतर संकेतों को संसाधित करते हैं, और एम्पलीफायर, सक्रिय फ़िल्टरिंग, डिमॉड्यूलेशन और फ़्रिक्वेंसी मिक्सर जैसे एनालॉग फ़ंक्शन करते हैं। | ||

IC एनालॉग-टू-डिजिटल कन्वर्टर्स और डिजिटल-टू-एनालॉग कन्वर्टर्स जैसे फ़ंक्शन बनाने के लिए एक चिप पर एनालॉग और डिजिटल सर्किट को जोड़ सकते हैं। ऐसे मिश्रित सिग्नल सर्किट छोटे आकार और कम लागत की पेशकश करते हैं, लेकिन सिग्नल हस्तक्षेप के लिए जिम्मेदार होना चाहिए। 1990 के दशक के उत्तरार्ध से पहले, माइक्रोप्रोसेसरों के समान कम लागत वाली CMOS प्रक्रियाओं में रेडियो का निर्माण नहीं किया जा सकता था। लेकिन 1998 से, RF CMOS प्रक्रियाओं का उपयोग करके रेडियो चिप्स विकसित किए गए हैं। उदाहरणों में इंटेल का डिजिटल एन्हांस्ड कॉर्डलेस टेलीकम्युनिकेशंस कॉर्डलेस फोन, या एथेरोस और अन्य कंपनियों द्वारा बनाए गए 802.11 (वाई-फाई) चिप्स शामिल हैं।<ref name="IEEE-CMOS-dualband-n">{{cite web|last1=Nathawad|first1=L.|last2=Zargari|first2=M.|last3=Samavati|first3=H.|last4=Mehta|first4=S.|last5=Kheirkhaki|first5=A.|last6=Chen|first6=P.|last7=Gong|first7=K.|last8=Vakili-Amini|first8=B.|last9=Hwang|first9=J.|last10=Chen|first10=M.|last11=Terrovitis|first11=M.|last12=Kaczynski|first12=B.|last13=Limotyrakis|first13=S.|last14=Mack|first14=M.|last15=Gan|first15=H.|last16=Lee|first16=M.|last17=Abdollahi-Alibeik|first17=B.|last18=Baytekin|first18=B.|last19=Onodera|first19=K.|last20=Mendis|first20=S.|last21=Chang|first21=A.|last22=Jen|first22=S.|last23=Su|first23=D.|last24=Wooley|first24=B.|title=20.2: A Dual-band CMOS MIMO Radio SoC for IEEE 802.11n Wireless LAN|url=http://www.ewh.ieee.org/r6/scv/ssc/May2008_WLAN.pdf|website=IEEE Entity Web Hosting|publisher=IEEE|access-date=22 October 2016}}</ref> | |||

आधुनिक: श्रेणी: | आधुनिक: श्रेणी: इलेक्ट्रॉनिक घटक वितरक अक्सर एकीकृत परिपथों को उप-वर्गीकृत करते हैं: | ||

* डिजिटल | * डिजिटल इंटीग्रेटेड सर्किट को लॉजिक IC (जैसे माइक्रोप्रोसेसर और माइक्रोकंट्रोलर), मेमोरी चिप्स (जैसे MOS मेमोरी और फ्लोटिंग-गेट मेमोरी), इंटरफ़ेस IC (लॉजिक लेवल, सीरियलाइज़र / डिसेरिएलाइज़र, आदि), पावर मैनेजमेंट IC, और के रूप में वर्गीकृत किया जाता है। प्रोग्रामेबल लॉजिक डिवाइस। | ||

* एनालॉग | * एनालॉग एकीकृत सर्किट को रैखिक एकीकृत सर्किट और आरएफ सर्किट (रेडियो आवृत्ति सर्किट) के रूप में वर्गीकृत किया जाता है। | ||

* | * मिक्स्ड-सिग्नल इंटीग्रेटेड सर्किट को डेटा अधिग्रहण आईसी (ए/डी कन्वर्टर्स, डी/ए कन्वर्टर्स, डिजिटल पोटेंशियोमीटर सहित), क्लॉक जेनरेटर | क्लॉक/टाइमिंग आईसी, स्विच्ड कैपेसिटर (एससी) सर्किट और आरएफ सीएमओएस सर्किट के रूप में वर्गीकृत किया गया है। | ||

* त्रि-आयामी एकीकृत सर्किट ( | * त्रि-आयामी एकीकृत सर्किट (3D IC) को थ्रू-सिलिकॉन (TSV) IC और Cu-Cu कनेक्शन IC के माध्यम से वर्गीकृत किया गया है। | ||

== | == निर्माण == | ||

{{refimprove|section|date=May 2022}} | {{refimprove|section|date=May 2022}} | ||

| Line 120: | Line 120: | ||

=== निर्माण === | === निर्माण === | ||

{{Main|Semiconductor device fabrication|l1=Semiconductor fabrication}} | {{Main|Semiconductor device fabrication|l1=Semiconductor fabrication}} | ||

[[File:Silicon chip 3d.png|right|thumb|तीन धातु परतों के साथ एक छोटे मानक सेल का प्रतिपादन (ढांकता हुआ हटा दिया गया है) | [[File:Silicon chip 3d.png|right|thumb|तीन धातु परतों के साथ एक छोटे मानक सेल का प्रतिपादन (ढांकता हुआ हटा दिया गया है)। रेत के रंग की संरचनाएं धातु इंटरकनेक्ट (एकीकृत सर्किट) हैं, जिसमें ऊर्ध्वाधर खंभे संपर्क होते हैं, आमतौर पर टंगस्टन के प्लग होते हैं। लाल रंग की संरचनाएं पॉलीसिलिकॉन गेट हैं, और तल पर ठोस मोनोक्रिस्टलाइन सिलिकॉन बल्क है।]] | ||

[[File:Cmos-chip structure in 2000s (en).svg|right|thumb| | [[File:Cmos-chip structure in 2000s (en).svg|right|thumb|सीएमओएस चिप की योजनाबद्ध संरचना, जैसा कि 2000 के दशक की शुरुआत में बनाया गया था। ग्राफिक एलडीडी-एमआईएसएफईटी को एसओआई सब्सट्रेट पर पांच धातुकरण परतों और फ्लिप-चिप बॉन्डिंग के लिए सोल्डर बंप के साथ दिखाता है। यह FEOL (लाइन का फ्रंट-एंड), BEOL (लाइन का बैक-एंड) और बैक-एंड प्रक्रिया के पहले भाग के लिए अनुभाग भी दिखाता है।]] | ||

रासायनिक तत्वों की आवर्त सारणी के | रासायनिक तत्वों की आवर्त सारणी के अर्धचालकों को सॉलिड-स्टेट इलेक्ट्रॉनिक्स | सॉलिड-स्टेट वैक्यूम ट्यूब के लिए सबसे संभावित सामग्री के रूप में पहचाना गया। कॉपर (I) ऑक्साइड से शुरू होकर, जर्मेनियम, फिर सिलिकॉन तक, सामग्री का व्यवस्थित रूप से 1940 और 1950 के दशक में अध्ययन किया गया था। आज, मोनोक्रिस्टलाइन सिलिकॉन आईसी के लिए उपयोग किया जाने वाला मुख्य सब्सट्रेट (प्रिंटिंग) है, हालांकि कुछ III-V यौगिक अर्धचालक जैसे गैलियम आर्सेनाइड का उपयोग प्रकाश उत्सर्जक डायोड, लेजर, सौर कोशिकाओं और उच्चतम गति एकीकृत सर्किट जैसे विशेष अनुप्रयोगों के लिए किया जाता है। अर्धचालक सामग्री की क्रिस्टल संरचना में न्यूनतम क्रिस्टल दोषों के साथ क्रिस्टल बनाने के सही तरीकों में दशकों लग गए। | ||

सेमीकंडक्टर आईसी एक प्लानर प्रक्रिया में | सेमीकंडक्टर आईसी एक प्लानर प्रक्रिया में निर्मित होते हैं जिसमें तीन प्रमुख प्रक्रिया चरण शामिल होते हैं{{snd}} फोटोलिथोग्राफी, बयान (जैसे रासायनिक वाष्प जमाव), और नक़्क़ाशी (माइक्रोफैब्रिकेशन)। मुख्य प्रक्रिया कदम डोपिंग और सफाई द्वारा पूरक हैं। अधिक हाल के या उच्च-प्रदर्शन वाले आईसी इसके बजाय मल्टीगेट डिवाइस का उपयोग कर सकते हैं|प्लानर वाले के बजाय मल्टी-गेट फिनफेट या जीएएएफईटी ट्रांजिस्टर, 22 एनएम नोड (इंटेल) या 16/14 एनएम नोड्स से शुरू होते हैं।<ref>Hsu, Chi-Ping (January 17, 2013). [https://www.electronicdesign.com/technologies/digital-ics/article/21795644/16nm14nm-finfets-enabling-the-new-electronics-frontier 16nm/14nm FinFETs: Enabling The New Electronics Frontier]. ''Electronic Design''</ref> | ||

मोनो-क्रिस्टल सिलिकॉन | मोनोक्रिस्टलाइन सिलिकॉन|मोनो-क्रिस्टल सिलिकॉन वेफर (इलेक्ट्रॉनिक्स) का उपयोग अधिकांश अनुप्रयोगों में किया जाता है (या विशेष अनुप्रयोगों के लिए, अन्य अर्धचालक जैसे गैलियम आर्सेनाइड का उपयोग किया जाता है)। वेफर पूरी तरह से सिलिकॉन नहीं होना चाहिए। फोटोलिथोग्राफी का उपयोग सब्सट्रेट के विभिन्न क्षेत्रों को डोपिंग (सेमीकंडक्टर) के रूप में चिह्नित करने के लिए किया जाता है या उन पर पॉलीसिलिकॉन, इंसुलेटर या धातु (आमतौर पर एल्यूमीनियम या तांबा) ट्रैक जमा करने के लिए किया जाता है। डोपेंट अशुद्धियाँ हैं जो जानबूझकर अर्धचालक को उसके इलेक्ट्रॉनिक गुणों को संशोधित करने के लिए पेश की जाती हैं। डोपिंग एक अर्धचालक पदार्थ में डोपेंट जोड़ने की प्रक्रिया है। | ||

{{anchor|circuitLayers}} * एकीकृत सर्किट कई अतिव्यापी परतों से बने होते हैं, प्रत्येक फोटोलिथोग्राफी द्वारा परिभाषित किया जाता है, और सामान्य रूप से विभिन्न रंगों में दिखाया | {{anchor|circuitLayers}} * एकीकृत सर्किट कई अतिव्यापी परतों से बने होते हैं, प्रत्येक को फोटोलिथोग्राफी द्वारा परिभाषित किया जाता है, और सामान्य रूप से विभिन्न रंगों में दिखाया जाता है। कुछ परतें चिह्नित करती हैं जहां विभिन्न डोपेंट सब्सट्रेट (डिफ्यूजन लेयर्स कहा जाता है) में विसरित होते हैं, कुछ परिभाषित करते हैं कि अतिरिक्त आयन कहाँ लगाए जाते हैं (प्रत्यारोपण परतें), कुछ कंडक्टर (डॉप्ड पॉलीसिलिकॉन या धातु की परतें) को परिभाषित करते हैं, और कुछ संवाहक परतों के बीच कनेक्शन को परिभाषित करते हैं। (के माध्यम से या संपर्क परतों)। सभी घटकों का निर्माण इन परतों के एक विशिष्ट संयोजन से किया जाता है। | ||

* एक स्व-संरेखित सीएमओएस प्रक्रिया में, एक ट्रांजिस्टर | * एक स्व-संरेखित सीएमओएस प्रक्रिया में, एक ट्रांजिस्टर बनता है जहां गेट परत (पॉलीसिलिकॉन या धातु) सीएमओएस # उदाहरण: भौतिक लेआउट में नंद गेट एक प्रसार परत।<ref name= selfAlignedCmos >[[Carver Mead|Mead, Carver A.]]; [[Lynn Conway|Conway, Lynn]] (1980) ''[[Introduction to VLSI Systems]]'' Reading, Mass.: Addison-Wesley: ISBN 2-201-04358-0</ref>{{rp|p.1 (see Fig. 1.1)}} | ||

* | * संधारित्र, एक पारंपरिक विद्युत संधारित्र के समानांतर-प्लेट संधारित्र के रूप में, प्लेटों के बीच इन्सुलेट सामग्री के साथ, प्लेटों के क्षेत्र के अनुसार बनते हैं। आकार की एक विस्तृत श्रृंखला के कैपेसिटर IC पर आम हैं। | ||

* अलग-अलग लंबाई की धारियों | * अलग-अलग लंबाई की घुमावदार धारियों का उपयोग कभी-कभी ऑन-चिप प्रतिरोधक बनाने के लिए किया जाता है, हालांकि अधिकांश लॉजिक सर्किट को किसी भी प्रतिरोधक की आवश्यकता नहीं होती है। प्रतिरोधक संरचना की लंबाई और इसकी चौड़ाई का अनुपात, इसकी शीट प्रतिरोधकता के साथ मिलकर, प्रतिरोध को निर्धारित करता है। | ||

* | * शायद ही कभी, प्रारंभ करनेवाला को छोटे ऑन-चिप कॉइल के रूप में बनाया जा सकता है, या गाइरेटर्स द्वारा सिम्युलेटेड किया जा सकता है। | ||

चूंकि एक | चूंकि एक सीएमओएस डिवाइस केवल बूलियन बीजगणित (लॉजिक) स्टेट (कंप्यूटर साइंस) के बीच स्टेट ट्रांजिशन फंक्शन पर करंट खींचता है, सीएमओएस डिवाइस बाइपोलर जंक्शन ट्रांजिस्टर डिवाइस की तुलना में बहुत कम करंट की खपत करते हैं। | ||

रैंडम-एक्सेस मेमोरी इंटीग्रेटेड सर्किट का सबसे नियमित प्रकार है; उच्चतम घनत्व वाले उपकरण इस प्रकार यादें हैं; लेकिन एक माइक्रोप्रोसेसर में भी चिप पर मेमोरी होगी। (पहली छवि के नीचे नियमित सरणी संरचना देखें।{{Which|date=October 2018}}) हालांकि संरचनाएं जटिल हैं - चौड़ाई के साथ जो दशकों से सिकुड़ रही हैं - परतें डिवाइस की चौड़ाई की तुलना में बहुत पतली रहती हैं। सामग्री की परतें एक फोटोग्राफिक प्रक्रिया की तरह गढ़ी जाती हैं, हालांकि दृश्य स्पेक्ट्रम में प्रकाश तरंगों का उपयोग सामग्री की एक परत को उजागर करने के लिए नहीं किया जा सकता है, क्योंकि वे सुविधाओं के लिए बहुत बड़े होंगे। इस प्रकार प्रत्येक परत के लिए पैटर्न बनाने के लिए उच्च आवृत्तियों (आमतौर पर पराबैंगनी) के फोटॉन का उपयोग किया जाता है। क्योंकि प्रत्येक सुविधा इतनी छोटी है, एक औद्योगिक प्रक्रिया इंजीनियर के लिए इलेक्ट्रॉन सूक्ष्मदर्शी आवश्यक उपकरण हैं जो एक निर्माण प्रक्रिया को डीबग कर सकते हैं। | |||

वेफर परीक्षण, या वेफर जांच के रूप में जानी जाने वाली प्रक्रिया में स्वचालित परीक्षण उपकरण (एटीई) का उपयोग करके पैकेजिंग से पहले प्रत्येक उपकरण का परीक्षण किया जाता है। फिर वेफर को आयताकार ब्लॉकों में काटा जाता है, जिनमें से प्रत्येक को डाई (एकीकृत सर्किट) कहा जाता है। प्रत्येक अच्छा डाई (बहुवचन पासा, मर जाता है, या मर जाता है) को फिर एल्यूमीनियम (या सोना) वायर बॉन्डिंग का उपयोग करके एक पैकेज में जोड़ा जाता है जो थर्मोसोनिक बॉन्डिंग होते हैं<ref><!-- Coucoulas, A., http://commons.wikimedia.org/wiki/File:Hot_Work_Ultrasonic_(Thermosonic)_Bonding_549-556.pdf DELETED--> [https://sites.google.com/site/hotworkultrasonicbonding/ "Hot Work Ultrasonic Bonding – A Method Of Facilitating Metal Flow By Restoration Processes"], Proc. 20th IEEE Electronic Components Conf. Washington, D.C., May 1970, pp. 549–556.]</ref> पैड के लिए, आमतौर पर मरने के किनारे के आसपास पाया जाता है। थर्मोसोनिक बॉन्डिंग की शुरुआत सबसे पहले ए. कौकुलस ने की थी, जिसने बाहरी दुनिया को इन महत्वपूर्ण विद्युत कनेक्शनों को बनाने का एक विश्वसनीय साधन प्रदान किया। पैकेजिंग के बाद, वेफर जांच के दौरान उपयोग किए जाने वाले समान या समान ATE पर उपकरणों का अंतिम परीक्षण किया जाता है। औद्योगिक सीटी स्कैनिंग का भी उपयोग किया जा सकता है। परीक्षण लागत कम लागत वाले उत्पादों पर निर्माण की लागत का 25% से अधिक हो सकती है, लेकिन कम उपज, बड़े या उच्च लागत वाले उपकरणों पर नगण्य हो सकती है। | |||

{{As of|2016}}, एक | {{As of|2016}}, एक सेमीकंडक्टर फैब्रिकेशन प्लांट (आमतौर पर सेमीकंडक्टर फैब के रूप में जाना जाता है) के निर्माण में 8 बिलियन अमेरिकी डॉलर से अधिक की लागत आ सकती है।<ref>{{cite web |title=How Intel Makes a Chip |date=9 June 2016 |author1=Chafkin, Max |author2=King, Ian |publisher=Bloomburg Businessweek |url=https://www.bloomberg.com/news/articles/2016-06-09/how-intel-makes-a-chip}}</ref> नए उत्पादों की बढ़ती जटिलता के कारण एक निर्माण सुविधा की लागत समय के साथ बढ़ती जाती है; इसे रॉक के नियम के रूप में जाना जाता है। ऐसी सुविधा विशेषताएं: | ||

* 300 | * वेफर (इलेक्ट्रॉनिक्स) 300 मिमी व्यास तक (एक सामान्य प्लेट (डिशवेयर) से अधिक चौड़ा)। | ||

* {{Update inline span|text={{As of|2016}}, 14 nm transistors.<ref>{{cite web |title=10 nm Fab Watch |author=Lapedus, Mark |publisher=Semiconductor Engineering |url=http://semiengineering.com/10nm-fab-watch/ |date=21 May 2015}}</ref>|date=October 2018|reason=In 2018, we see 7 nm and soon expect 5 nm processes}} | * {{Update inline span|text={{As of|2016}}, 14 nm transistors.<ref>{{cite web |title=10 nm Fab Watch |author=Lapedus, Mark |publisher=Semiconductor Engineering |url=http://semiengineering.com/10nm-fab-watch/ |date=21 May 2015}}</ref>|date=October 2018|reason=In 2018, we see 7 nm and soon expect 5 nm processes}} | ||

* कॉपर | * कॉपर इंटरकनेक्ट करता है जहां कॉपर वायरिंग इंटरकनेक्ट के लिए एल्युमीनियम की जगह लेती है। | ||

* कम- | * कम-κ ढांकता हुआ इन्सुलेटर (बिजली)। | ||

* | * इन्सुलेटर पर सिलिकॉन (SOI)। | ||

* आईबीएम द्वारा उपयोग की जाने वाली | * आईबीएम द्वारा उपयोग की जाने वाली प्रक्रिया में स्ट्रेनड सिलिकॉन सीधे इंसुलेटर (एसएसडीओआई) पर स्ट्रेनड सिलिकॉन के रूप में जाना जाता है। | ||

* ट्राई-गेट | * मल्टीगेट डिवाइस जैसे ट्राई-गेट ट्रांजिस्टर। | ||

एकीकृत उपकरण निर्माताओं (आईडीएम) द्वारा या फाउंड्री मॉडल का उपयोग करके आईसी का निर्माण या तो घर में किया जा सकता है। IDM लंबवत रूप से एकीकृत कंपनियाँ (जैसे Intel और Samsung) हैं जो अपने स्वयं के IC का डिज़ाइन, निर्माण और बिक्री करती हैं, और अन्य कंपनियों को डिज़ाइन और/या निर्माण (फाउंड्री) सेवाएँ प्रदान कर सकती हैं (बाद में अक्सर फैबलेस कंपनी को)। फाउंड्री मॉडल में, फैबलेस कंपनियां (जैसे एनवीडिया) केवल आईसी को डिजाइन और बेचती हैं और सभी मैन्युफैक्चरिंग को शुद्ध प्ले # प्योर प्ले फाउंड्री जैसे टीएसएमसी को आउटसोर्स करती हैं। ये फाउंड्री आईसी डिजाइन सेवाएं प्रदान कर सकती हैं। | |||

=== पैकेजिंग === | === पैकेजिंग === | ||

{{Main|Integrated circuit packaging}} | {{Main|Integrated circuit packaging}} | ||

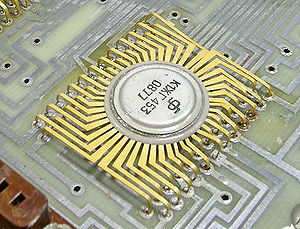

[[File:RUS-IC.JPG|right|thumb|1977 में | [[File:RUS-IC.JPG|right|thumb|1977 में बनी सोवियत एमएसआई एनएमओएस लॉजिक चिप, 1970 में डिज़ाइन किए गए चार-चिप कैलकुलेटर सेट का हिस्सा है<ref>{{cite web | url=http://www.155la3.ru/k145_3.htm#k145hk1 | title = 145 series ICs (in Russian) | access-date=22 April 2012 }}</ref>]] | ||

सबसे पहले एकीकृत सर्किट | सबसे पहले एकीकृत सर्किट सिरेमिक फ्लैटपैक (इलेक्ट्रॉनिक्स) में पैक किए गए थे, जो कि कई वर्षों तक सेना द्वारा उनकी विश्वसनीयता और छोटे आकार के लिए उपयोग किया जाता रहा। वाणिज्यिक सर्किट पैकेजिंग जल्दी से दोहरी इन-लाइन पैकेज (डीआईपी) में चली गई, पहले सिरेमिक में और बाद में प्लास्टिक में, जो आमतौर पर क्रेसोल-फॉर्मेल्डिहाइड-नोवोलैक होता है। 1980 के दशक में वीएलएसआई सर्किट के पिन काउंट डीआईपी पैकेजिंग के लिए व्यावहारिक सीमा से अधिक हो गए, जिससे पिन ग्रिड एरे (पीजीए) और लीडलेस चिप कैरियर (एलसीसी) पैकेज हो गए। सरफेस-माउंट टेक्नोलॉजी पैकेजिंग 1980 के दशक की शुरुआत में दिखाई दी और 1980 के दशक के अंत में लोकप्रिय हो गई, जिसमें गल-विंग या जे-लीड के रूप में बनाई गई लीड के साथ महीन लीड पिच का उपयोग किया गया, जैसा कि स्मॉल आउटलाइन इंटीग्रेटेड सर्किट | स्मॉल-आउटलाइन इंटीग्रेटेड सर्किट ( SOIC) पैकेज - एक वाहक जो एक समकक्ष डीआईपी से लगभग 30-50% कम क्षेत्र पर कब्जा करता है और आमतौर पर 70% पतला होता है। इस पैकेज में दो लंबी भुजाओं से गल विंग लीड उभरी हुई है और 0.050 इंच की लीड स्पेसिंग है। | ||

1990 के दशक के उत्तरार्ध में, | 1990 के दशक के उत्तरार्ध में, PQFP (PQFP) और थिन स्मॉल आउटलाइन पैकेज | थिन स्मॉल-आउटलाइन पैकेज (TSOP) पैकेज हाई पिन काउंट डिवाइस के लिए सबसे आम हो गए, हालांकि PGA पैकेज अभी भी हाई-एंड माइक्रोप्रोसेसर के लिए उपयोग किए जाते हैं। | ||

बॉल ग्रिड | बॉल ग्रिड ऐरे (बीजीए) पैकेज 1970 के दशक से मौजूद हैं। फ्लिप चिप | फ्लिप-चिप बॉल ग्रिड ऐरे पैकेज, जो अन्य पैकेज प्रकारों की तुलना में बहुत अधिक पिन काउंट की अनुमति देते हैं, 1990 के दशक में विकसित किए गए थे। एक FCBGA पैकेज में, डाई को उल्टा (फ़्लिप) लगाया जाता है और पैकेज बॉल्स को एक पैकेज सब्सट्रेट के माध्यम से जोड़ता है जो तारों के बजाय एक मुद्रित-सर्किट बोर्ड के समान होता है। FCBGA पैकेज इनपुट/आउटपुट|इनपुट-आउटपुट सिग्नल (जिन्हें एरिया-I/O कहा जाता है) की एक सरणी को डाई परिधि तक सीमित होने के बजाय पूरे डाई पर वितरित करने की अनुमति देता है। BGA उपकरणों को एक समर्पित सॉकेट की आवश्यकता नहीं होने का लाभ होता है, लेकिन डिवाइस की विफलता के मामले में इसे बदलना बहुत कठिन होता है। | ||

इंटेल | इंटेल पीजीए से लैंड ग्रिड ऐरे (एलजीए) और बीजीए में 2004 में शुरू हुआ, मोबाइल प्लेटफॉर्म के लिए 2014 में जारी आखिरी पीजीए सॉकेट के साथ। {{As of|2018}}, एएमडी मुख्यधारा के डेस्कटॉप प्रोसेसर पर पीजीए पैकेज का उपयोग करता है,<ref>{{Cite news|url=https://wccftech.com/amd-am4-socket-zen-bristol-bridge-soc-package-pictured/|title=AMD Zen CPU & AM4 Socket Pictured, Launching February 2017 – PGA Design With 1331 Pins Confirmed|last=Moammer|first=Khalid|date=2016-09-16|work=Wccftech|access-date=2018-05-20}}</ref> मोबाइल प्रोसेसर पर बीजीए पैकेज,<ref>{{Cite news|url=https://en.wikichip.org/wiki/amd/ryzen_5/2500u|title=Ryzen 5 2500U – AMD – WikiChip|access-date=2018-05-20|publisher=wikichip.org}}</ref> और हाई-एंड डेस्कटॉप और सर्वर माइक्रोप्रोसेसर LGA पैकेज का उपयोग करते हैं।<ref>{{Cite news|url=https://www.pcworld.com/article/3198924/computers/amds-tr4-threadripper-cpu-socket-is-gigantic.html|title=AMD's 'TR4' Threadripper CPU socket is gigantic|work=PCWorld|access-date=2018-05-20|author=Ung, Gordon Mah |date=May 30, 2017}}</ref> | ||

मरने | मरने से निकलने वाले विद्युत संकेतों को मुद्रित सर्किट बोर्ड पर पैकेज को प्रवाहकीय निशान से जोड़ने वाले लीड के माध्यम से, पैकेज में प्रवाहकीय सिग्नल ट्रेस (पथ) के माध्यम से, पैकेज में मरने को विद्युत रूप से जोड़ने वाली सामग्री से गुजरना होगा। इन विद्युत संकेतों के मार्ग में उपयोग की जाने वाली सामग्रियों और संरचनाओं में एक ही मरने के विभिन्न हिस्सों की यात्रा करने वालों की तुलना में बहुत भिन्न विद्युत गुण होते हैं। नतीजतन, उन्हें यह सुनिश्चित करने के लिए विशेष डिजाइन तकनीकों की आवश्यकता होती है कि सिग्नल दूषित न हों, और मरने तक ही सीमित संकेतों की तुलना में बहुत अधिक विद्युत शक्ति। | ||

जब एक पैकेज में कई मर जाते हैं, तो परिणाम पैकेज में एक | जब एक पैकेज में कई मर जाते हैं, तो परिणाम पैकेज में एक सिस्टम होता है, जिसे संक्षिप्त किया जाता है {{Abbr|SiP|System in Package}}. एक बहु-चिप मॉड्यूल ({{Abbr|MCM|multi-chip module}}), अक्सर सिरेमिक से बने एक छोटे सब्सट्रेट पर कई डाई को मिलाकर बनाया जाता है। एक बड़े एमसीएम और एक छोटे मुद्रित सर्किट बोर्ड के बीच का अंतर कभी-कभी अस्पष्ट होता है। | ||

पैकेज्ड इंटीग्रेटेड सर्किट आमतौर पर काफी बड़े होते हैं जिनमें पहचान की जानकारी शामिल होती है। चार सामान्य खंड हैं निर्माता का नाम या लोगो, भाग संख्या, एक भाग उत्पादन बैच संख्या और सीरियल नंबर, और चार अंकों का दिनांक-कोड यह पहचानने के लिए कि चिप का निर्माण कब किया गया था। अत्यधिक छोटे सतह-माउंट प्रौद्योगिकी भागों में अक्सर एकीकृत सर्किट की विशेषताओं को खोजने के लिए निर्माता की लुकअप तालिका में उपयोग की जाने वाली संख्या ही होती है। | |||

निर्माण की तारीख को आमतौर पर दो अंकों के वर्ष के रूप में दर्शाया जाता है, जिसके बाद दो अंकों का सप्ताह कोड होता है, जैसे कि कोड 8341 वाला एक हिस्सा 1983 के सप्ताह 41 में या लगभग अक्टूबर 1983 में निर्मित किया गया था। | |||

== बौद्धिक संपदा == | == बौद्धिक संपदा == | ||

{{Main|Integrated circuit layout design protection}} | {{Main|Integrated circuit layout design protection}} | ||

एक एकीकृत | एक एकीकृत परिपथ की प्रत्येक परत की तस्वीर खींचकर और प्राप्त तस्वीरों के आधार पर इसके उत्पादन के लिए फोटोमास्क तैयार करने की संभावना लेआउट डिजाइनों के संरक्षण के लिए कानून की शुरूआत का एक कारण है। 1984 के यूएस सेमीकंडक्टर चिप प्रोटेक्शन एक्ट ने एकीकृत सर्किट का उत्पादन करने के लिए उपयोग किए जाने वाले फोटोमास्क के लिए बौद्धिक संपदा संरक्षण की स्थापना की।<ref name="USC-circ100">{{cite web|title=Federal Statutory Protection for Mask Works|url=https://copyright.gov/circs/circ100.pdf|website=United States Copyright Office|publisher=United States Copyright Office|access-date=22 October 2016}}</ref> | ||

1989 में वाशिंगटन, डीसी में आयोजित एक राजनयिक सम्मेलन ने एकीकृत सर्किट के संबंध में बौद्धिक संपदा पर एक संधि को अपनाया,<ref>{{cite web|url=https://www.wipo.int/treaties/en/ip/washington/index.html|title=Washington Treaty on Intellectual Property in Respect of Integrated Circuits|website=www.wipo.int}}</ref> | 1989 में वाशिंगटन, डीसी में आयोजित एक राजनयिक सम्मेलन ने एकीकृत सर्किट के संबंध में बौद्धिक संपदा पर एक संधि को अपनाया,<ref>{{cite web|url=https://www.wipo.int/treaties/en/ip/washington/index.html|title=Washington Treaty on Intellectual Property in Respect of Integrated Circuits|website=www.wipo.int}}</ref> इसे वाशिंगटन संधि या आईपीआईसी संधि भी कहा जाता है। संधि वर्तमान में लागू नहीं है, लेकिन आंशिक रूप से ट्रिप्स समझौते में एकीकृत किया गया था।<ref>On 1 January 1995, the ''Agreement on Trade-Related Aspects of Intellectual Property Rights'' (TRIPs) (Annex 1C to the World Trade Organization (WTO) Agreement), went into force. Part II, section 6 of TRIPs protects semiconductor chip products and was the basis for Presidential Proclamation No. 6780, 23 March 1995, under SCPA § 902(a)(2), extending protection to all present and future WTO members.</ref> | ||

एकीकृत सर्किट से जुड़े कई संयुक्त राज्य पेटेंट हैं, जिनमें जैक किल्बी द्वारा पेटेंट शामिल हैं | जे.एस. किल्बी {{US patent|3138743|US3,138,743}}, {{US patent|3261081|US3,261,081}}, {{US patent|3434015|US3,434,015}} और आर.एफ. स्टीवर्ट {{US patent|3138747|US3,138,747}}. | |||

आईसी लेआउट डिजाइनों की रक्षा करने वाले राष्ट्रीय कानूनों को जापान सहित कई देशों में अपनाया गया है,<ref>Japan was the first country to enact its own version of the SCPA, the Japanese "Act Concerning the Circuit Layout of a Semiconductor Integrated Circuit" of 1985.</ref> यूरोपीय आर्थिक समुदाय,<ref>In 1986 the EC promulgated a directive requiring its members to adopt national legislation for the protection of semiconductor topographies. Council Directive 1987/54/EEC of 16 December 1986 on the ''Legal Protection of Topographies of Semiconductor Products'', art. 1(1)(b), 1987 O.J. (L 24) 36.</ref> यूके, ऑस्ट्रेलिया और कोरिया। यूके ने कॉपीराइट, डिजाइन और पेटेंट अधिनियम, 1988 अधिनियमित किया, c. 48, 213, शुरू में यह स्थिति लेने के बाद कि इसका कॉपीराइट कानून पूरी तरह से चिप स्थलाकृतियों की रक्षा करता है। ब्रिटिश लीलैंड मोटर कार्पोरेशन बनाम आर्मस्ट्रांग पेटेंट कंपनी देखें। | |||

ऑस्ट्रेलिया ने | |||

यूके के कॉपीराइट दृष्टिकोण की अपर्याप्तता की आलोचना, जैसा कि यूएस सेमीकंडक्टर उद्योग द्वारा माना जाता है, को आगे के चिप अधिकारों के विकास में संक्षेपित किया गया है।<ref>{{cite journal|doi=10.1109/MM.1985.304489|title=MicroLaw|journal=IEEE Micro|volume=5|issue=4|pages=90–92|year=1985|last1=Stern|first1=Richard}}</ref> | |||

ऑस्ट्रेलिया ने सर्किट लेआउट अधिनियम 1989 को चिप सुरक्षा के एक सुई जेनेरिस रूप के रूप में पारित किया।{{citation needed|date=December 2020}} कोरिया ने सेमीकंडक्टर इंटीग्रेटेड सर्किट के लेआउट-डिज़ाइन के संबंध में अधिनियम पारित किया।{{citation needed|date=December 2020}} | |||

== पीढ़ी == | == पीढ़ी == | ||

{{See also|List of semiconductor scale examples|MOS integrated circuit|Transistor count}} | {{See also|List of semiconductor scale examples|MOS integrated circuit|Transistor count}} | ||

सरल एकीकृत | सरल एकीकृत परिपथों के शुरुआती दिनों में, प्रौद्योगिकी के बड़े पैमाने ने प्रत्येक चिप को केवल कुछ ट्रांजिस्टर तक सीमित कर दिया था, और एकीकरण की निम्न डिग्री का मतलब था कि डिजाइन प्रक्रिया अपेक्षाकृत सरल थी। पहले पास की उपज भी आज के मानकों से काफी कम थी। जैसे-जैसे मेटल-ऑक्साइड-सेमीकंडक्टर (MOS) तकनीक आगे बढ़ी, लाखों और फिर अरबों MOS ट्रांजिस्टर एक चिप पर रखे जा सकते थे,<ref>Peter Clarke, ''Intel enters billion-transistor processor era'', [http://www.eetimes.com/news/latest/showArticle.jhtml?articleID=172301051 EE Times, 14 October 2005] {{Webarchive|url=https://web.archive.org/web/20130510121557/http://www.eetimes.com/news/latest/showArticle.jhtml?articleID=172301051 |date=10 May 2013 }}</ref> और अच्छे डिजाइनों के लिए पूरी तरह से योजना बनाने की आवश्यकता थी, जिससे इलेक्ट्रॉनिक डिजाइन ऑटोमेशन, या ईडीए के क्षेत्र में वृद्धि हुई। | ||

कुछ एसएसआई और एमएसआई चिप्स, असतत ट्रांजिस्टर | कुछ एसएसआई और एमएसआई चिप्स, जैसे असतत ट्रांजिस्टर, अभी भी बड़े पैमाने पर उत्पादित होते हैं, दोनों पुराने उपकरणों को बनाए रखने और नए उपकरणों का निर्माण करने के लिए केवल कुछ द्वारों की आवश्यकता होती है। उदाहरण के लिए, ट्रांजिस्टर-ट्रांजिस्टर लॉजिक चिप्स के 7400-श्रृंखला के एकीकृत सर्किट एक वास्तविक मानक बन गए हैं और उत्पादन में बने हुए हैं। | ||

{|class="wikitable sortable" | {|class="wikitable sortable" | ||

| Line 199: | Line 201: | ||

=== छोटे पैमाने पर एकीकरण (एसएसआई) {{Anchor|SSI, MSI and LSI|SSI}}===<!-- This section is linked from [[PDP-11]] and Computer fan--> | === छोटे पैमाने पर एकीकरण (एसएसआई) {{Anchor|SSI, MSI and LSI|SSI}}===<!-- This section is linked from [[PDP-11]] and Computer fan--> | ||

पहले एकीकृत | पहले एकीकृत परिपथों में केवल कुछ ट्रांजिस्टर होते थे। दसियों ट्रांजिस्टर वाले प्रारंभिक डिजिटल सर्किट में कुछ लॉजिक गेट उपलब्ध थे, और प्रारंभिक रैखिक IC जैसे कि प्लेसी SL201 या Philips TAA320 में कम से कम दो ट्रांजिस्टर थे। तब से एक एकीकृत परिपथ में ट्रांजिस्टर की संख्या में नाटकीय रूप से वृद्धि हुई है। सैद्धांतिक अवधारणा का वर्णन करते समय बड़े पैमाने पर एकीकरण (LSI) शब्द का प्रयोग पहली बार IBM वैज्ञानिक रॉल्फ लैंडौअर द्वारा किया गया था;<ref>{{Cite journal|last=Safir|first=Ruben|date=March 2015|title=System on Chip – Integrated Circuits|url=https://books.google.com/books?id=JsOmCQAAQBAJ&pg=PT39|journal=NYLXS Journal|isbn=9781312995512}}</ref> उस शब्द ने छोटे पैमाने के एकीकरण (एसएसआई), मध्यम पैमाने के एकीकरण (एमएसआई), बहुत बड़े पैमाने पर एकीकरण (वीएलएसआई), और अल्ट्रा-बड़े पैमाने पर एकीकरण (यूएलएसआई) को जन्म दिया। प्रारंभिक एकीकृत सर्किट एसएसआई थे। | ||

प्रारंभिक एयरोस्पेस परियोजनाओं के लिए एसएसआई सर्किट महत्वपूर्ण थे, और एयरोस्पेस परियोजनाओं ने प्रौद्योगिकी के विकास को प्रेरित करने में मदद की। LGM-30 Minuteman और Apollo कार्यक्रम दोनों को अपने जड़त्वीय मार्गदर्शन प्रणालियों के लिए हल्के डिजिटल कंप्यूटरों की आवश्यकता थी। हालांकि अपोलो गाइडेंस कंप्यूटर ने एकीकृत-सर्किट प्रौद्योगिकी का नेतृत्व और प्रेरित किया,<ref>{{cite book |last=Mindell |first=David A. |title=Digital Apollo: Human and Machine in Spaceflight |year=2008 |publisher=The MIT Press |isbn=978-0-262-13497-2}}</ref> यह मिनुटमैन मिसाइल थी जिसने इसे बड़े पैमाने पर उत्पादन के लिए मजबूर किया। मिनुटमैन मिसाइल कार्यक्रम और विभिन्न अन्य संयुक्त राज्य नौसेना कार्यक्रमों ने 1962 में कुल $4 मिलियन एकीकृत सर्किट बाजार के लिए जिम्मेदार था, और 1968 तक, नासा के बजट और संयुक्त राज्य अमेरिका के सैन्य बजट पर यू.एस. सरकार का खर्च अभी भी 312 मिलियन डॉलर का 37% था। कुल उत्पादन। | |||

अमेरिकी सरकार की मांग ने नवजात एकीकृत सर्किट बाजार का समर्थन किया | अमेरिकी सरकार की मांग ने नवजात एकीकृत सर्किट बाजार का समर्थन किया जब तक कि आईसी फर्मों को उद्योग (विनिर्माण) बाजार और अंततः उपभोक्ता बाजार में प्रवेश करने की अनुमति देने के लिए लागत पर्याप्त नहीं हो गई। प्रति एकीकृत परिपथ की औसत कीमत 1962 में $50.00 से गिरकर 1968 में $2.33 हो गई।<ref>{{cite book| last = Ginzberg| first = Eli| title = Economic impact of large public programs: the NASA Experience| year = 1976| publisher = Olympus Publishing Company| isbn = 978-0-913420-68-3| page = 57 }}</ref> 1970 के दशक के अंत तक उपभोक्ता उत्पादों में एकीकृत सर्किट दिखाई देने लगे। टेलीविज़न रिसीवर्स में एक विशिष्ट अनुप्रयोग फ़्रीक्वेंसी मॉड्यूलेशन इंटर-कैरियर साउंड प्रोसेसिंग था। | ||

पहला | पहला अनुप्रयोग MOSFET चिप्स छोटे पैमाने पर एकीकरण (SSI) चिप्स थे।<ref name="forging"/>1960 में मोहम्मद एम. अटाला के एमओएस इंटीग्रेटेड सर्किट चिप के प्रस्ताव के बाद,<ref name="Moskowitz">{{cite book|last1=Moskowitz|first1=Sanford L.|url=https://books.google.com/books?id=2STRDAAAQBAJ&pg=PA165|title=Advanced Materials Innovation: Managing Global Technology in the 21st century|date=2016|publisher=[[John Wiley & Sons]]|isbn=9780470508923|pages=165–167}}</ref> गढ़ी जाने वाली सबसे पहली प्रायोगिक एमओएस चिप एक 16-ट्रांजिस्टर चिप थी जिसे 1962 में आरसीए में फ्रेड हेमैन और स्टीवन हॉफस्टीन द्वारा बनाया गया था।<ref name="computerhistory-digital"/>एमओएस एसएसआई चिप्स का पहला व्यावहारिक अनुप्रयोग नासा के उपग्रहों के लिए था।<ref name="forging" /> | ||

=== मध्यम | === मध्यम स्तर का एकीकरण (एमएसआई) {{Anchor|MSI}}=== | ||

एकीकृत | एकीकृत परिपथों के विकास के अगले चरण में ऐसे उपकरण पेश किए गए जिनमें प्रत्येक चिप पर सैकड़ों ट्रांजिस्टर होते हैं, जिन्हें मध्यम-स्तरीय एकीकरण (MSI) कहा जाता है। | ||

MOSFET स्केलिंग तकनीक ने उच्च घनत्व वाले चिप्स | MOSFET स्केलिंग तकनीक ने उच्च-घनत्व वाले चिप्स बनाना संभव बना दिया है।<ref name="computerhistory-transistor"/>1964 तक, एमओएस चिप्स द्विध्रुवी जंक्शन ट्रांजिस्टर चिप्स की तुलना में उच्च ट्रांजिस्टर घनत्व और कम विनिर्माण लागत तक पहुंच गए थे।<ref name="ieee"/> | ||

1964 में, फ्रैंक वानलास ने एक | 1964 में, फ्रैंक वानलास ने एक सिंगल-चिप 16-बिट शिफ्ट रजिस्टर का प्रदर्शन किया, जिसे उन्होंने डिज़ाइन किया था, जिसमें एक एकल चिप पर तत्कालीन-अविश्वसनीय 120 MOS ट्रांजिस्टर थे।<ref name="forging">{{cite book | title = We were burning: Japanese entrepreneurs and the forging of the electronic age | author = Johnstone, Bob | publisher = Basic Books | year = 1999 | isbn = 978-0-465-09118-8 | pages = 47–48 | url = https://books.google.com/books?id=PE1bQS9VpWoC&pg=PA47 }}</ref><ref>{{cite web| url = http://www.eecs.umich.edu/eecs/about/articles/2007/Boysel.html| title = Making Your First Million (and other tips for aspiring entrepreneurs)| author = Boysel, Lee | date = 2007-10-12| work = U. Mich. EECS Presentation / ECE Recordings}}</ref> उसी वर्ष, जनरल माइक्रोइलेक्ट्रॉनिक ने पहली वाणिज्यिक एमओएस एकीकृत सर्किट चिप पेश की, जिसमें 120 पीएमओएस लॉजिक | पी-चैनल एमओएस ट्रांजिस्टर शामिल थे।<ref name="computerhistory1964"/>यह एक 20-बिट शिफ्ट रजिस्टर था, जिसे रॉबर्ट नॉर्मन द्वारा विकसित किया गया था<ref name="computerhistory-digital"/>और फ्रैंक वानलास।<ref>{{cite journal |last1=Kilby |first1=J. S. |title=Miniaturized electronic circuits [US Patent No. 3,138, 743] |journal=IEEE Solid-State Circuits Society Newsletter |date=2007 |volume=12 |issue=2 |pages=44–54 |doi=10.1109/N-SSC.2007.4785580 |url=https://www.researchgate.net/publication/245509003 }}</ref> मूर के नियम द्वारा अनुमानित दर पर MOS चिप्स जटिलता में और बढ़ गए, जिससे 1960 के दशक के अंत तक एक चिप पर सैकड़ों MOSFETs के साथ चिप्स बन गए।<ref name="ieee"/> | ||

=== बड़े पैमाने पर एकीकरण ( | === बड़े पैमाने पर एकीकरण (LSI) {{Anchor|LSI}}=== | ||

समान MOSFET स्केलिंग तकनीक और आर्थिक कारकों द्वारा संचालित आगे के विकास ने 1970 के दशक के मध्य तक प्रति चिप हजारों ट्रांजिस्टर के साथ बड़े पैमाने पर एकीकरण (LSI) का नेतृत्व किया।<ref name="Hittinger">{{cite journal |last1=Hittinger |first1=William C. |title=Metal-Oxide-Semiconductor Technology |journal=Scientific American |date=1973 |volume=229 |issue=2 |pages=48–59 |jstor=24923169 |doi=10.1038/scientificamerican0873-48 |bibcode=1973SciAm.229b..48H }}</ref> | |||

एसएसआई, एमएसआई और शुरुआती एलएसआई और वीएलएसआई उपकरणों (जैसे कि 1970 के दशक के | एसएसआई, एमएसआई और शुरुआती एलएसआई और वीएलएसआई उपकरणों (जैसे कि 1970 के दशक के शुरुआती माइक्रोप्रोसेसरों) को संसाधित करने और निर्माण करने के लिए उपयोग किए जाने वाले मुखौटे ज्यादातर हाथ से बनाए जाते थे, अक्सर रूबीलिथ-टेप या इसी तरह का उपयोग करते थे।<ref>{{cite web |url=https://www.cnet.com/news/intels-accidental-revolution/ |title=Intel's Accidental Revolution |website=CNET|author=Kanellos, Michael |date=January 16, 2002}}</ref> बड़े या जटिल आईसी (जैसे कंप्यूटर मेमोरी या प्रोसेसर (कंप्यूटिंग)) के लिए, यह अक्सर सर्किट लेआउट के प्रभारी विशेष रूप से किराए के पेशेवरों द्वारा किया जाता था, जिन्हें इंजीनियरों की एक टीम की देखरेख में रखा जाता था, जो सर्किट डिजाइनरों के साथ भी होगा। प्रत्येक मास्क का निरीक्षण और कार्यात्मक सत्यापन। | ||

एकीकृत सर्किट जैसे | एकीकृत सर्किट जैसे 1K-बिट RAM, कैलकुलेटर चिप्स, और पहला माइक्रोप्रोसेसर, जो 1970 के दशक की शुरुआत में मध्यम मात्रा में निर्मित होना शुरू हुआ, में 4,000 ट्रांजिस्टर थे। ट्रू एलएसआई सर्किट, 10,000 ट्रांजिस्टर के करीब, कंप्यूटर की मुख्य यादों और दूसरी पीढ़ी के माइक्रोप्रोसेसरों के लिए 1974 के आसपास निर्मित होने लगे। | ||

=== बहुत | === बहुत बड़े पैमाने पर एकीकरण (वीएलएसआई) === | ||

{{Main|Very-large-scale integration}} | {{Main|Very-large-scale integration}} | ||

[[File:80486DX2 200x.png|right|thumb| | [[File:80486DX2 200x.png|right|thumb|Intel 80486DX2 माइक्रोप्रोसेसर पर ऊपरी इंटरकनेक्ट परतें मर जाती हैं]] | ||

1980 के दशक की शुरुआत में | वेरी-लार्ज-स्केल इंटीग्रेशन (वीएलएसआई) एक ऐसा विकास है जिसकी शुरुआत 1980 के दशक की शुरुआत में सैकड़ों हजारों ट्रांजिस्टर के साथ हुई थी, और 2016 तक, ट्रांजिस्टर की संख्या प्रति चिप दस बिलियन ट्रांजिस्टर से आगे बढ़ रही है। | ||

इस बढ़े हुए घनत्व को प्राप्त करने के लिए कई | इस बढ़े हुए घनत्व को प्राप्त करने के लिए कई विकासों की आवश्यकता थी। निर्माता छोटे MOSFET डिज़ाइन नियमों और क्लीनरूम में चले गए। प्रक्रिया में सुधार के मार्ग को सेमीकंडक्टर्स (आईटीआरएस) के लिए अंतर्राष्ट्रीय प्रौद्योगिकी रोडमैप द्वारा संक्षेपित किया गया था, जिसे बाद में उपकरणों और प्रणालियों के लिए अंतर्राष्ट्रीय रोडमैप (आईआरडीएस) द्वारा सफल बनाया गया है। इलेक्ट्रॉनिक डिजाइन ऑटोमेशन में सुधार हुआ, जिससे डिजाइनों को उचित समय में खत्म करना व्यावहारिक हो गया। अधिक ऊर्जा कुशल CMOS ने NMOS तर्क और PMOS तर्क को बदल दिया, ऊर्जा खपत में निषेधात्मक वृद्धि से बचा। आधुनिक वीएलएसआई उपकरणों की जटिलता और घनत्व ने मास्क की जांच करना या हाथ से मूल डिजाइन करना संभव नहीं बना दिया। इसके बजाय, इंजीनियर उपयोग करते हैं {{Abbr|EDA|Electronic design automation}} सबसे कार्यात्मक सत्यापन कार्य करने के लिए उपकरण।<ref>{{cite journal|doi=10.1109/AFIPS.1968.93|year=1968|journal=Afips 1968|author=O'Donnell, C.F. |url=http://www.computer.org/csdl/proceedings/afips/1968/5072/00/50720867.pdf|title=Engineering for systems using large scale integration|page= 870}}</ref> | ||

1986 में, एक- | 1986 में, एक-मेगाबिट रैंडम-एक्सेस मेमोरी (RAM) चिप्स पेश किए गए, जिसमें एक मिलियन से अधिक ट्रांजिस्टर थे। माइक्रोप्रोसेसर चिप्स ने 1989 में मिलियन-ट्रांजिस्टर का निशान और 2005 में बिलियन-ट्रांजिस्टर का निशान पार किया।<ref>{{cite web |last1=Clarke |first1=Peter |title=Intel enters billion-transistor processor era |url=https://www.eetimes.com/intel-enters-billion-transistor-processor-era/ |website=EETimes.com |access-date=May 23, 2022 |date=14 October 2005}}</ref> यह प्रवृत्ति काफी हद तक बेरोकटोक जारी है, 2007 में पेश किए गए चिप्स में दसियों अरबों मेमोरी ट्रांजिस्टर शामिल हैं।<ref>{{cite web |title=Samsung First to Mass Produce 16Gb NAND Flash Memory |url=https://phys.org/news/2007-04-samsung-mass-16gb-nand-memory.html |website=phys.org |access-date=May 23, 2022 |date=April 30, 2007}}</ref> | ||

=== ULSI, WSI, | === ULSI, WSI, SoC और 3D-IC === | ||

{{See|Wafer-scale integration|System on a chip|Three-dimensional integrated circuit}} | {{See|Wafer-scale integration|System on a chip|Three-dimensional integrated circuit}} | ||

जटिलता के और विकास को प्रतिबिंबित करने के लिए, ULSI शब्द जो अल्ट्रा-लार्ज-स्केल | जटिलता के और विकास को प्रतिबिंबित करने के लिए, ULSI शब्द जो अल्ट्रा-लार्ज-स्केल इंटीग्रेशन के लिए है, 1 मिलियन से अधिक ट्रांजिस्टर के चिप्स के लिए प्रस्तावित किया गया था।<ref>{{cite journal|last1=Meindl|first1=J.D.|title=Ultra-large scale integration|journal=IEEE Transactions on Electron Devices|volume=31|issue=11|pages=1555–1561|doi=10.1109/T-ED.1984.21752|year=1984|bibcode=1984ITED...31.1555M|s2cid=19237178}}</ref> | ||

वेफर-स्केल इंटीग्रेशन ( | वेफर-स्केल इंटीग्रेशन (WSI) बहुत बड़े एकीकृत परिपथों के निर्माण का एक साधन है जो एक एकल सुपर-चिप का उत्पादन करने के लिए संपूर्ण सिलिकॉन वेफर का उपयोग करता है। बड़े आकार और कम पैकेजिंग के संयोजन के माध्यम से, WSI कुछ प्रणालियों के लिए नाटकीय रूप से कम लागत का कारण बन सकता है, विशेष रूप से बड़े पैमाने पर समानांतर सुपर कंप्यूटर। यह नाम वेरी-लार्ज-स्केल इंटीग्रेशन शब्द से लिया गया है, जब डब्ल्यूएसआई विकसित किया जा रहा था, तब कला की वर्तमान स्थिति।<ref>{{cite web|date=1985|last1=Shanefield|first1=Daniel|title=Wafer scale integration|url=http://www.google.com/patents/US4866501|website=google.com/patents|access-date=21 September 2014}}</ref> | ||

एक सिस्टम-ऑन-ए-चिप (एसओसी या एसओसी) एक एकीकृत सर्किट है जिसमें कंप्यूटर या अन्य सिस्टम के लिए आवश्यक सभी घटकों को | एक सिस्टम-ऑन-ए-चिप (एसओसी या एसओसी) एक एकीकृत सर्किट है जिसमें कंप्यूटर या अन्य सिस्टम के लिए आवश्यक सभी घटकों को एक चिप पर शामिल किया जाता है। इस तरह के एक उपकरण का डिज़ाइन जटिल और महंगा हो सकता है, और जबकि प्रदर्शन लाभ एक ही बार में सभी आवश्यक घटकों को एकीकृत करने से प्राप्त किया जा सकता है, लाइसेंस की लागत और एक-मरने वाली मशीन को विकसित करने की लागत अभी भी अलग-अलग उपकरणों से अधिक है। उपयुक्त लाइसेंस के साथ, इन कमियों को कम विनिर्माण और असेंबली लागत और बहुत कम बिजली बजट द्वारा ऑफसेट किया जाता है: क्योंकि घटकों के बीच सिग्नल ऑन-डाई रखे जाते हैं, बहुत कम बिजली की आवश्यकता होती है (देखें #पैकेजिंग)।<ref>{{cite web|last1=Klaas|first1=Jeff|title=System-on-a-chip|date=2000|url=http://www.google.com/patents/US6816750|website=google.com/patents|access-date=21 September 2014}}</ref> इसके अलावा, सिग्नल स्रोत और गंतव्य हैं मरने पर संदर्भ का स्थान, तारों की लंबाई को कम करना और इसलिए विलंबता (इंजीनियरिंग), डेटा ट्रांसमिशन बिजली की लागत और एक ही चिप पर मॉड्यूल के बीच संचार से अपशिष्ट गर्मी। इसने तथाकथित नेटवर्क ऑन चिप | नेटवर्क-ऑन-चिप (एनओसी) उपकरणों की खोज को प्रेरित किया है, जो पारंपरिक बस (कंप्यूटिंग) के विपरीत डिजिटल संचार नेटवर्क के लिए सिस्टम-ऑन-चिप डिज़ाइन पद्धति को लागू करते हैं। | ||

एक त्रि-आयामी एकीकृत सर्किट ( | एक त्रि-आयामी एकीकृत सर्किट (3D-IC) में सक्रिय इलेक्ट्रॉनिक घटकों की दो या दो से अधिक परतें होती हैं जो एक एकल सर्किट में लंबवत और क्षैतिज रूप से एकीकृत होती हैं। परतों के बीच संचार ऑन-डाई सिग्नलिंग का उपयोग करता है, इसलिए बिजली की खपत समकक्ष अलग सर्किट की तुलना में बहुत कम है। छोटे ऊर्ध्वाधर तारों का विवेकपूर्ण उपयोग तेजी से संचालन के लिए समग्र तार की लंबाई को काफी हद तक कम कर सकता है।<ref>{{cite journal|last1=Topol|first1=A.W.|last2=Tulipe|first2=D.C.La|last3=Shi|first3=L|last4=et.|first4=al|title=Three-dimensional integrated circuits|journal=IBM Journal of Research and Development|volume=50|issue=4.5|pages=491–506|doi=10.1147/rd.504.0491|year=2006|s2cid=18432328|url=https://semanticscholar.org/paper/8de20d9e01b189c02f5e68ae3720965bed48c82c}}</ref> | ||

== सिलिकॉन लेबलिंग और भित्तिचित्र == | == सिलिकॉन लेबलिंग और भित्तिचित्र == | ||

उत्पादन के दौरान पहचान की अनुमति देने के लिए, अधिकांश सिलिकॉन चिप्स | उत्पादन के दौरान पहचान की अनुमति देने के लिए, अधिकांश सिलिकॉन चिप्स के एक कोने में एक सीरियल नंबर होगा। निर्माता का लोगो जोड़ना भी आम है। जब से IC बनाया गया है, कुछ चिप डिजाइनरों ने गुप्त, गैर-कार्यात्मक छवियों या शब्दों के लिए सिलिकॉन सतह क्षेत्र का उपयोग किया है। इन्हें कभी-कभी चिप आर्ट, सिलिकॉन आर्ट, सिलिकॉन ग्रैफिटी या सिलिकॉन डूडलिंग के रूप में जाना जाता है।{{citation needed|date=December 2020}} | ||

== | == आईसी और आईसी परिवार == | ||

* 555 टाइमर आईसी | * 555 टाइमर आईसी | ||

* | * ऑपरेशनल एम्पलीफायर | ||

* 7400-श्रृंखला एकीकृत सर्किट | * 7400-श्रृंखला एकीकृत सर्किट | ||

* 4000-श्रृंखला एकीकृत सर्किट, | * 4000-श्रृंखला एकीकृत सर्किट, 7400 श्रृंखला के लिए CMOS समकक्ष (यह भी देखें: HCMOS) | ||

* इंटेल 4004, आम तौर पर | * इंटेल 4004, जिसे आम तौर पर व्यावसायिक रूप से उपलब्ध पहला माइक्रोप्रोसेसर माना जाता है, जिसके कारण प्रसिद्ध इंटेल 8080 सीपीयू और फिर आईबीएम पीसी के इंटेल 8088, 80286, इंटेल i486 आदि। | ||

* MOS | * MOS Technology 6502 और Zilog Z80 माइक्रोप्रोसेसर, 1980 के दशक की शुरुआत में कई घरेलू कंप्यूटरों में उपयोग किए गए थे | ||

* कंप्यूटर से संबंधित चिप्स की मोटोरोला 6800 श्रृंखला, 68000 और 88000 श्रृंखला (कुछ | * कंप्यूटर से संबंधित चिप्स की मोटोरोला 6800 श्रृंखला, 68000 और 88000 श्रृंखला (कुछ एप्पल कंप्यूटरों में और 1980 के दशक में कमोडोर अमीगा श्रृंखला में प्रयुक्त) | ||

* एलएम- | * एलएम-श्रृंखला एकीकृत परिपथों की सूची|एनालॉग एकीकृत परिपथों की एलएम-श्रृंखला | ||

== यह भी देखें == | == यह भी देखें == | ||

{{Portal|Electronics|Physics|Technology|Telecommunication|Engineering|History of science|Companies|Computer programming|Amiga/Selected biography|Telephones}} | {{Portal|Electronics|Physics|Technology|Telecommunication|Engineering|History of science|Companies|Computer programming|Amiga/Selected biography|Telephones}} | ||

* चिपसेट | * चिपसेट | ||

*चिप्स और विज्ञान अधिनियम | |||

* एकीकृत इंजेक्शन तर्क | * एकीकृत इंजेक्शन तर्क | ||

* आयन आरोपण | *आयन आरोपण | ||

*माइक्रोइलेक्ट्रॉनिक्स | *माइक्रोइलेक्ट्रॉनिक्स | ||

* | * मोनोलिथिक माइक्रोवेव इंटीग्रेटेड सर्किट | ||

* | * बहु-दहलीज CMOS | ||

* सिलिकॉन-जर्मेनियम | *सिलिकॉन-जर्मेनियम* | ||

* साउंड चिप | * साउंड चिप | ||

* मसाला | * मसाला | ||

* चिप वाहक | *चिप वाहक | ||

*डार्क सिलिकॉन | *डार्क सिलिकॉन | ||

*एकीकृत निष्क्रिय उपकरण | *एकीकृत निष्क्रिय उपकरण | ||

*उच्च तापमान | *उच्च तापमान परिचालन जीवन | ||

*एकीकृत सर्किट के लिए थर्मल सिमुलेशन | *एकीकृत सर्किट के लिए थर्मल सिमुलेशन | ||

*एकीकृत | *एकीकृत परिपथों में ऊष्मा उत्पन्न करना | ||

== संदर्भ == | == संदर्भ == | ||

{{Reflist}} | {{Reflist}} | ||

==इस पृष्ठ में अनुपलब्ध आंतरिक कड़ियों की सूची== | |||

*विशिष्ट एकीकृत परिपथ आवेदन | |||

*डिजिटल डाटा | |||

*आंकड़े | |||

*के माध्यम से (इलेक्ट्रॉनिक्स) | |||

*विनिर्माण क्षमता के लिए डिजाइन (आईसी) | |||

*संवहन दस्तावेज़ स्वरूप | |||