धारिता: Difference between revisions

mNo edit summary |

mNo edit summary |

||

| Line 16: | Line 16: | ||

}} | }} | ||

{{Electromagnetism |Network}} | {{Electromagnetism |Network}} | ||

'''''कैपेसिटेंस [[ विद्युत कंडक्टर |विद्युत कंडक्टर]] (''''' इलेक्ट्रिक कंडक्टर) पर संग्रहीत [[ आवेश |आवेश]] की मात्रा और विद्युत क्षमता में | '''''कैपेसिटेंस [[ विद्युत कंडक्टर |विद्युत कंडक्टर]] (''''' इलेक्ट्रिक कंडक्टर) पर संग्रहीत [[ आवेश |आवेश]] की मात्रा और विद्युत क्षमता में अंतर का अनुपात है। धारिता के दो प्रकार है जो आपस में एक दूसरे से सम्बंधित है: ''सेल्फ कैपेसिटेंस (आत्म धारिता) ''और ''म्यूचुअल कैपेसिटेंस (पारस्परिक धारिता)''।<ref name=Harrington_2003>{{cite book |last=Harrington |first=Roger F. |author-link=Roger F. Harrington |title=Introduction to Electromagnetic Engineering |publisher=Dover Publications |year=2003 |edition=1st |page=43 |isbn=0-486-43241-6}}</ref>{{rp|237–238}} कोई भी वस्तु जिसे विद्युत रूप से चार्ज किया जा सकता है वह आत्म धारिता प्रदर्शित करता है। इस मामले में वस्तु और जमीन के बीच[[ संभावित अंतर | संभावित विद्युत अंतर]] मापा जाता है। पारस्परिक धारिता को दो कंडक्टरों के बीच मापा जाता है,और यह संधारित्र के संचालन में विशेष रूप से महत्वपूर्ण है, (प्रतिरोधों और [[ प्रारंभ करनेवाला ]]ों के साथ) इस उद्देश्य के लिए एक प्राथमिक रैखिक इलेक्ट्रॉनिक घटक के रूप में उपकरण डिज़ाइन किया गया है। [[ संधारित्र |संधारित्र]] के संचालन को समझने के लिए पारस्परिक धारिता की धारणा विशेष रूप से महत्वपूर्ण है। एक विशिष्ट संधारित्र में, दो कंडक्टरों का उपयोग इलेक्ट्रिक चार्ज को अलग करने के लिए किया जाता है, जिसमें एक कंडक्टर को धनात्मक रूप से चार्ज किया जाता है और दूसरा ऋणात्मक रूप से चार्ज किया जाता है, लेकिन सिस्टम का कुल चार्ज शून्य होता है। | ||

धारिता केवल संधारित्र के डिजाइन की ज्यामिति का एक कार्य है, उदाहरण के लिए, प्लेटों का विरोधी सतह क्षेत्र और उनके बीच की दूरी, और प्लेटों के बीच परावैद्युत पदार्थ की पारगम्यता। कई परावैद्युत पदार्थ के लिए, पारगम्यता और धारिता, कंडक्टरों के बीच [[ संभावित अंतर |संभावित विद्युत अंतर]] और उन पर उपस्थित कुल चार्ज से स्वतंत्र है। | धारिता केवल संधारित्र के डिजाइन की ज्यामिति का एक कार्य है, उदाहरण के लिए, प्लेटों का विरोधी सतह क्षेत्र और उनके बीच की दूरी, और प्लेटों के बीच परावैद्युत पदार्थ की पारगम्यता। कई परावैद्युत पदार्थ के लिए, पारगम्यता और धारिता, कंडक्टरों के बीच [[ संभावित अंतर |संभावित विद्युत अंतर]] और उन पर उपस्थित कुल चार्ज से स्वतंत्र है। | ||

| Line 22: | Line 22: | ||

कैपेसिटेंस की एसआई इकाई अंग्रेजी भौतिक वैज्ञानिक[[ माइकल फैराडे ]]के नाम पर फैराड (प्रतीक: एफ) है। 1 फैराड कैपेसिटर, जब 1[[ कूलम्ब | कूलम्ब]] विद्युत आवेश के साथ आरोपित किया जाता है, तो इसकी प्लेटों के बीच 1[[ वाल्ट | वोल्ट]] का संभावित अंतर होता है।<ref>{{cite web |url=http://www.collinsdictionary.com/dictionary/english/farad |title=Definition of 'farad' |publisher=Collins}}</ref> धारिता के वुत्पन्न को [[ इलास्टेंस |इलास्टेंस]] कहा जाता है। | कैपेसिटेंस की एसआई इकाई अंग्रेजी भौतिक वैज्ञानिक[[ माइकल फैराडे ]]के नाम पर फैराड (प्रतीक: एफ) है। 1 फैराड कैपेसिटर, जब 1[[ कूलम्ब | कूलम्ब]] विद्युत आवेश के साथ आरोपित किया जाता है, तो इसकी प्लेटों के बीच 1[[ वाल्ट | वोल्ट]] का संभावित अंतर होता है।<ref>{{cite web |url=http://www.collinsdictionary.com/dictionary/english/farad |title=Definition of 'farad' |publisher=Collins}}</ref> धारिता के वुत्पन्न को [[ इलास्टेंस |इलास्टेंस]] कहा जाता है। | ||

== स्व समाई == | == स्व समाई(आत्म धारिता) == | ||

विद्युत | विद्युत परिपथ में, धारिता शब्द आमतौर पर दो आसन्न कंडक्टरों के बीच पारस्परिक समाई के लिए एक आशुलिपि (शॉर्टहैंड) है, जैसे कि एक संधारित्र की दो प्लेटें। हालांकि, एक पृथक संधारित्र के लिए, सेल्फ कैपेसिटेंस (आत्म धारिता) नामक एक संपत्ति भी मौजूद है, जो कि विद्युत आवेश की मात्रा है जिसे एक अलग संधारित्र में जोड़ा जाना चाहिए ताकि इसकी विद्युत क्षमता को एक इकाई (यानी एक वोल्ट, अधिकांश माप प्रणालियों में) तक बढ़ाया जा सके।<ref>{{cite book|author=William D. Greason| title=Electrostatic discharge in electronics|url=https://books.google.com/books?id=404fAQAAIAAJ|year=1992|publisher=Research Studies Press|isbn=978-0-86380-136-5 |page=48}}</ref> इस विभव के लिए संदर्भ बिंदु इस क्षेत्र के अंदर केंद्रित संधारित्र के साथ अनंत त्रिज्या का एक सैद्धांतिक खोखला क्षेत्र है। | ||

गणितीय रूप से, एक | गणितीय रूप से, एक संधारित्र की सेल्फ कैपेसिटेंस (आत्म धारिता) को परिभाषित किया गया है | ||

<math display="block">C = \frac{q}{V},</math> | <math display="block">C = \frac{q}{V},</math> | ||

जहाँ पे | जहाँ पे | ||

| Line 42: | Line 42: | ||

*एक वैन डी[[ ग्राफ जनरेटर से | ग्राफ जनरेटर]] की शीर्ष प्लेट के लिए,आमतौर पर एक वृत्त त्रिज्या में 20 सेमी: 22.24 पीएफ, | *एक वैन डी[[ ग्राफ जनरेटर से | ग्राफ जनरेटर]] की शीर्ष प्लेट के लिए,आमतौर पर एक वृत्त त्रिज्या में 20 सेमी: 22.24 पीएफ, | ||

*ग्रह पृथ्वी: लगभग 710 µf।<ref>{{cite book | last1 = Tipler | first1 = Paul | last2 = Mosca | first2 = Gene | title = Physics for Scientists and Engineers | publisher = Macmillan | year = 2004 | edition = 5th | page = 752 | isbn = 978-0-7167-0810-0 }}</ref> | *ग्रह पृथ्वी: लगभग 710 µf।<ref>{{cite book | last1 = Tipler | first1 = Paul | last2 = Mosca | first2 = Gene | title = Physics for Scientists and Engineers | publisher = Macmillan | year = 2004 | edition = 5th | page = 752 | isbn = 978-0-7167-0810-0 }}</ref> | ||

एक विद्युत चुम्बकीय कुंडल की अंतर-घुमावदार धारिता को कभी-कभी आत्म धारिता कहा जाता है,<ref>{{cite journal| title=Self capacitance of inductors|doi=10.1109/63.602562 |author1=Massarini, A. |author2=Kazimierczuk, M.K. |year=1997 |volume=12 |issue=4 |pages=671–676 |journal=IEEE Transactions on Power Electronics |postscript=: example of the use of the term 'self capacitance'.|bibcode=1997ITPE...12..671M |citeseerx=10.1.1.205.7356 }}</ref> लेकिन यह एक अलग घटना है।यह वास्तव में कॉइल के अलग-अलग मोड़ के बीच पारस्परिक धारिता है और आवारा, या [[ परजीवी समाई | परजीवी समाई(धारिता)]] का एक रूप है। यह आत्म धारिता उच्च आवृत्तियों के लिए महत्वपूर्ण विचार है: यह कॉइल के [[ विद्युत प्रतिबाधा |विद्युत प्रतिबाधा]] को बदलता है और समानांतर विद्युत अनुनाद को जन्म देता है। कई अनुप्रयोगों में यह एक अवांछनीय प्रभाव है और परिपथ के सही संचालन के लिए एक ऊपरी आवृत्ति सीमा निर्धारित करता है।{{citation needed|date=May 2017}} | एक विद्युत चुम्बकीय कुंडल की अंतर-घुमावदार धारिता को कभी-कभी आत्म धारिता कहा जाता है,<ref>{{cite journal| title=Self capacitance of inductors|doi=10.1109/63.602562 |author1=Massarini, A. |author2=Kazimierczuk, M.K. |year=1997 |volume=12 |issue=4 |pages=671–676 |journal=IEEE Transactions on Power Electronics |postscript=: example of the use of the term 'self capacitance'.|bibcode=1997ITPE...12..671M |citeseerx=10.1.1.205.7356 }}</ref> लेकिन यह एक अलग घटना है।यह वास्तव में कॉइल के अलग-अलग मोड़ के बीच पारस्परिक धारिता है और आवारा, या [[ परजीवी समाई | परजीवी समाई (धारिता)]] का एक रूप है। यह आत्म धारिता उच्च आवृत्तियों के लिए महत्वपूर्ण विचार है: यह कॉइल के [[ विद्युत प्रतिबाधा |विद्युत प्रतिबाधा]] को बदलता है और समानांतर विद्युत अनुनाद को जन्म देता है। कई अनुप्रयोगों में यह एक अवांछनीय प्रभाव है और परिपथ के सही संचालन के लिए एक ऊपरी आवृत्ति सीमा निर्धारित करता है।{{citation needed|date=May 2017}} | ||

== म्यूचुअल कैपेसिटेंस == | == म्यूचुअल कैपेसिटेंस (पारस्परिक धारिता) == | ||

ये ,सामान्य रूप एक समानांतर-प्लेट संधारित्र है, जिसमें दो प्रवाहकीय प्लेटें होती हैं,और ये दोनों प्लेट एक दूसरे के ऊपर रखीं होती हैं,आमतौर पर प्लेट एक दूसरे के ऊपर ऐसे रखीं होती है जैसे डाइइलेक्ट्रिक | ये ,सामान्य रूप एक समानांतर-प्लेट संधारित्र है, जिसमें दो प्रवाहकीय प्लेटें होती हैं,और ये दोनों प्लेट एक दूसरे के ऊपर रखीं होती हैं,आमतौर पर प्लेट एक दूसरे के ऊपर ऐसे रखीं होती है जैसे डाइइलेक्ट्रिक सामग्री उन दोनों प्लेट के बीच में रखा हो। एक समानांतर प्लेट संधारित्र में,धारिता संधारित्र प्लेटों के सतह क्षेत्र के समानुपाती और और दो प्लेट के बीच की दूरी के व्युत्क्रमानुपाती होता है। | ||

यदि प्लेटों पर आवेश +Q और, -Q हैं, और V प्लेटों के बीच [[ वोल्टेज |वोल्टेज]] देता है, तो | यदि प्लेटों पर आवेश +Q और, -Q हैं, और V प्लेटों के बीच [[ वोल्टेज |वोल्टेज]] देता है, तो धारिता को C द्वारा प्रदर्शित किया जाता है। <math display="block">C = \frac{q}{V},</math> | ||

जो वोल्टेज और विद्युत धारा में सम्बन्ध प्रदर्शित करता है | जो वोल्टेज और विद्युत धारा में सम्बन्ध प्रदर्शित करता है | ||

<math display="block">i(t) = C \frac{\mathrm{d}v(t)}{\mathrm{d}t},</math> | <math display="block">i(t) = C \frac{\mathrm{d}v(t)}{\mathrm{d}t},</math> | ||

| Line 55: | Line 55: | ||

=== कैपेसिटेंस मैट्रिक्स === | === कैपेसिटेंस मैट्रिक्स (धारिता मैट्रिक्स) === | ||

उपरोक्त चर्चा दो संचालन प्लेटों के मामले तक सीमित है, हालांकि मनमानी आकार और आकृति की है। ये परिभाषा | उपरोक्त चर्चा दो संचालन प्लेटों के मामले तक सीमित है, हालांकि मनमानी आकार और आकृति की है। ये परिभाषा <math>C = Q/V</math> तब लागू नहीं है जब दो से अधिक चार्ज किए गए प्लेटें होती हैं , या जब दो प्लेटों पर नेट चार्ज शून्य नहीं होता है। इस मामले को संभालने के लिए, मैक्सवेल ने अपने संभावित गुणांक पेश किए। यदि तीन (लगभग आदर्श) कंडक्टरों को आवेश <math>Q_1, Q_2, Q_3</math>, दिया जाता है तो कंडक्टर 1 पर दिया गया वोल्टेज है: | ||

<math display="block">V_1 = P_{11}Q_1 + P_{12} Q_2 + P_{13}Q_3, </math> | <math display="block">V_1 = P_{11}Q_1 + P_{12} Q_2 + P_{13}Q_3, </math> | ||

और इसी तरह अन्य वोल्टेज के लिये [[ हरमन वॉन हेल्महोल्त्ज़ |हरमन वॉन हेल्महोल्त्ज़]] और[[ सर विलियम थॉमसन ]]ने प्रदिर्शित किया कि क्षमता के गुणांक सममित हैं, और इसलिए <math>P_{12} = P_{21}</math> होगा। इस प्रकार प्रणाली को इलास्टेंस मैट्रिक्स या पारस्परिक धारिता मैट्रिक्स के रूप में ज्ञात गुणांक के संग्रह द्वारा वर्णित किया जा सकता है, जिसे इस प्रकार परिभाषित किया गया है: | और इसी तरह अन्य वोल्टेज के लिये [[ हरमन वॉन हेल्महोल्त्ज़ |हरमन वॉन हेल्महोल्त्ज़]] और[[ सर विलियम थॉमसन ]]ने प्रदिर्शित किया कि क्षमता के गुणांक सममित हैं, और इसलिए <math>P_{12} = P_{21}</math> होगा। इस प्रकार प्रणाली को इलास्टेंस मैट्रिक्स या पारस्परिक धारिता मैट्रिक्स के रूप में ज्ञात गुणांक के संग्रह द्वारा वर्णित किया जा सकता है, जिसे इस प्रकार परिभाषित किया गया है: | ||

| Line 69: | Line 69: | ||

== कैपेसिटर (संधारित्र) == | == कैपेसिटर (संधारित्र) == | ||

विद्युत परिपथ में उपयोग किए जाने वाले ज्यादातर संधारित्र की धारिता आम तौर पर फैराड की तुलना में बहुत छोटी है। आज सबसे ज्यादा आम उपयोग में आने वाली धारिता की उपइकाई [[ सूक्ष्म |सूक्ष्म]] फ़ारड (µf), [[ नैनो ]]फ़ारड (nf), [[ पिको- |पिको-]] फराड (pf), और, सूक्ष्मपरिपथ मे, [[ स्त्री |स्त्री]] फारड (Ff) हैं। हालांकि, विशेष रूप से बनाए गए [[ सुपरकैपेसिटर | | विद्युत परिपथ में उपयोग किए जाने वाले ज्यादातर संधारित्र की धारिता आम तौर पर फैराड की तुलना में बहुत छोटी है। आज सबसे ज्यादा आम उपयोग में आने वाली धारिता की उपइकाई [[ सूक्ष्म |सूक्ष्म]] फ़ारड (µf), [[ नैनो ]]फ़ारड (nf), [[ पिको- |पिको-]] फराड (pf), और, सूक्ष्मपरिपथ मे, [[ स्त्री |स्त्री]] फारड (Ff) हैं। हालांकि, विशेष रूप से बनाए गए [[ सुपरकैपेसिटर |सुपर कैपेसिटर]] बहुत बड़े हो सकते हैं (जितना सैकड़ों फैराड्स), और परजीवी कैपेसिटिव तत्व एक फेमटोफराड से कम हो सकते हैं। अतीत में, पुराने ऐतिहासिक पाठ में वैकल्पिक उपइकाई का उपयोग किया गया था; माइक्रोफारड के लिए (एमएफ) और (एमएफडी); "mmf", "mmfd", [[ पिको- |पिको-]] फराड "pfd", (PF) के लिए; लेकिन अब यह अप्रचलित माना जाता है।<ref>{{cite web |url=http://www.justradios.com/MFMMFD.html |title=Capacitor MF-MMFD Conversion Chart |website=Just Radios}}</ref><ref>{{cite book |url=https://archive.org/details/FundamentalsOfElectronics93400A1b |title=Fundamentals of Electronics |volume=1b — Basic Electricity — Alternating Current |publisher=Bureau of Naval Personnel |year=1965 |page=[https://archive.org/details/FundamentalsOfElectronics93400A1b/page/n58 197]}}</ref> | ||

यदि | यदि संधारित्र की ज्यामिति और संधारित्रों के बीच इन्सुलेटर के परावैद्युत गुण ज्ञात हों तो धारिता की गणना की जा सकती है। <br> | ||

जब एक धनात्मक आवेश एक सुचालक को दिया जाता है, यह आवेश एक विद्युत क्षेत्र बनाता है, जोकि सुचालक पर स्थानांतरित किए जाने वाले किसी भी अन्य धनात्मक आवेश को प्रतिकर्षित करता है; यानी,आवश्यक वोल्टेज बढ़ाता है। लेकिन अगर पास में एक अन्य सुचालक है, और अगर उस पर एक | जब एक धनात्मक आवेश एक सुचालक को दिया जाता है, यह आवेश एक विद्युत क्षेत्र बनाता है, जोकि सुचालक पर स्थानांतरित किए जाने वाले किसी भी अन्य धनात्मक आवेश को प्रतिकर्षित करता है; यानी,आवश्यक वोल्टेज बढ़ाता है। लेकिन अगर पास में एक अन्य सुचालक है, और अगर उस पर एक ऋणात्मक आवेश है, दूसरे धनात्मक आवेश को प्रतिकर्षित करने वाले धनात्मक चालक का विद्युत क्षेत्र कमजोर हो जाता है (दूसरा धनात्मक आवेश भी ऋणात्मक आवेश के आकर्षण बल को महसूस करता है)। इसलिए एक ऋणात्मक आवेश वाले दूसरे सुचालक के साथ दूसरे कंडक्टर के कारण, पहले से ही धनात्मक आवेश किए गए पहले कंडक्टर पर धनात्मक आवेश करना आसान हो जाता है, और इसके विपरीत;जिससे आवश्यक वोल्टेज को कम किया जा सके। <br>एक मात्रात्मक उदाहरण के रूप में दो समानांतर प्लेटों से निर्मित एक संधारित्र की धारिता पर विचार करें, जब दोनों प्लेटों का क्षेत्रफल A है जो कि एक दूरी d द्वारा अलग किए गए हैं। यदि d पर्याप्त रूप से ''A'' के सबसे छोटे कॉर्ड के संबंध में छोटा है, तो सटीकता के उच्च स्तर के लिए: | ||

<br>एक मात्रात्मक उदाहरण के रूप में दो समानांतर प्लेटों से निर्मित एक संधारित्र की धारिता पर विचार करें, जब दोनों प्लेटों का क्षेत्रफल A है जो कि एक दूरी d द्वारा अलग किए गए हैं। यदि d पर्याप्त रूप से ''A'' के सबसे छोटे कॉर्ड के संबंध में छोटा है, तो सटीकता के उच्च स्तर के लिए: | |||

<math display="block">\ C=\varepsilon\frac{A}{d}</math>ध्यान दें कि | <math display="block">\ C=\varepsilon\frac{A}{d}</math>ध्यान दें कि | ||

| Line 87: | Line 85: | ||

धारिता अतिव्यापन के क्षेत्र के लिए समानुपाती हैऔर संवाहक शीट के बीच के अंतर के व्युत्क्रमानुपाती है। धारिता जितनी अधिक होती है शीट एक दूसरे के उतनी करीब होती हैं। | धारिता अतिव्यापन के क्षेत्र के लिए समानुपाती हैऔर संवाहक शीट के बीच के अंतर के व्युत्क्रमानुपाती है। धारिता जितनी अधिक होती है शीट एक दूसरे के उतनी करीब होती हैं। | ||

समीकरण एक अच्छा सन्निकटन है यदि D प्लेटों के अन्य आयामों की तुलना में छोटा है, ताकि संधारित्र क्षेत्र में विद्युत क्षेत्र समान हो, और परिधि के चारों ओर तथाकथित '''''फ्रिंजिंग क्षेत्र''''' धारिता में केवल एक छोटा योगदान प्रदान करता है। | समीकरण एक अच्छा सन्निकटन है यदि D प्लेटों के अन्य आयामों की तुलना में छोटा है, ताकि संधारित्र क्षेत्र में विद्युत क्षेत्र समान हो, और परिधि के चारों ओर तथाकथित '''''फ्रिंजिंग क्षेत्र''''' धारिता में केवल एक छोटा योगदान प्रदान करता है। | ||

धारिता में संग्रहीत ऊर्जा के लिए उपरोक्त समीकरण के साथ धारिता के लिए समीकरण का संयोजन, एक फ्लैट-प्लेट संधारित्र के लिए संग्रहीत ऊर्जा है: | |||

<math display="block"> W_\text{stored} = \frac{1}{2} C V^2 = \frac{1}{2} \varepsilon_{0} \frac{A}{d} V^2.</math> | <math display="block"> W_\text{stored} = \frac{1}{2} C V^2 = \frac{1}{2} \varepsilon_{0} \frac{A}{d} V^2.</math> | ||

जहां W ऊर्जा है, जूल्स में; C धारिता है, फैराड्स में;और V वोल्ट में वोल्टेज है। | जहां W ऊर्जा है, जूल्स में; C धारिता है, फैराड्स में;और V वोल्ट में वोल्टेज है। | ||

Revision as of 20:53, 14 October 2022

सामान्य प्रतीक | C |

|---|---|

| Si इकाई | farad |

अन्य इकाइयां | μF, nF, pF |

| SI आधार इकाइयाँ में | F = A2 s4 kg−1 m−2 |

अन्य मात्राओं से व्युत्पत्तियां | C = charge / voltage |

| आयाम | M−1 L−2 T4 I2 |

| Articles about |

| Electromagnetism |

|---|

|

कैपेसिटेंस विद्युत कंडक्टर ( इलेक्ट्रिक कंडक्टर) पर संग्रहीत आवेश की मात्रा और विद्युत क्षमता में अंतर का अनुपात है। धारिता के दो प्रकार है जो आपस में एक दूसरे से सम्बंधित है: सेल्फ कैपेसिटेंस (आत्म धारिता) और म्यूचुअल कैपेसिटेंस (पारस्परिक धारिता)।[1]: 237–238 कोई भी वस्तु जिसे विद्युत रूप से चार्ज किया जा सकता है वह आत्म धारिता प्रदर्शित करता है। इस मामले में वस्तु और जमीन के बीच संभावित विद्युत अंतर मापा जाता है। पारस्परिक धारिता को दो कंडक्टरों के बीच मापा जाता है,और यह संधारित्र के संचालन में विशेष रूप से महत्वपूर्ण है, (प्रतिरोधों और प्रारंभ करनेवाला ों के साथ) इस उद्देश्य के लिए एक प्राथमिक रैखिक इलेक्ट्रॉनिक घटक के रूप में उपकरण डिज़ाइन किया गया है। संधारित्र के संचालन को समझने के लिए पारस्परिक धारिता की धारणा विशेष रूप से महत्वपूर्ण है। एक विशिष्ट संधारित्र में, दो कंडक्टरों का उपयोग इलेक्ट्रिक चार्ज को अलग करने के लिए किया जाता है, जिसमें एक कंडक्टर को धनात्मक रूप से चार्ज किया जाता है और दूसरा ऋणात्मक रूप से चार्ज किया जाता है, लेकिन सिस्टम का कुल चार्ज शून्य होता है।

धारिता केवल संधारित्र के डिजाइन की ज्यामिति का एक कार्य है, उदाहरण के लिए, प्लेटों का विरोधी सतह क्षेत्र और उनके बीच की दूरी, और प्लेटों के बीच परावैद्युत पदार्थ की पारगम्यता। कई परावैद्युत पदार्थ के लिए, पारगम्यता और धारिता, कंडक्टरों के बीच संभावित विद्युत अंतर और उन पर उपस्थित कुल चार्ज से स्वतंत्र है।

कैपेसिटेंस की एसआई इकाई अंग्रेजी भौतिक वैज्ञानिकमाइकल फैराडे के नाम पर फैराड (प्रतीक: एफ) है। 1 फैराड कैपेसिटर, जब 1 कूलम्ब विद्युत आवेश के साथ आरोपित किया जाता है, तो इसकी प्लेटों के बीच 1 वोल्ट का संभावित अंतर होता है।[2] धारिता के वुत्पन्न को इलास्टेंस कहा जाता है।

स्व समाई(आत्म धारिता)

विद्युत परिपथ में, धारिता शब्द आमतौर पर दो आसन्न कंडक्टरों के बीच पारस्परिक समाई के लिए एक आशुलिपि (शॉर्टहैंड) है, जैसे कि एक संधारित्र की दो प्लेटें। हालांकि, एक पृथक संधारित्र के लिए, सेल्फ कैपेसिटेंस (आत्म धारिता) नामक एक संपत्ति भी मौजूद है, जो कि विद्युत आवेश की मात्रा है जिसे एक अलग संधारित्र में जोड़ा जाना चाहिए ताकि इसकी विद्युत क्षमता को एक इकाई (यानी एक वोल्ट, अधिकांश माप प्रणालियों में) तक बढ़ाया जा सके।[3] इस विभव के लिए संदर्भ बिंदु इस क्षेत्र के अंदर केंद्रित संधारित्र के साथ अनंत त्रिज्या का एक सैद्धांतिक खोखला क्षेत्र है।

गणितीय रूप से, एक संधारित्र की सेल्फ कैपेसिटेंस (आत्म धारिता) को परिभाषित किया गया है

- q कंडक्टर पर आयोजित शुल्क है,

- विद्युत क्षमता है,

- σ सतह आवेश घनत्व है।

- dS कंडक्टर की सतह पर क्षेत्र का एक असीम तत्व है,

- r कंडक्टर पर एक निश्चित बिंदु m से ds तक लंबाई है

- वैक्यूम पारगम्यता है

इस पद्धति का उपयोग करते हुए, सेल्फ कैपेसिटेंस (आत्म धारिता) के एक संचालन क्षेत्र की त्रिज्या R है:[4]

- एक वैन डी ग्राफ जनरेटर की शीर्ष प्लेट के लिए,आमतौर पर एक वृत्त त्रिज्या में 20 सेमी: 22.24 पीएफ,

- ग्रह पृथ्वी: लगभग 710 µf।[5]

एक विद्युत चुम्बकीय कुंडल की अंतर-घुमावदार धारिता को कभी-कभी आत्म धारिता कहा जाता है,[6] लेकिन यह एक अलग घटना है।यह वास्तव में कॉइल के अलग-अलग मोड़ के बीच पारस्परिक धारिता है और आवारा, या परजीवी समाई (धारिता) का एक रूप है। यह आत्म धारिता उच्च आवृत्तियों के लिए महत्वपूर्ण विचार है: यह कॉइल के विद्युत प्रतिबाधा को बदलता है और समानांतर विद्युत अनुनाद को जन्म देता है। कई अनुप्रयोगों में यह एक अवांछनीय प्रभाव है और परिपथ के सही संचालन के लिए एक ऊपरी आवृत्ति सीमा निर्धारित करता है।[citation needed]

म्यूचुअल कैपेसिटेंस (पारस्परिक धारिता)

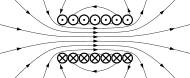

ये ,सामान्य रूप एक समानांतर-प्लेट संधारित्र है, जिसमें दो प्रवाहकीय प्लेटें होती हैं,और ये दोनों प्लेट एक दूसरे के ऊपर रखीं होती हैं,आमतौर पर प्लेट एक दूसरे के ऊपर ऐसे रखीं होती है जैसे डाइइलेक्ट्रिक सामग्री उन दोनों प्लेट के बीच में रखा हो। एक समानांतर प्लेट संधारित्र में,धारिता संधारित्र प्लेटों के सतह क्षेत्र के समानुपाती और और दो प्लेट के बीच की दूरी के व्युत्क्रमानुपाती होता है।

यदि प्लेटों पर आवेश +Q और, -Q हैं, और V प्लेटों के बीच वोल्टेज देता है, तो धारिता को C द्वारा प्रदर्शित किया जाता है।

एक संधारित्र में संग्रहीत ऊर्जा W के समाकलन द्वारा प्राप्त किया जाता है:

कैपेसिटेंस मैट्रिक्स (धारिता मैट्रिक्स)

उपरोक्त चर्चा दो संचालन प्लेटों के मामले तक सीमित है, हालांकि मनमानी आकार और आकृति की है। ये परिभाषा तब लागू नहीं है जब दो से अधिक चार्ज किए गए प्लेटें होती हैं , या जब दो प्लेटों पर नेट चार्ज शून्य नहीं होता है। इस मामले को संभालने के लिए, मैक्सवेल ने अपने संभावित गुणांक पेश किए। यदि तीन (लगभग आदर्श) कंडक्टरों को आवेश , दिया जाता है तो कंडक्टर 1 पर दिया गया वोल्टेज है:

गुणांकों का संग्रह धारिता मैट्रिक्स के रूप में जाना जाता है,[8][9][10] और यह इलास्टेंस मैट्रिक्स का उलटा है।

कैपेसिटर (संधारित्र)

विद्युत परिपथ में उपयोग किए जाने वाले ज्यादातर संधारित्र की धारिता आम तौर पर फैराड की तुलना में बहुत छोटी है। आज सबसे ज्यादा आम उपयोग में आने वाली धारिता की उपइकाई सूक्ष्म फ़ारड (µf), नैनो फ़ारड (nf), पिको- फराड (pf), और, सूक्ष्मपरिपथ मे, स्त्री फारड (Ff) हैं। हालांकि, विशेष रूप से बनाए गए सुपर कैपेसिटर बहुत बड़े हो सकते हैं (जितना सैकड़ों फैराड्स), और परजीवी कैपेसिटिव तत्व एक फेमटोफराड से कम हो सकते हैं। अतीत में, पुराने ऐतिहासिक पाठ में वैकल्पिक उपइकाई का उपयोग किया गया था; माइक्रोफारड के लिए (एमएफ) और (एमएफडी); "mmf", "mmfd", पिको- फराड "pfd", (PF) के लिए; लेकिन अब यह अप्रचलित माना जाता है।[11][12]

यदि संधारित्र की ज्यामिति और संधारित्रों के बीच इन्सुलेटर के परावैद्युत गुण ज्ञात हों तो धारिता की गणना की जा सकती है।

जब एक धनात्मक आवेश एक सुचालक को दिया जाता है, यह आवेश एक विद्युत क्षेत्र बनाता है, जोकि सुचालक पर स्थानांतरित किए जाने वाले किसी भी अन्य धनात्मक आवेश को प्रतिकर्षित करता है; यानी,आवश्यक वोल्टेज बढ़ाता है। लेकिन अगर पास में एक अन्य सुचालक है, और अगर उस पर एक ऋणात्मक आवेश है, दूसरे धनात्मक आवेश को प्रतिकर्षित करने वाले धनात्मक चालक का विद्युत क्षेत्र कमजोर हो जाता है (दूसरा धनात्मक आवेश भी ऋणात्मक आवेश के आकर्षण बल को महसूस करता है)। इसलिए एक ऋणात्मक आवेश वाले दूसरे सुचालक के साथ दूसरे कंडक्टर के कारण, पहले से ही धनात्मक आवेश किए गए पहले कंडक्टर पर धनात्मक आवेश करना आसान हो जाता है, और इसके विपरीत;जिससे आवश्यक वोल्टेज को कम किया जा सके।

एक मात्रात्मक उदाहरण के रूप में दो समानांतर प्लेटों से निर्मित एक संधारित्र की धारिता पर विचार करें, जब दोनों प्लेटों का क्षेत्रफल A है जो कि एक दूरी d द्वारा अलग किए गए हैं। यदि d पर्याप्त रूप से A के सबसे छोटे कॉर्ड के संबंध में छोटा है, तो सटीकता के उच्च स्तर के लिए:

जहाँ पे

- C धारिता है, फैराड्स में;

- A दो प्लेटों के ओवरलैप का क्षेत्र है, वर्ग मीटर में;

- ε0 वैक्यूम पारगम्यता है (ε0 ≈ 8.854×10−12 F⋅m−1);

- εr प्लेटों के बीच सामग्री के सापेक्ष पारगम्यता (परावैद्युत नियतांक) εr = 1 हवा के लिए);तथा

- D प्लेटों के बीच बीच की दूरी है,मीटर में;

धारिता अतिव्यापन के क्षेत्र के लिए समानुपाती हैऔर संवाहक शीट के बीच के अंतर के व्युत्क्रमानुपाती है। धारिता जितनी अधिक होती है शीट एक दूसरे के उतनी करीब होती हैं। समीकरण एक अच्छा सन्निकटन है यदि D प्लेटों के अन्य आयामों की तुलना में छोटा है, ताकि संधारित्र क्षेत्र में विद्युत क्षेत्र समान हो, और परिधि के चारों ओर तथाकथित फ्रिंजिंग क्षेत्र धारिता में केवल एक छोटा योगदान प्रदान करता है।

धारिता में संग्रहीत ऊर्जा के लिए उपरोक्त समीकरण के साथ धारिता के लिए समीकरण का संयोजन, एक फ्लैट-प्लेट संधारित्र के लिए संग्रहीत ऊर्जा है:

आवारा समाई

कोई भी दो पास का कंडक्टर एक संधारित्र के रूप में कार्य कर सकते हैं, हालांकि कैपेसिटेंस तब तक छोटा होता है जब तक कि कंडक्टर लंबी दूरी के लिए या एक बड़े क्षेत्र में एक साथ करीब न हों। यह (अक्सर अवांछित) धारिता को परजीवी या आवारा कहा जाता है। आवारा कैपेसिटेंस संकेतों को अन्यथा पृथक सर्किट (क्रॉसस्टॉक (इलेक्ट्रॉनिक्स) नामक एक प्रभाव) के बीच लीक करने की अनुमति दे सकता है, और यह उच्च आवृत्ति पर सर्किट के उचित कामकाज के लिए एक सीमित कारक हो सकता है। Any two adjacent conductors can function as a capacitor, though the capacitance is small unless the conductors are close together for long distances or over a large area. This (often unwanted) capacitance is called parasitic or "stray capacitance". Stray capacitance can allow signals to leak between otherwise isolated circuits (an effect called crosstalk), and it can be a limiting factor for proper functioning of circuits at high frequency.

एम्पलीफायर सर्किट में इनपुट और आउटपुट के बीच आवारा समाई परेशानी भरा हो सकता है क्योंकि यह फीडबैक#इलेक्ट्रॉनिक इंजीनियरिंग के लिए एक पथ बना सकता है, जिससे एम्पलीफायर में अस्थिरता और परजीवी दोलन हो सकता है। यह अक्सर विश्लेषणात्मक उद्देश्यों के लिए एक इनपुट-टू-ग्राउंड कैपेसिटेंस और एक आउटपुट-टू-ग्राउंड कैपेसिटेंस के संयोजन के साथ इस समाई को बदलने के लिए सुविधाजनक होता है; मूल कॉन्फ़िगरेशन-इनपुट-टू-आउटपुट कैपेसिटेंस सहित-को अक्सर पीआई-कॉन्फ़िगरेशन के रूप में संदर्भित किया जाता है। इस प्रतिस्थापन को प्रभावित करने के लिए मिलर के प्रमेय का उपयोग किया जा सकता है: यह बताता है कि, यदि दो नोड्स का लाभ अनुपात 1/k है, तो Z को दो नोड्स को जोड़ने के एक विद्युत प्रतिबाधा को z/(1 & nbsp; & nbsp; k के साथ बदला जा सकता है; ) पहले नोड और जमीन और एक kz/(k & nbsp; - & nbsp; 1) के बीच प्रतिबाधा दूसरे नोड और जमीन के बीच प्रतिबाधा। चूंकि प्रतिबाधा समाई के साथ विपरीत रूप से भिन्न होती है, इंटर्नोड कैपेसिटेंस, सी, को केसी की एक कैपेसिटेंस द्वारा इनपुट से जमीन तक और (k & nbsp; - & nbsp; 1) C/K से आउटपुट से जमीन तक। जब इनपुट-टू-आउटपुट लाभ बहुत बड़ा होता है, तो समतुल्य इनपुट-टू-ग्राउंड प्रतिबाधा बहुत कम होता है जबकि आउटपुट-टू-ग्राउंड प्रतिबाधा अनिवार्य रूप से मूल (इनपुट-टू-आउटपुट) प्रतिबाधा के बराबर होता है।

साधारण आकृतियों के साथ कंडक्टरों की समाई

Laplace समीकरण को हल करने के लिए एक सिस्टम राशि की समाई की गणना2 φ & nbsp; = & nbsp; 0 3-स्पेस में एम्बेडेड कंडक्टरों की 2-आयामी सतह पर एक निरंतर क्षमता के साथ।यह समरूपता द्वारा सरल है।अधिक जटिल मामलों में प्राथमिक कार्यों के संदर्भ में कोई समाधान नहीं है।

विमान स्थितियों के लिए, विश्लेषणात्मक कार्यों का उपयोग एक दूसरे को विभिन्न ज्यामिति को मैप करने के लिए किया जा सकता है।श्वार्ज़ -क्रिस्टोफेल मैपिंग भी देखें।

| Type | Capacitance | Comment |

|---|---|---|

| Parallel-plate capacitor | ε: Permittivity | |

| Concentric cylinders |

ε: Permittivity | |

| Eccentric cylinders[13] |

ε: Permittivity | |

| Pair of parallel wires[14] |

| |

| Wire parallel to wall[14] | a: Wire radius d: Distance, d > a ℓ: Wire length | |

| Two parallel coplanar strips[15] |

d: Distance w1, w2: Strip width km: d/(2wm+d) k2: k1k2 | |

| Concentric spheres |

ε: Permittivity | |

| Two spheres, equal radius[16][17] |

a: Radius d: Distance, d > 2a D = d/2a, D > 1 γ: Euler's constant | |

| Sphere in front of wall[16] | : Radius : Distance, | |

| Sphere | : Radius | |

| Circular disc[18] | : Radius | |

| Thin straight wire, finite length[19][20][21] |

: Wire radius : Length |

ऊर्जा भंडारण

संधारित्र में संग्रहीत ऊर्जा (जूल में मापी गई) संधारित्र में आरोपों को धकेलने के लिए आवश्यक कार्य के बराबर है, अर्थात इसे चार्ज करने के लिए।कैपेसिटेंस सी के एक संधारित्र पर विचार करें, एक प्लेट पर एक चार्ज +क्यू और दूसरे पर the क्यू आयोजित करें।संभावित अंतर के खिलाफ एक प्लेट से दूसरी प्लेट में चार्ज DQ का एक छोटा तत्व ले जाना V = q/C काम की आवश्यकता है DW:

एक संधारित्र में संग्रहीत ऊर्जा इस समीकरण के अभिन्न अंग द्वारा पाई जाती है।एक अपरिवर्तित समाई के साथ शुरू (q = 0) और एक प्लेट से दूसरी प्लेट तक चलती चार्ज जब तक प्लेटों में चार्ज +क्यू न हो और way क्यू को काम की आवश्यकता होती है:

नैनोस्केल सिस्टम

क्वांटम डॉट्स जैसे नैनोस्केल ढांकता हुआ कैपेसिटर की समाई बड़े कैपेसिटर के पारंपरिक योगों से भिन्न हो सकती है।विशेष रूप से, पारंपरिक कैपेसिटर में इलेक्ट्रॉनों द्वारा अनुभव किए गए इलेक्ट्रोस्टैटिक संभावित अंतर को पारंपरिक कैपेसिटर में मौजूद इलेक्ट्रॉनों की सांख्यिकीय रूप से बड़ी संख्या के अलावा धातु इलेक्ट्रोड के आकार और आकार द्वारा स्थानिक रूप से अच्छी तरह से परिभाषित और तय किया जाता है।नैनोस्केल कैपेसिटर में, हालांकि, इलेक्ट्रॉनों द्वारा अनुभव की जाने वाली इलेक्ट्रोस्टैटिक क्षमता सभी इलेक्ट्रॉनों की संख्या और स्थानों द्वारा निर्धारित की जाती है जो डिवाइस के इलेक्ट्रॉनिक गुणों में योगदान करते हैं।ऐसे उपकरणों में, इलेक्ट्रॉनों की संख्या बहुत कम हो सकती है, इसलिए डिवाइस के भीतर सुसंगत सतहों का परिणामी स्थानिक वितरण अत्यधिक जटिल है।

सिंगल-इलेक्ट्रॉन डिवाइस

एक जुड़े, या बंद, एकल-इलेक्ट्रॉन डिवाइस की समाई एक असंबद्ध, या खुले, एकल-इलेक्ट्रॉन डिवाइस की समाई से दोगुनी है।[22] इस तथ्य को एकल-इलेक्ट्रॉन डिवाइस में संग्रहीत ऊर्जा के लिए अधिक मौलिक रूप से पता लगाया जा सकता है, जिनके प्रत्यक्ष ध्रुवीकरण इंटरैक्शन ऊर्जा को इलेक्ट्रॉन की उपस्थिति और राशि की उपस्थिति के कारण डिवाइस पर ध्रुवीकृत आवेश के साथ इलेक्ट्रॉन की बातचीत में समान रूप से विभाजित किया जा सकता है।डिवाइस पर ध्रुवीकृत चार्ज बनाने के लिए आवश्यक संभावित ऊर्जा (इलेक्ट्रॉन के कारण क्षमता के साथ डिवाइस की ढांकता हुआ सामग्री में शुल्क की बातचीत)।[23]

कुछ-इलेक्ट्रॉन डिवाइस

कुछ-इलेक्ट्रॉन डिवाइस के एक क्वांटम कैपेसिटेंस की व्युत्पत्ति में N कण प्रणाली की थर्मोडायनामिक रासायनिक क्षमता शामिल है

हालांकि, विशुद्ध रूप से शास्त्रीय इलेक्ट्रोस्टैटिक इंटरैक्शन के ढांचे के भीतर, 1/2 के कारक की उपस्थिति पारंपरिक सूत्रीकरण में एकीकरण का परिणाम है,

स्पष्ट गणितीय अंतर को संभावित ऊर्जा के रूप में अधिक मौलिक रूप से समझा जाता है, , एक पृथक डिवाइस (सेल्फ-कैपेसिटेंस) दो बार है जो कम सीमा n = 1 में एक जुड़े डिवाइस में संग्रहीत है।जैसे -जैसे n बढ़ता है, .[23]इस प्रकार, समाई की सामान्य अभिव्यक्ति है

इलेक्ट्रॉनिक और अर्धचालक उपकरणों में समाई

इलेक्ट्रॉनिक और अर्धचालक उपकरणों में, टर्मिनलों के बीच क्षणिक या आवृत्ति-निर्भर धारा में चालन और विस्थापन दोनों घटक होते हैं। वाहक धारा आवेश वाहक आयन (इलेक्ट्रॉनों, होल या कोटर, आयनों, आदि) से संबंधित है, जबकि विस्थापन धारा या समय के साथ परिवर्तित हो रहे विद्युत क्षेत्र के कारण होता है। वाहक परिवहन विद्युत क्षेत्रों से और कई भौतिक घटनाओं से प्रभावित होता है-जैसे कि वाहक बहाव और प्रसार, ट्रैपिंग, इंजेक्शन, संपर्क-संबंधित प्रभाव, प्रभाव आयनीकरण, आदि। परिणामस्वरूप, डिवाइस प्रवेश आवृत्ति-निर्भर है,और एक सामान्य है, और समाई के लिए एक साधारण इलेक्ट्रोस्टैटिक सूत्र लागू नहीं है। धारिता की एक अधिक सामान्य परिभाषा, इलेक्ट्रोस्टैटिक फॉर्मूला को शामिल करना, है:[26]

सामान्य तौर पर, धारिता आवृत्ति का एक फलन है। उच्च आवृत्तियों पर, कैपेसिटेंस एक निरंतर मान ज्यामितीय समाई के बराबर,तक पहुंचता है, डिवाइस में टर्मिनलों की ज्यामिति और परावैद्युत सामग्री द्वारा निर्धारित किया जाता है। स्टीवन लक्स द्वारा प्रस्तुत एक पेपर[26]कैपेसिटेंस गणना के लिए संख्यात्मक तकनीकों की समीक्षा प्रस्तुत करता है। विशेष रूप से,कैपेसिटेंस की गणना एक चरण-जैसे वोल्टेज उत्तेजना के जवाब में एक क्षणिक धारा के फूरियर रूपांतरण द्वारा की जा सकती है:

अर्धचालक उपकरणों में ऋणात्मक धारिता

आमतौर पर, अर्धचालक उपकरणों में धारिता धनात्मक है। हालांकि, कुछ उपकरणों में और कुछ शर्तों (तापमान, लागू वोल्टेज,आवृत्ति,आदि) के तहत, धारिता ऋणात्मक हो सकती है। एक चरण-समान उत्तेजना के जवाब में क्षणिक धारा के गैर-मोनोटोनिक व्यवहार को ऋणात्मक धारिता के तंत्र के रूप में प्रस्तावित किया गया है।[27] कई अलग -अलग प्रकार के अर्धचालक उपकरणों में ऋणात्मक धारिता का प्रदर्शन और पता लगाया गया है।[28]

कैपेसिटेंस (धारिता) क मापन

एक कैपेसिटेंस मीटर इलेक्ट्रॉनिक परीक्षण उपकरणों का एक टुकड़ा है जिसका उपयोग धारिता को मापने के लिए किया जाता है, मुख्य रूप से असतत कैपेसिटर का। अधिकांश उद्देश्यों के लिए और ज्यादातर मामलों में संधारित्र को विद्युत सर्किट (परिपथ) से डिस्कनेक्ट किया जाना चाहिए।

कई डीवीएम (डिजिटल वोल्टमीटर) में एक धारिता मापने वाला फ़ंक्शन होता है। ये आमतौर पर एक ज्ञात विद्युत प्रवाह के साथ परीक्षण के तहत डिवाइस को चार्ज और डिस्चार्ज करके और परिणामस्वरूप वोल्टेज की वृद्धि दर को मापते हैं; धारिता जितनी ज्यादा होगी वृद्धि की दर उतनी कम होगी। डीवीएम आमतौर पर फैराड से कुछ सौ माइक्रोफारड्स तक धारिता को माप सकते हैं, लेकिन व्यापक सीमाएं असामान्य नहीं हैं। परीक्षण के तहत डिवाइस के माध्यम से एक ज्ञात उच्च-आवृत्ति प्रत्यावर्ती धारा को भेज करके और इसके पार परिणामी वोल्टेज को मापने के लिए धारिता को मापना भी संभव है (ध्रुवीकृत धारिता के लिए काम नहीं करता है)।

अधिक परिष्कृत उपकरण अन्य तकनीकों का उपयोग करते हैं जैसे कि कैपेसिटर-अंडर-टेस्ट को पुल परिपथ में सम्मिलित करना। पुल में अन्य पैरों के मान को अलग करके (ताकि पुल को संतुलन में लाया जा सके), अज्ञात संधारित्र का मान निर्धारित किया जाता है। धारिता को मापने के अप्रत्यक्ष उपयोग की यह विधि अधिक सटीकता सुनिश्चित करती चार टर्मिनल सेंसिंग और अन्य सावधान डिजाइन तकनीकों के उपयोग के माध्यम से, ये उपकरण आमतौर पर पिकोफारड्स से लेकर फैराड तक की सीमा से अधिक संधारित्र को माप सकते हैं।

यह भी देखें

- कैपेसिटिव विस्थापन संवेदक

- एक सेट की क्षमता

- परिमाण समाई

- विद्युत चालकता

- विस्थापन वर्तमान

- Ampère का सर्कुलेटल कानून

- गॉस लॉ

- हाइड्रोलिक सादृश्य

- मैग्नेटोकैपेसिटेंस

- आरकेएम कोड

- Lcr मीटर

संदर्भ

- ↑ Harrington, Roger F. (2003). Introduction to Electromagnetic Engineering (1st ed.). Dover Publications. p. 43. ISBN 0-486-43241-6.

- ↑ "Definition of 'farad'". Collins.

- ↑ William D. Greason (1992). Electrostatic discharge in electronics. Research Studies Press. p. 48. ISBN 978-0-86380-136-5.

- ↑ Lecture notes; University of New South Wales

- ↑ Tipler, Paul; Mosca, Gene (2004). Physics for Scientists and Engineers (5th ed.). Macmillan. p. 752. ISBN 978-0-7167-0810-0.

- ↑ Massarini, A.; Kazimierczuk, M.K. (1997). "Self capacitance of inductors". IEEE Transactions on Power Electronics. 12 (4): 671–676. Bibcode:1997ITPE...12..671M. CiteSeerX 10.1.1.205.7356. doi:10.1109/63.602562: example of the use of the term 'self capacitance'.

{{cite journal}}: CS1 maint: postscript (link) - ↑ Jackson, John David (1999). Classical Electrodynamic (3rd ed.). John Wiley & Sons. p. 43. ISBN 978-0-471-30932-1.

- ↑ Maxwell, James (1873). "3". A treatise on electricity and magnetism. Vol. 1. Clarendon Press. p. 88ff.

- ↑ "Capacitance : Charge as a Function of Voltage". Av8n.com. Retrieved 20 September 2010.

- ↑ Smolić, Ivica; Klajn, Bruno (2021). "Capacitance matrix revisited". Progress in Electromagnetics Research B. 92: 1–18. arXiv:2007.10251. doi:10.2528/PIERB21011501. Retrieved 4 May 2021.

- ↑ "Capacitor MF-MMFD Conversion Chart". Just Radios.

- ↑ Fundamentals of Electronics. Vol. 1b — Basic Electricity — Alternating Current. Bureau of Naval Personnel. 1965. p. 197.

- ↑ Dawes, Chester L. (1973). "Capacitance and Potential Gradients of Eccentric Cylindrical Condensers". Physics. 4 (2): 81–85. doi:10.1063/1.1745162.

- ↑ 14.0 14.1 Jackson, J. D. (1975). Classical Electrodynamics. Wiley. p. 80.

- ↑ Binns; Lawrenson (1973). Analysis and computation of electric and magnetic field problems. Pergamon Press. ISBN 978-0-08-016638-4.

- ↑ 16.0 16.1 Maxwell, J. C. (1873). A Treatise on Electricity and Magnetism. Dover. p. 266ff. ISBN 978-0-486-60637-8.

- ↑ Rawlins, A. D. (1985). "Note on the Capacitance of Two Closely Separated Spheres". IMA Journal of Applied Mathematics. 34 (1): 119–120. doi:10.1093/imamat/34.1.119.

- ↑ Jackson, J. D. (1975). Classical Electrodynamics. Wiley. p. 128, problem 3.3.

{{cite book}}: CS1 maint: postscript (link) - ↑ Maxwell, J. C. (1878). "On the electrical capacity of a long narrow cylinder and of a disk of sensible thickness". Proc. London Math. Soc. IX: 94–101. doi:10.1112/plms/s1-9.1.94.

- ↑ Vainshtein, L. A. (1962). "Static boundary problems for a hollow cylinder of finite length. III Approximate formulas". Zh. Tekh. Fiz. 32: 1165–1173.

- ↑ Jackson, J. D. (2000). "Charge density on thin straight wire, revisited". Am. J. Phys. 68 (9): 789–799. Bibcode:2000AmJPh..68..789J. doi:10.1119/1.1302908.

- ↑ Raphael Tsu (2011). Superlattice to Nanoelectronics. Elsevier. pp. 312–315. ISBN 978-0-08-096813-1.

- ↑ 23.0 23.1 T. LaFave Jr. (2011). "Discrete charge dielectric model of electrostatic energy". J. Electrostatics. 69 (6): 414–418. arXiv:1203.3798. doi:10.1016/j.elstat.2011.06.006. S2CID 94822190.

- ↑ G. J. Iafrate; K. Hess; J. B. Krieger; M. Macucci (1995). "Capacitive nature of atomic-sized structures". Phys. Rev. B. 52 (15): 10737–10739. Bibcode:1995PhRvB..5210737I. doi:10.1103/physrevb.52.10737. PMID 9980157.

- ↑ T. LaFave Jr; R. Tsu (March–April 2008). "Capacitance: A property of nanoscale materials based on spatial symmetry of discrete electrons" (PDF). Microelectronics Journal. 39 (3–4): 617–623. doi:10.1016/j.mejo.2007.07.105. Archived from the original (PDF) on 22 February 2014. Retrieved 12 February 2014.

- ↑ 26.0 26.1 Laux, S.E. (October 1985). "Techniques for small-signal analysis of semiconductor devices". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 4 (4): 472–481. doi:10.1109/TCAD.1985.1270145. S2CID 13058472.

- ↑ Jonscher, A.K. (1986). "The physical origin of negative capacitance". J. Chem. Soc. Faraday Trans. II. 82: 75–81. doi:10.1039/F29868200075.

- ↑ Ershov, M.; Liu, H.C.; Li, L.; Buchanan, M.; Wasilewski, Z.R.; Jonscher, A.K. (October 1998). "Negative capacitance effect in semiconductor devices". IEEE Trans. Electron Devices. 45 (10): 2196–2206. arXiv:cond-mat/9806145. Bibcode:1998ITED...45.2196E. doi:10.1109/16.725254. S2CID 204925581.

इस पृष्ठ में गुम आंतरिक लिंक की सूची

- विद्युतीय संभाव्यता

- अंगुली की छाप

- रैखिक परिपथ

- तथा

- अवरोध

- परावैद्युतांक

- धरती

- विद्युत चुम्बकीय कॉइल

- विद्युत प्रतिध्वनि

- विद्युत प्रवाह

- क्षमता के गुणांक

- लाप्लास समीकरण

- जौल

- प्रत्यावर्ती धारा

- इलेक्ट्रॉनिक परीक्षण उपस्कर

- परीक्षण के अंतर्गत उपकरण

- उच्च आवृत्ति

- एलसीआर मीटर

अग्रिम पठन

- Tipler, Paul (1998). Physics for Scientists and Engineers: Vol. 2: Electricity and Magnetism, Light (4th ed.). W. H. Freeman. ISBN 1-57259-492-6

- Serway, Raymond; Jewett, John (2003). Physics for Scientists and Engineers (6th ed.). Brooks Cole. ISBN 0-534-40842-7

- Saslow, Wayne M.(2002). Electricity, Magnetism, and Light. Thomson Learning. ISBN 0-12-619455-6. See Chapter 8, and especially pp. 255–259 for coefficients of potential.

]