कैस्कोड: Difference between revisions

No edit summary |

No edit summary |

||

| Line 21: | Line 21: | ||

</ref> | </ref> | ||

एकल प्रवर्धक चरण की तुलना में, इस संयोजन में निम्नलिखित विशेषताओं में से एक या अधिक हो सकते | एकल प्रवर्धक चरण की तुलना में, इस संयोजन में निम्नलिखित विशेषताओं में से एक या अधिक हो सकते हैं l उच्च इनपुट-आउटपुट , उच्च इनपुट प्रतिबाधा, उच्च [[आउटपुट प्रतिबाधा]], उच्च [[बैंडविड्थ (सिग्नल प्रोसेसिंग)|बैंडविड्थ (संकेत प्रोसेसिंग)]] होता है। | ||

आधुनिक परिपथ में, कैस्कोड अधिकांशतः दो [[ट्रांजिस्टर]] ([[द्विध्रुवी जंक्शन ट्रांजिस्टर]] [[ फील्ड इफ़ेक्ट ट्रांजिस्टर |फील्ड इफ़ेक्ट ट्रांजिस्टर]] ) से बना होता है | आधुनिक परिपथ में, कैस्कोड अधिकांशतः दो [[ट्रांजिस्टर]] ([[द्विध्रुवी जंक्शन ट्रांजिस्टर]] [[ फील्ड इफ़ेक्ट ट्रांजिस्टर |फील्ड इफ़ेक्ट ट्रांजिस्टर]] ) से बना होता है | जिसमें से [[सामान्य उत्सर्जक]] या [[सामान्य स्रोत]] के रूप में काम करता है और दूसरा [[सामान्य आधार]] या सामान्य गेट के रूप में होता है। | ||

कैस्कोड इनपुट-आउटपुट (रिवर्स ट्रांसमिशन को कम करता है) में सुधार करता है क्योंकि आउटपुट से इनपुट तक कोई सीधा युग्मन नहीं होता है। यह [[मिलर प्रभाव]] को समाप्त करता है और इस प्रकार बहुत अधिक बैंडविड्थ में योगदान देता है। | कैस्कोड इनपुट-आउटपुट (रिवर्स ट्रांसमिशन को कम करता है) में सुधार करता है | क्योंकि आउटपुट से इनपुट तक कोई सीधा युग्मन नहीं होता है। यह [[मिलर प्रभाव]] को समाप्त करता है और इस प्रकार बहुत अधिक बैंडविड्थ में योगदान देता है। | ||

== इतिहास == | == इतिहास == | ||

कैसकोड (कभी-कभी कैसकोडिंग के लिए [[ क्रिया |क्रिया]] ) का उपयोग [[एनालॉग सर्किट|एनालॉग परिपथ]] प्रदर्शन में सुधार के लिए सामान्य विधि है | कैसकोड (कभी-कभी कैसकोडिंग के लिए [[ क्रिया |क्रिया]] ) का उपयोग [[एनालॉग सर्किट|एनालॉग परिपथ]] प्रदर्शन में सुधार के लिए सामान्य विधि है | जो [[ वेक्यूम - ट्यूब |वेक्यूम - ट्यूब]] और ट्रांजिस्टर दोनों पर प्रयुक्त होता है। [[वोल्टेज स्टेबलाइजर]] के आवेदन पर चर्चा में 1939 में [[फ्रेडरिक विंटन हंट]] और रोजर वेन हिकमैन द्वारा लिखे गए एक लेख में कैसकोड नाम गढ़ा गया था।<ref>{{cite journal|last1=Hunt|first1=Frederick Vinton|last2=Hickman|first2=Roger Wayne|title=इलेक्ट्रॉनिक वोल्टेज स्टेबलाइजर्स पर|journal=Review of Scientific Instruments|date=1939|volume=10|issue=1|pages=6|doi=10.1063/1.1751443|url=http://www.tubezone.net/pdf/diagrams/regulator.pdf|accessdate=20 March 2016}}</ref> उन्होंने [[ एक कलम के साथ |कलम के साथ]] के प्रतिस्थापन के रूप में दो [[ट्रायोड]] ( सामान्य [[कैथोड]] सेटअप के साथ पहला, सामान्य [[नियंत्रण ग्रिड]] वाला दूसरा) का कैस्केड प्रस्तावित किया, और इसलिए नाम को कैस्क (एडेड ट्रायोड एम्पलीफायर) का संक्षिप्त नाम माना जा सकता है। विशेषताओं के समान, किन्तु एकल पेंट) की तुलना में <ref>"Cathode Ray", "The Cascode and its Advantages for Band III Reception", ''Wireless World'', vol. 61, p. 397 (August 1955).</ref> कम ध्वनि और व्यापक बैंडविड्थ के कारण 'फ्रंट-एंड' या ट्यूनर के लिए प्रारंभिक टेलीविजन सेटों में कैस्कोड परिपथ नियोजित किए गए थे। | ||

== संचालन == | == संचालन == | ||

| Line 34: | Line 34: | ||

जैसा कि निचला एफईटी संचालित करता है | यह ऊपरी एफईटी के स्रोत वोल्टेज को बदलता है, और ऊपरी एफईटी इसके गेट और स्रोत के बीच परिवर्तित क्षमता के कारण संचालित होता है। | जैसा कि निचला एफईटी संचालित करता है | यह ऊपरी एफईटी के स्रोत वोल्टेज को बदलता है, और ऊपरी एफईटी इसके गेट और स्रोत के बीच परिवर्तित क्षमता के कारण संचालित होता है। | ||

इस परिपथ व्यवस्था का प्रमुख लाभ इनपुट (कम) एफईटी के आउटपुट टर्मिनल (नाली) के भार के रूप में ऊपरी क्षेत्र-प्रभाव ट्रांजिस्टर (एफईटी) की नियुक्ति से उत्पन्न है। क्योंकि संचालन आवृत्तियों पर ऊपरी एफईटी का गेट प्रभावी रूप से ग्राउंडेड होता है | ऊपरी एफईटी का स्रोत वोल्टेज (और इसलिए इनपुट ट्रांजिस्टर की नाली) संचालन के समय लगभग स्थिर वोल्टेज पर आयोजित होता है। दूसरे शब्दों में, ऊपरी एफईटी निचले एफईटी के लिए कम इनपुट प्रतिरोध प्रदर्शित करता हैl जिससे निचले एफईटी का वोल्टेज लाभ बहुत छोटा हो जाता हैl जो नाटकीय रूप से मिलर प्रभाव फीडबैक कैपेसिटेंस को निचले एफईटी के नाले से गेट तक कम कर देता है। वोल्टेज लाभ का यह हानि ऊपरी एफईटी द्वारा वसूल किया जाता है। इस प्रकार, ऊपरी ट्रांजिस्टर कम एफईटी को न्यूनतम | इस परिपथ व्यवस्था का प्रमुख लाभ इनपुट (कम) एफईटी के आउटपुट टर्मिनल (नाली) के भार के रूप में ऊपरी क्षेत्र-प्रभाव ट्रांजिस्टर (एफईटी) की नियुक्ति से उत्पन्न है। क्योंकि संचालन आवृत्तियों पर ऊपरी एफईटी का गेट प्रभावी रूप से ग्राउंडेड होता है | ऊपरी एफईटी का स्रोत वोल्टेज (और इसलिए इनपुट ट्रांजिस्टर की नाली) संचालन के समय लगभग स्थिर वोल्टेज पर आयोजित होता है। दूसरे शब्दों में, ऊपरी एफईटी निचले एफईटी के लिए कम इनपुट प्रतिरोध प्रदर्शित करता हैl जिससे निचले एफईटी का वोल्टेज लाभ बहुत छोटा हो जाता हैl जो नाटकीय रूप से मिलर प्रभाव फीडबैक कैपेसिटेंस को निचले एफईटी के नाले से गेट तक कम कर देता है। वोल्टेज लाभ का यह हानि ऊपरी एफईटी द्वारा वसूल किया जाता है। इस प्रकार, ऊपरी ट्रांजिस्टर कम एफईटी को न्यूनतम ऋणात्मक (मिलर) प्रतिक्रिया के साथ संचालित करने की अनुमति देता हैl जिससे इसकी बैंडविड्थ में सुधार होता है। | ||

ऊपरी एफईटी गेट विद्युत रूप से ग्राउंडेड है, इसलिए कैपेसिटेंस C<sub>dg</sub> का चार्ज और डिस्चार्ज,केवल R<sub>D</sub> , नाली और गेट के बीच से होकर जाता है और आउटपुट लोड (R<sub>out</sub> कहते हैं), और आवृत्ति प्रतिक्रिया केवल संबद्ध [[आरसी समय स्थिर| | ऊपरी एफईटी गेट विद्युत रूप से ग्राउंडेड है, इसलिए कैपेसिटेंस C<sub>dg</sub> का चार्ज और डिस्चार्ज,केवल R<sub>D</sub> , नाली और गेट के बीच से होकर जाता है और आउटपुट लोड (R<sub>out</sub> कहते हैं), और आवृत्ति प्रतिक्रिया केवल संबद्ध [[आरसी समय स्थिर|Rc समय स्थिर]] τ = C से ऊपर की आवृत्तियों के लिए प्रभावित होती है | R<sub>D</sub>//R<sub>out</sub>, अर्थात् f = 1/(2πτ), उच्च आवृत्ति क्योंकि C<sub>dg</sub>छोटा है अर्थात्, ऊपरी एफईटी गेट C<sub>dg</sub> के मिलर प्रवर्धन से ग्रस्त नहीं है | | ||

यदि ऊपरी एफईटी चरण अकेले अपने स्रोत को इनपुट नोड (अर्थात, कॉमन-गेट (CG) विन्यास) के रूप में उपयोग करके संचालित किया जाता है, तो इसमें अच्छा वोल्टेज लाभ और व्यापक बैंडविड्थ होगा। चूँकि, इसकी कम इनपुट प्रतिबाधा इसकी उपयोगिता को बहुत कम-प्रतिबाधा वोल्टेज चालकों तक सीमित कर देगी। उच्च इनपुट प्रतिबाधा में कम एफईटी परिणाम जोड़ने से, कैस्कोड चरण को उच्च-प्रतिबाधा स्रोत द्वारा संचालित करने की अनुमति मिलती है। | यदि ऊपरी एफईटी चरण अकेले अपने स्रोत को इनपुट नोड (अर्थात, कॉमन-गेट (CG) विन्यास) के रूप में उपयोग करके संचालित किया जाता है, तो इसमें अच्छा वोल्टेज लाभ और व्यापक बैंडविड्थ होगा। चूँकि, इसकी कम इनपुट प्रतिबाधा इसकी उपयोगिता को बहुत कम-प्रतिबाधा वोल्टेज चालकों तक सीमित कर देगी। उच्च इनपुट प्रतिबाधा में कम एफईटी परिणाम जोड़ने से, कैस्कोड चरण को उच्च-प्रतिबाधा स्रोत द्वारा संचालित करने की अनुमति मिलती है। | ||

| Line 43: | Line 43: | ||

=== स्थिरता === | === स्थिरता === | ||

कैस्कोड व्यवस्था भी बहुत स्थिर है। इसका आउटपुट विद्युत और भौतिक दोनों तरह से इनपुट से प्रभावी रूप से अलग होता है। निचले ट्रांजिस्टर में नाली और स्रोत दोनों पर लगभग स्थिर वोल्टेज होता है, और इस प्रकार इसके गेट में वापस फीड करने के लिए अनिवार्य रूप से कुछ भी नहीं होता है। ऊपरी ट्रांजिस्टर के गेट और स्रोत पर लगभग स्थिर वोल्टेज होता है। इस प्रकार, उन पर महत्वपूर्ण वोल्टेज वाले एकमात्र नोड इनपुट और आउटपुट हैं, और इन्हें लगभग स्थिर वोल्टेज के केंद्रीय सम्बन्ध और दो ट्रांजिस्टर की भौतिक दूरी से अलग किया जाता है। इस प्रकार व्यवहार में आउटपुट से इनपुट तक बहुत कम प्रतिक्रिया होती है। धातु परिरक्षण दोनों ट्रांजिस्टर के बीच आवश्यकता पड़ने पर और भी अधिक के लिए प्रभावी और | कैस्कोड व्यवस्था भी बहुत स्थिर है। इसका आउटपुट विद्युत और भौतिक दोनों तरह से इनपुट से प्रभावी रूप से अलग होता है। निचले ट्रांजिस्टर में नाली और स्रोत दोनों पर लगभग स्थिर वोल्टेज होता है, और इस प्रकार इसके गेट में वापस फीड करने के लिए अनिवार्य रूप से कुछ भी नहीं होता है। ऊपरी ट्रांजिस्टर के गेट और स्रोत पर लगभग स्थिर वोल्टेज होता है। इस प्रकार, उन पर महत्वपूर्ण वोल्टेज वाले एकमात्र नोड इनपुट और आउटपुट हैं, और इन्हें लगभग स्थिर वोल्टेज के केंद्रीय सम्बन्ध और दो ट्रांजिस्टर की भौतिक दूरी से अलग किया जाता है। इस प्रकार व्यवहार में आउटपुट से इनपुट तक बहुत कम प्रतिक्रिया होती है। धातु परिरक्षण दोनों ट्रांजिस्टर के बीच आवश्यकता पड़ने पर और भी अधिक के लिए प्रभावी और सरल दोनों है। यह -ट्रांजिस्टर एम्पलीफायर परिपथ में मुश्किल होगा, जो उच्च आवृत्तियों पर [[न्यूट्रोडाइन]] की आवश्यकता होगी । | ||

=== पूर्वाग्रह === | === पूर्वाग्रह === | ||

जैसा कि दिखाया गया है | जैसा कि दिखाया गया है | दो स्टैक्ड एफईटी का उपयोग करने वाला कैस्कोड परिपथ दो एफईटी पर कुछ प्रतिबंध लगाता है अर्थात्, ऊपरी एफईटी को पक्षपाती होना चाहिए | जिससे इसका स्रोत वोल्टेज पर्याप्त उच्च हो (कम एफईटी ड्रेन वोल्टेज बहुत कम हो सकता है, जिससे यह संतृप्त हो सकता है)। एफईटी के लिए इस स्थिति को सुनिश्चित करने के लिए जोड़ी के लिए सावधानीपूर्वक चयन या ऊपरी एफईटी गेट के विशेष बायसिंग, बढ़ती निवेश की आवश्यकता होती है। | ||

कैसकोड परिपथ को द्विध्रुवी ट्रांजिस्टर, या एमओएसएफईटी, या एफईटी (या एमओएसएफईटी) और बीजेटी का उपयोग करके भी बनाया जा सकता है। [[वीएचएफ]] टेलीविजन ट्यूनर में यह परिपथ व्यवस्था बहुत सामान्य थी | जब वे वैक्यूम ट्यूबों को नियोजित करते थे। | कैसकोड परिपथ को द्विध्रुवी ट्रांजिस्टर, या एमओएसएफईटी, या एफईटी (या एमओएसएफईटी) और बीजेटी का उपयोग करके भी बनाया जा सकता है। [[वीएचएफ]] टेलीविजन ट्यूनर में यह परिपथ व्यवस्था बहुत सामान्य थी | जब वे वैक्यूम ट्यूबों को नियोजित करते थे। | ||

| Line 54: | Line 54: | ||

=== हानि === | === हानि === | ||

कैस्कोड परिपथ को दो ट्रांजिस्टर की आवश्यकता होती है और अपेक्षाकृत उच्च आपूर्ति वोल्टेज की आवश्यकता होती है। दो-एफईटी कैस्कोड के लिए, दोनों ट्रांजिस्टर को पर्याप्त | कैस्कोड परिपथ को दो ट्रांजिस्टर की आवश्यकता होती है और अपेक्षाकृत उच्च आपूर्ति वोल्टेज की आवश्यकता होती है। दो-एफईटी कैस्कोड के लिए, दोनों ट्रांजिस्टर को पर्याप्त v<sub>DS</sub> के साथ पक्षपाती होना चाहिए | संचालन में, आपूर्ति वोल्टेज पर निचली सीमा प्रयुक्त करना चाहिए। | ||

=== डुअल-गेट संस्करण === | === डुअल-गेट संस्करण === | ||

| Line 60: | Line 60: | ||

=== [[सुपरहेट्रोडाइन]] रिसीवर्स में मिक्सर === | === [[सुपरहेट्रोडाइन]] रिसीवर्स में मिक्सर === | ||

सुपरहेटरोडाइन रिसीवर्स में गुणा [[आवृत्ति मिक्सर]] परिपथ के रूप में कैस्कोड परिपथ बहुत उपयोगी है। निचले गेट पर | सुपरहेटरोडाइन रिसीवर्स में गुणा [[आवृत्ति मिक्सर]] परिपथ के रूप में कैस्कोड परिपथ बहुत उपयोगी है। निचले गेट पर RF संकेत मिक्सर को फीड किया जाता है, और ऊपरी गेट पर [[स्थानीय थरथरानवाला]] संकेत मिक्सर को फीड किया जाता है | दोनों संकेतों को मिक्सर द्वारा गुणा किया जाता है, और अंतर आवृत्ति, मध्यवर्ती आवृत्ति, कैस्कोड मिक्सर की ऊपरी नाली से ली जाती है। | ||

इसे संतुलित मिक्सर बनाने के लिए पूरे लंबी-पूंछ जोड़ी अंतर-प्रवर्धक चरणों को और फिर [[गिल्बर्ट सेल]] डबल-संतुलित मिक्सर कैसकोडिंग द्वारा विकसित किया गया था | | इसे संतुलित मिक्सर बनाने के लिए पूरे लंबी-पूंछ जोड़ी अंतर-प्रवर्धक चरणों को और फिर [[गिल्बर्ट सेल]] डबल-संतुलित मिक्सर कैसकोडिंग द्वारा विकसित किया गया था | | ||

| Line 67: | Line 67: | ||

[[एकीकृत परिपथ]] के उदय के साथ, सिलिकॉन डाई क्षेत्र के संदर्भ में ट्रांजिस्टर सस्ते हो गए हैं। विशेष रूप से एमओएसएफईटी प्रौद्योगिकी में, आउटपुट [[वर्तमान स्रोत]] के आउटपुट प्रतिबाधा को बढ़ाने के लिए [[वर्तमान दर्पण]] में कैसकोडिंग का उपयोग किया जा सकता है। | [[एकीकृत परिपथ]] के उदय के साथ, सिलिकॉन डाई क्षेत्र के संदर्भ में ट्रांजिस्टर सस्ते हो गए हैं। विशेष रूप से एमओएसएफईटी प्रौद्योगिकी में, आउटपुट [[वर्तमान स्रोत]] के आउटपुट प्रतिबाधा को बढ़ाने के लिए [[वर्तमान दर्पण]] में कैसकोडिंग का उपयोग किया जा सकता है। | ||

कैस्कोड का संशोधित संस्करण भी [[ मॉडुलन |मॉडुलन]] के रूप में उपयोग किया जा सकता | कैस्कोड का संशोधित संस्करण भी [[ मॉडुलन |मॉडुलन]] के रूप में उपयोग किया जा सकता है l विशेष रूप से आयाम मॉड्यूलेशन के लिए ऊपरी उपकरण ऑडियो संकेत की आपूर्ति करता है, और निचला [[ आरएफ न्यूनाधिक |RF न्यूनाधिक]] एम्पलीफायर उपकरण है। | ||

[[File:Cascode-voltage-ladder.png|thumb|right|हाई-वोल्टेज स्टैक]]उच्च-वोल्टेज ट्रांजिस्टर बनाने के लिए कैस्कोड को [[वोल्टेज सीढ़ी]] के साथ भी जोड़ा जा सकता है। इनपुट ट्रांजिस्टर किसी भी लो-U<sub>CEO</sub> का हो सकता है | जबकि अन्य, स्टैक्ड रैखिक नियामक सरल श्रृंखला नियामक वोल्टेज नियामकों के रूप में कार्य करते हुए, आपूर्ति वोल्टेज के अधिक अंश का सामना करने में सक्षम होना चाहिए। ध्यान दें कि बड़े आउटपुट-वोल्टेज स्विंग के लिए, उनके बेस वोल्टेज को कैपेसिटर द्वारा ग्राउंड पर बायपास नहीं किया जाना चाहिए, और ऊपरवाला सीढ़ी रोकनेवाला पूर्ण आपूर्ति वोल्टेज का सामना करने में सक्षम होना चाहिए। | [[File:Cascode-voltage-ladder.png|thumb|right|हाई-वोल्टेज स्टैक]]उच्च-वोल्टेज ट्रांजिस्टर बनाने के लिए कैस्कोड को [[वोल्टेज सीढ़ी]] के साथ भी जोड़ा जा सकता है। इनपुट ट्रांजिस्टर किसी भी लो-U<sub>CEO</sub> का हो सकता है | जबकि अन्य, स्टैक्ड रैखिक नियामक सरल श्रृंखला नियामक वोल्टेज नियामकों के रूप में कार्य करते हुए, आपूर्ति वोल्टेज के अधिक अंश का सामना करने में सक्षम होना चाहिए। ध्यान दें कि बड़े आउटपुट-वोल्टेज स्विंग के लिए, उनके बेस वोल्टेज को कैपेसिटर द्वारा ग्राउंड पर बायपास नहीं किया जाना चाहिए, और ऊपरवाला सीढ़ी रोकनेवाला पूर्ण आपूर्ति वोल्टेज का सामना करने में सक्षम होना चाहिए। | ||

इससे पता चलता है कि रैखिक श्रृंखला वोल्टेज नियामक वास्तव में वर्तमान बफर है जिसके ''इनपुट'' और ''आउटपुट'' पदनामों की अदला-बदली होती है। | इससे पता चलता है कि रैखिक श्रृंखला वोल्टेज नियामक वास्तव में वर्तमान बफर है | जिसके ''इनपुट'' और ''आउटपुट'' पदनामों की अदला-बदली होती है। | ||

== दो-पोर्ट मापदंड == | == दो-पोर्ट मापदंड == | ||

कैस्कोड विन्यास को इसके इनपुट प्रतिबाधा, आउटपुट प्रतिबाधा और वोल्टेज [[लाभ (इलेक्ट्रॉनिक्स)]] का उपयोग करके साधारण वोल्टेज एम्पलीफायर (या अधिक स्पष्ट रूप से, | कैस्कोड विन्यास को इसके इनपुट प्रतिबाधा, आउटपुट प्रतिबाधा और वोल्टेज [[लाभ (इलेक्ट्रॉनिक्स)]] का उपयोग करके साधारण वोल्टेज एम्पलीफायर (या अधिक स्पष्ट रूप से, g-मापदंड [[दो-पोर्ट नेटवर्क]] के रूप में) के रूप में दर्शाया जा सकता है। ये मापदंड नीचे दिए गए संबंधित g-मापदंड से संबंधित हैं।<ref>In the [[two-port network#Inverse hybrid parameters (g-parameters)|''g''-parameter two-port]], ''g''<sub>12</sub> is the reverse current gain. When no such feedback occurs, ''g''<sub>12</sub> = 0, and the network is called '''unilateral'''.</ref> अन्य उपयोगी गुणों पर यहां विचार नहीं किया गया है | परिपथ बैंडविड्थ (संकेत प्रोसेसिंग) और डायनेमिक स्तर इलेक्ट्रॉनिक्स होते है। | ||

=== बीजेटी कैस्कोड: कम-आवृत्ति वाले छोटे-संकेत मापदंड === | === बीजेटी कैस्कोड: कम-आवृत्ति वाले छोटे-संकेत मापदंड === | ||

[[File:BJT Cascode.png|thumbnail|200px|चित्र 2: डीसी बायस और बड़े कपलिंग कैपेसिटर के लिए ग्राउंड और एसी संकेत स्रोत के लिए आदर्श वर्तमान स्रोतों का उपयोग करके बीजेटी कैस्कोड; कैपेसिटर एसी के लिए शॉर्ट परिपथ हैं]]चित्र 2 में परिपथ के लिए आदर्श छोटे-संकेत समतुल्य परिपथ का निर्माण खुले परिपथ के साथ वर्तमान स्रोतों और शॉर्ट परिपथ वाले कैपेसिटर को बदलकर किया जा सकता है, यह मानते हुए कि वे आवृत्तियों पर शॉर्ट परिपथ के रूप में कार्य करने के लिए पर्याप्त हैं। बीजेटी को छोटे-संकेत परिपथ में हाइब्रिड-पी मॉडल | [[File:BJT Cascode.png|thumbnail|200px|चित्र 2: डीसी बायस और बड़े कपलिंग कैपेसिटर के लिए ग्राउंड और एसी संकेत स्रोत के लिए आदर्श वर्तमान स्रोतों का उपयोग करके बीजेटी कैस्कोड; कैपेसिटर एसी के लिए शॉर्ट परिपथ हैं]]चित्र 2 में परिपथ के लिए आदर्श छोटे-संकेत समतुल्य परिपथ का निर्माण खुले परिपथ के साथ वर्तमान स्रोतों और शॉर्ट परिपथ वाले कैपेसिटर को बदलकर किया जा सकता है, यह मानते हुए कि वे आवृत्तियों पर शॉर्ट परिपथ के रूप में कार्य करने के लिए पर्याप्त हैं। बीजेटी को छोटे-संकेत परिपथ में हाइब्रिड-पी मॉडल हाइब्रिड-π मॉडल द्वारा दर्शाया जा सकता है।<ref name=Gray-Meyer1> | ||

{{cite book | {{cite book | ||

|title= Analysis and Design of Analog Integrated Circuits | |title= Analysis and Design of Analog Integrated Circuits | ||

| Line 106: | Line 106: | ||

|} | |} | ||

=== एमओएसएफईटी कैस्कोड: कम-आवृत्ति वाले छोटे-संकेत मापदंड === | === एमओएसएफईटी कैस्कोड: कम-आवृत्ति वाले छोटे-संकेत मापदंड === | ||

[[File:MOSFET Cascode.png|thumbnail|200px|चित्रा 3: डीसी गेट पूर्वाग्रह के लिए आदर्श वोल्टेज स्रोतों और सक्रिय लोड के रूप में डीसी वर्तमान स्रोत का उपयोग कर एमओएसएफईटी कैस्कोड। चूंकि प्रत्येक एमओएसएफईटी ट्रांजिस्टर में गेट और स्रोत जुड़े होते हैं, यह विन्यास केवल असतत 3-टर्मिनल घटकों के लिए मान्य है।]]इसी तरह, एमओएसएफईटी संस्करण के लिए छोटे-संकेत मापदंड प्राप्त किए जा सकते हैं | [[File:MOSFET Cascode.png|thumbnail|200px|चित्रा 3: डीसी गेट पूर्वाग्रह के लिए आदर्श वोल्टेज स्रोतों और सक्रिय लोड के रूप में डीसी वर्तमान स्रोत का उपयोग कर एमओएसएफईटी कैस्कोड। चूंकि प्रत्येक एमओएसएफईटी ट्रांजिस्टर में गेट और स्रोत जुड़े होते हैं, यह विन्यास केवल असतत 3-टर्मिनल घटकों के लिए मान्य है।]]इसी तरह, एमओएसएफईटी संस्करण के लिए छोटे-संकेत मापदंड प्राप्त किए जा सकते हैं | एमओएसएफईटी को इसके हाइब्रिड-π मॉडल समकक्ष द्वारा भी प्रतिस्थापित किया जा सकता है। इस व्युत्पत्ति को यह देखते हुए सरल किया जा सकता है कि एमओएसएफईटी गेट करंट शून्य है | इसलिए बीजेटी के लिए छोटा-संकेत मॉडल शून्य बेस करंट की सीमा में एमओएसएफईटी का बन जाता है | | ||

:<math>I_B \to 0 \rArr r_\pi = \frac{V_T}{I_B} \to \infty,</math> | :<math>I_B \to 0 \rArr r_\pi = \frac{V_T}{I_B} \to \infty,</math> | ||

जहां v<sub>T</sub> बोल्ट्जमान स्थिरांक है | अर्धचालक भौतिकी में भूमिका: थर्मल वोल्टेज है।<ref name=Gray-Meyer2> | जहां v<sub>T</sub> बोल्ट्जमान स्थिरांक है | अर्धचालक भौतिकी में भूमिका: थर्मल वोल्टेज है।<ref name=Gray-Meyer2> | ||

| Line 137: | Line 137: | ||

|<math>\left( r_{\mathrm{O1}} + r_{\mathrm{O2}} \right) \left( 1+g_{\mathrm{m1}}(r_{\mathrm{O1}}//r_{\mathrm{O2}}) \right)</math> | |<math>\left( r_{\mathrm{O1}} + r_{\mathrm{O2}} \right) \left( 1+g_{\mathrm{m1}}(r_{\mathrm{O1}}//r_{\mathrm{O2}}) \right)</math> | ||

|} | |} | ||

कारकों का संयोजन g<sub>m</sub>r<sub>O</sub> उपरोक्त सूत्रों में अधिकांशतः होता है | कारकों का संयोजन g<sub>m</sub>r<sub>O</sub> उपरोक्त सूत्रों में अधिकांशतः होता है | जो आगे की परीक्षा को आमंत्रित करता है। द्विध्रुवी ट्रांजिस्टर के लिए यह उत्पाद है | ([[ हाइब्रिड-पाई मॉडल | हाइब्रिड-पाई मॉडल]] देखें): | ||

:<math>g_m r_O = \frac{I_C}{V_T} \frac{V_A + V_{CE}}{I_C} = \frac{V_A + V_{CE}}{V_T}.</math> | :<math>g_m r_O = \frac{I_C}{V_T} \frac{V_A + V_{CE}}{I_C} = \frac{V_A + V_{CE}}{V_T}.</math> | ||

| Line 165: | Line 165: | ||

|url=http://worldcat.org/isbn/0387257462 | |url=http://worldcat.org/isbn/0387257462 | ||

|page=13 (§0124)}} | |page=13 (§0124)}} | ||

</ref> बात यह है कि क्योंकि g<sub>m</sub>r<sub>O</sub>प्रौद्योगिकी की परवाह किए बिना लगभग बड़ा है | </ref> बात यह है कि क्योंकि g<sub>m</sub>r<sub>O</sub>प्रौद्योगिकी की परवाह किए बिना लगभग बड़ा है | एमओएसएफईटी और द्विध्रुवी कैस्कोड दोनों के लिए सारणीबद्ध लाभ और आउटपुट प्रतिरोध बहुत बड़ा है। इस तथ्य का आगामी चर्चा में निहितार्थ है। | ||

=== कम आवृत्ति रचना === | === कम आवृत्ति रचना === | ||

[[File:BJT Cascode Small-signal Circuit.png|thumbnail|400px|चित्र 4 टॉप: हाइब्रिड-पीआई मॉडल का उपयोग करते हुए छोटे-संकेत बीजेटी कैस्कोड नीचे: एम्पलीफायर कम आवृत्ति मापदंड का उपयोग करके बीजेटी कैस्कोड के लिए समतुल्य परिपथ]]उपरोक्त सूत्रों में पाए जाने वाले g-मापदंड का उपयोग मूल कैस्कोड (समतुल्य परिपथ) के समान लाभ, इनपुट और आउटपुट प्रतिरोध के साथ छोटे-संकेत वोल्टेज एम्पलीफायर के निर्माण के लिए किया जा सकता है। यह परिपथ केवल इतनी कम आवृत्तियों पर प्रयुक्त होता है कि ट्रांजिस्टर [[परजीवी समाई|परजीवी]] कोई मायने नहीं रखती। यह आंकड़ा मूल कैस्कोड (चित्र 1) और समतुल्य वोल्टेज एम्पलीफायर या | [[File:BJT Cascode Small-signal Circuit.png|thumbnail|400px|चित्र 4 टॉप: हाइब्रिड-पीआई मॉडल का उपयोग करते हुए छोटे-संकेत बीजेटी कैस्कोड नीचे: एम्पलीफायर कम आवृत्ति मापदंड का उपयोग करके बीजेटी कैस्कोड के लिए समतुल्य परिपथ]]उपरोक्त सूत्रों में पाए जाने वाले g-मापदंड का उपयोग मूल कैस्कोड (समतुल्य परिपथ) के समान लाभ, इनपुट और आउटपुट प्रतिरोध के साथ छोटे-संकेत वोल्टेज एम्पलीफायर के निर्माण के लिए किया जा सकता है। यह परिपथ केवल इतनी कम आवृत्तियों पर प्रयुक्त होता है कि ट्रांजिस्टर [[परजीवी समाई|परजीवी]] कोई मायने नहीं रखती। यह आंकड़ा मूल कैस्कोड (चित्र 1) और समतुल्य वोल्टेज एम्पलीफायर या g-समतुल्य दो-पोर्ट (चित्र 4) दिखाता है। समतुल्य परिपथ विभिन्न चालकों और भारों के लिए परिपथ के व्यवहार की सरल गणना की अनुमति देता है। चित्र में थेवेनिन प्रतिरोध R<sub>S</sub> के साथ थेवेनिन समकक्ष वोल्टेज स्रोतएम्पलीफायर ड्राइव करता है, और आउटपुट पर साधारण लोड रेसिस्टर R<sub>L</sub>संलग्न है। समतुल्य परिपथ का उपयोग करते हुए, एम्पलीफायर के लिए इनपुट वोल्टेज है | ([[ वोल्टेज विभक्त | वोल्टेज विभक्त]] देखें): | ||

::<math>{\upsilon}_{in} = {\upsilon}_s \begin{matrix} \frac {R_{in}}{R_S + R_{in}} \end{matrix}</math>, | ::<math>{\upsilon}_{in} = {\upsilon}_s \begin{matrix} \frac {R_{in}}{R_S + R_{in}} \end{matrix}</math>, | ||

जो R<sub>S</sub> << R<sub>in</sub> प्रतिरोध वाले ड्राइवर के उपयोग के महत्व को दर्शाता हैl एम्पलीफायर में प्रवेश करने वाले संकेत के क्षीणन से बचने के लिए। उपरोक्त प्रवर्धक विशेषताओं से, हम देखते हैं कि R<sub>in</sub> एमओएसएफईटी कैस्कोड के लिए अनंत है, इसलिए उस स्थिति में इनपुट संकेत का कोई क्षीणन नहीं होता है। बीजेटी कैस्कोड अधिक प्रतिबंधात्मक है | क्योंकि R<sub>in</sub> = R<sub>π2</sub>. | जो R<sub>S</sub> << R<sub>in</sub> प्रतिरोध वाले ड्राइवर के उपयोग के महत्व को दर्शाता हैl एम्पलीफायर में प्रवेश करने वाले संकेत के क्षीणन से बचने के लिए। उपरोक्त प्रवर्धक विशेषताओं से, हम देखते हैं कि R<sub>in</sub> एमओएसएफईटी कैस्कोड के लिए अनंत है, इसलिए उस स्थिति में इनपुट संकेत का कोई क्षीणन नहीं होता है। बीजेटी कैस्कोड अधिक प्रतिबंधात्मक है | क्योंकि R<sub>in</sub> = R<sub>π2</sub>. | ||

| Line 184: | Line 184: | ||

=== उच्च आवृत्ति रचना === | === उच्च आवृत्ति रचना === | ||

उच्च आवृत्तियों पर, स्पष्ट आवृत्ति प्रतिक्रिया प्राप्त करने के लिए ट्रांजिस्टर (गेट-टू-ड्रेन, गेट-टू-सोर्स, ड्रेन-टू बॉडी, और बाइपोलर समतुल्य) के परजीवी को हाइब्रिड-π मॉडल में सम्मिलित किया जाना चाहिए। कम आवृत्ति वाले रचना के लिए ऊपर वर्णित समग्र उच्च लाभ पर जोर देने से रचना लक्ष्य भी भिन्न होते हैं। उच्च आवृत्ति परिपथ में, संकेत प्रतिबिंबों को खत्म करने और [[शक्ति लाभ]] को अधिकतम करने के लिए एम्पलीफायर के इनपुट और आउटपुट पर [[प्रतिबाधा मिलान]] सामान्यतः वांछित होता है। कैस्कोड में, इनपुट और आउटपुट [[ बंदरगाह (सर्किट सिद्धांत) |बंदरगाह (परिपथ सिद्धांत)]] के बीच अभी भी छोटे से रिवर्स ट्रांसमिशन टर्म g<sub>12</sub> द्वारा विशेषता है | मेल खाने वाले नेटवर्क को रचना करना | उच्च आवृत्तियों पर, स्पष्ट आवृत्ति प्रतिक्रिया प्राप्त करने के लिए ट्रांजिस्टर (गेट-टू-ड्रेन, गेट-टू-सोर्स, ड्रेन-टू बॉडी, और बाइपोलर समतुल्य) के परजीवी को हाइब्रिड-π मॉडल में सम्मिलित किया जाना चाहिए। कम आवृत्ति वाले रचना के लिए ऊपर वर्णित समग्र उच्च लाभ पर जोर देने से रचना लक्ष्य भी भिन्न होते हैं। उच्च आवृत्ति परिपथ में, संकेत प्रतिबिंबों को खत्म करने और [[शक्ति लाभ]] को अधिकतम करने के लिए एम्पलीफायर के इनपुट और आउटपुट पर [[प्रतिबाधा मिलान]] सामान्यतः वांछित होता है। कैस्कोड में, इनपुट और आउटपुट [[ बंदरगाह (सर्किट सिद्धांत) |बंदरगाह (परिपथ सिद्धांत)]] के बीच अभी भी छोटे से रिवर्स ट्रांसमिशन टर्म g<sub>12</sub> द्वारा विशेषता है | मेल खाने वाले नेटवर्क को रचना करना सरल बनाता है | क्योंकि एम्पलीफायर लगभग एकतरफा है। | ||

==संदर्भ== | ==संदर्भ== | ||

Revision as of 10:40, 20 May 2023

कैस्कोड एक दो-चरण एम्पलीफायर है, जिसमें सामान्य-एमिटर चरण होता है जो सामान्य-बेस चरण में होता है।[1][2]

एकल प्रवर्धक चरण की तुलना में, इस संयोजन में निम्नलिखित विशेषताओं में से एक या अधिक हो सकते हैं l उच्च इनपुट-आउटपुट , उच्च इनपुट प्रतिबाधा, उच्च आउटपुट प्रतिबाधा, उच्च बैंडविड्थ (संकेत प्रोसेसिंग) होता है।

आधुनिक परिपथ में, कैस्कोड अधिकांशतः दो ट्रांजिस्टर (द्विध्रुवी जंक्शन ट्रांजिस्टर फील्ड इफ़ेक्ट ट्रांजिस्टर ) से बना होता है | जिसमें से सामान्य उत्सर्जक या सामान्य स्रोत के रूप में काम करता है और दूसरा सामान्य आधार या सामान्य गेट के रूप में होता है।

कैस्कोड इनपुट-आउटपुट (रिवर्स ट्रांसमिशन को कम करता है) में सुधार करता है | क्योंकि आउटपुट से इनपुट तक कोई सीधा युग्मन नहीं होता है। यह मिलर प्रभाव को समाप्त करता है और इस प्रकार बहुत अधिक बैंडविड्थ में योगदान देता है।

इतिहास

कैसकोड (कभी-कभी कैसकोडिंग के लिए क्रिया ) का उपयोग एनालॉग परिपथ प्रदर्शन में सुधार के लिए सामान्य विधि है | जो वेक्यूम - ट्यूब और ट्रांजिस्टर दोनों पर प्रयुक्त होता है। वोल्टेज स्टेबलाइजर के आवेदन पर चर्चा में 1939 में फ्रेडरिक विंटन हंट और रोजर वेन हिकमैन द्वारा लिखे गए एक लेख में कैसकोड नाम गढ़ा गया था।[3] उन्होंने कलम के साथ के प्रतिस्थापन के रूप में दो ट्रायोड ( सामान्य कैथोड सेटअप के साथ पहला, सामान्य नियंत्रण ग्रिड वाला दूसरा) का कैस्केड प्रस्तावित किया, और इसलिए नाम को कैस्क (एडेड ट्रायोड एम्पलीफायर) का संक्षिप्त नाम माना जा सकता है। विशेषताओं के समान, किन्तु एकल पेंट) की तुलना में [4] कम ध्वनि और व्यापक बैंडविड्थ के कारण 'फ्रंट-एंड' या ट्यूनर के लिए प्रारंभिक टेलीविजन सेटों में कैस्कोड परिपथ नियोजित किए गए थे।

संचालन

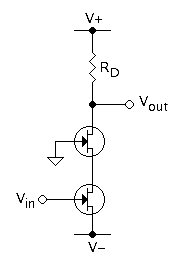

चित्रा 1 संकेत स्रोत, vin द्वारा संचालित इनपुट चरण के रूप में सामान्य स्रोत एम्पलीफायर के साथ कैस्कोड एम्पलीफायर का उदाहरण दिखाता है | यह इनपुट चरण आउटपुट संकेत vout के साथ आउटपुट चरण के रूप में सामान्य-गेट एम्पलीफायर चलाता है |

जैसा कि निचला एफईटी संचालित करता है | यह ऊपरी एफईटी के स्रोत वोल्टेज को बदलता है, और ऊपरी एफईटी इसके गेट और स्रोत के बीच परिवर्तित क्षमता के कारण संचालित होता है।

इस परिपथ व्यवस्था का प्रमुख लाभ इनपुट (कम) एफईटी के आउटपुट टर्मिनल (नाली) के भार के रूप में ऊपरी क्षेत्र-प्रभाव ट्रांजिस्टर (एफईटी) की नियुक्ति से उत्पन्न है। क्योंकि संचालन आवृत्तियों पर ऊपरी एफईटी का गेट प्रभावी रूप से ग्राउंडेड होता है | ऊपरी एफईटी का स्रोत वोल्टेज (और इसलिए इनपुट ट्रांजिस्टर की नाली) संचालन के समय लगभग स्थिर वोल्टेज पर आयोजित होता है। दूसरे शब्दों में, ऊपरी एफईटी निचले एफईटी के लिए कम इनपुट प्रतिरोध प्रदर्शित करता हैl जिससे निचले एफईटी का वोल्टेज लाभ बहुत छोटा हो जाता हैl जो नाटकीय रूप से मिलर प्रभाव फीडबैक कैपेसिटेंस को निचले एफईटी के नाले से गेट तक कम कर देता है। वोल्टेज लाभ का यह हानि ऊपरी एफईटी द्वारा वसूल किया जाता है। इस प्रकार, ऊपरी ट्रांजिस्टर कम एफईटी को न्यूनतम ऋणात्मक (मिलर) प्रतिक्रिया के साथ संचालित करने की अनुमति देता हैl जिससे इसकी बैंडविड्थ में सुधार होता है।

ऊपरी एफईटी गेट विद्युत रूप से ग्राउंडेड है, इसलिए कैपेसिटेंस Cdg का चार्ज और डिस्चार्ज,केवल RD , नाली और गेट के बीच से होकर जाता है और आउटपुट लोड (Rout कहते हैं), और आवृत्ति प्रतिक्रिया केवल संबद्ध Rc समय स्थिर τ = C से ऊपर की आवृत्तियों के लिए प्रभावित होती है | RD//Rout, अर्थात् f = 1/(2πτ), उच्च आवृत्ति क्योंकि Cdgछोटा है अर्थात्, ऊपरी एफईटी गेट Cdg के मिलर प्रवर्धन से ग्रस्त नहीं है |

यदि ऊपरी एफईटी चरण अकेले अपने स्रोत को इनपुट नोड (अर्थात, कॉमन-गेट (CG) विन्यास) के रूप में उपयोग करके संचालित किया जाता है, तो इसमें अच्छा वोल्टेज लाभ और व्यापक बैंडविड्थ होगा। चूँकि, इसकी कम इनपुट प्रतिबाधा इसकी उपयोगिता को बहुत कम-प्रतिबाधा वोल्टेज चालकों तक सीमित कर देगी। उच्च इनपुट प्रतिबाधा में कम एफईटी परिणाम जोड़ने से, कैस्कोड चरण को उच्च-प्रतिबाधा स्रोत द्वारा संचालित करने की अनुमति मिलती है।

यदि कोई ऊपरी एफईटी को विशिष्ट आगमनात्मक/प्रतिरोधक भार के साथ प्रतिस्थापित करता है और इनपुट ट्रांजिस्टर के ड्रेन (अर्थात, सामान्य-स्रोत (सीएस) विन्यास) से आउटपुट लेता है, तो सीएस विन्यास उसी इनपुट प्रतिबाधा की प्रस्तुति करेगा जो कैस्कोड के रूप में होती है।, किन्तु कैस्कोड विन्यास संभावित रूप से अधिक लाभ और बहुत अधिक बैंडविड्थ प्रदान करेगा।

स्थिरता

कैस्कोड व्यवस्था भी बहुत स्थिर है। इसका आउटपुट विद्युत और भौतिक दोनों तरह से इनपुट से प्रभावी रूप से अलग होता है। निचले ट्रांजिस्टर में नाली और स्रोत दोनों पर लगभग स्थिर वोल्टेज होता है, और इस प्रकार इसके गेट में वापस फीड करने के लिए अनिवार्य रूप से कुछ भी नहीं होता है। ऊपरी ट्रांजिस्टर के गेट और स्रोत पर लगभग स्थिर वोल्टेज होता है। इस प्रकार, उन पर महत्वपूर्ण वोल्टेज वाले एकमात्र नोड इनपुट और आउटपुट हैं, और इन्हें लगभग स्थिर वोल्टेज के केंद्रीय सम्बन्ध और दो ट्रांजिस्टर की भौतिक दूरी से अलग किया जाता है। इस प्रकार व्यवहार में आउटपुट से इनपुट तक बहुत कम प्रतिक्रिया होती है। धातु परिरक्षण दोनों ट्रांजिस्टर के बीच आवश्यकता पड़ने पर और भी अधिक के लिए प्रभावी और सरल दोनों है। यह -ट्रांजिस्टर एम्पलीफायर परिपथ में मुश्किल होगा, जो उच्च आवृत्तियों पर न्यूट्रोडाइन की आवश्यकता होगी ।

पूर्वाग्रह

जैसा कि दिखाया गया है | दो स्टैक्ड एफईटी का उपयोग करने वाला कैस्कोड परिपथ दो एफईटी पर कुछ प्रतिबंध लगाता है अर्थात्, ऊपरी एफईटी को पक्षपाती होना चाहिए | जिससे इसका स्रोत वोल्टेज पर्याप्त उच्च हो (कम एफईटी ड्रेन वोल्टेज बहुत कम हो सकता है, जिससे यह संतृप्त हो सकता है)। एफईटी के लिए इस स्थिति को सुनिश्चित करने के लिए जोड़ी के लिए सावधानीपूर्वक चयन या ऊपरी एफईटी गेट के विशेष बायसिंग, बढ़ती निवेश की आवश्यकता होती है।

कैसकोड परिपथ को द्विध्रुवी ट्रांजिस्टर, या एमओएसएफईटी, या एफईटी (या एमओएसएफईटी) और बीजेटी का उपयोग करके भी बनाया जा सकता है। वीएचएफ टेलीविजन ट्यूनर में यह परिपथ व्यवस्था बहुत सामान्य थी | जब वे वैक्यूम ट्यूबों को नियोजित करते थे।

लाभ

कैस्कोड व्यवस्था उच्च लाभ, उच्च बैंडविड्थ, उच्च स्लीव दर, उच्च स्थिरता और उच्च इनपुट प्रतिबाधा प्रदान करती है। दो-ट्रांजिस्टर परिपथ के रूप में, पुर्जों की संख्या बहुत कम है।

हानि

कैस्कोड परिपथ को दो ट्रांजिस्टर की आवश्यकता होती है और अपेक्षाकृत उच्च आपूर्ति वोल्टेज की आवश्यकता होती है। दो-एफईटी कैस्कोड के लिए, दोनों ट्रांजिस्टर को पर्याप्त vDS के साथ पक्षपाती होना चाहिए | संचालन में, आपूर्ति वोल्टेज पर निचली सीमा प्रयुक्त करना चाहिए।

डुअल-गेट संस्करण

मल्टीगेट उपकरण डुअल-गेट एमओएसएफईटी अधिकांशतः -ट्रांजिस्टर कैस्कोड के रूप में कार्य करता है | संवेदनशील बहुत उच्च आवृत्ति रिसीवर के सामने के छोर में सामान्य, एक दोहरे गेट एमओएसएफईटी को इनपुट से जुड़े प्राथमिक गेट (सामान्यतः एमओएसएफईटी निर्माताओं द्वारा निर्दिष्ट गेट 1) के साथ सामान्य-स्रोत एम्पलीफायर के रूप में संचालित किया जाता है और दूसरा गेट ग्राउंडेड (बाईपास) होता है। आंतरिक रूप से, दो निकटवर्ती फाटकों द्वारा कवर किया गया चैनल है | इसलिए, परिणामी परिपथ विद्युत रूप से दो एफईटी से बना कैस्कोड है, सामान्य निचला-नाली-से-ऊपरी-स्रोत सम्बन्ध केवल एकल चैनल का वह भाग है | जो दो फाटकों के बीच की सीमा के निकट भौतिक रूप से स्थित है।

सुपरहेट्रोडाइन रिसीवर्स में मिक्सर

सुपरहेटरोडाइन रिसीवर्स में गुणा आवृत्ति मिक्सर परिपथ के रूप में कैस्कोड परिपथ बहुत उपयोगी है। निचले गेट पर RF संकेत मिक्सर को फीड किया जाता है, और ऊपरी गेट पर स्थानीय थरथरानवाला संकेत मिक्सर को फीड किया जाता है | दोनों संकेतों को मिक्सर द्वारा गुणा किया जाता है, और अंतर आवृत्ति, मध्यवर्ती आवृत्ति, कैस्कोड मिक्सर की ऊपरी नाली से ली जाती है।

इसे संतुलित मिक्सर बनाने के लिए पूरे लंबी-पूंछ जोड़ी अंतर-प्रवर्धक चरणों को और फिर गिल्बर्ट सेल डबल-संतुलित मिक्सर कैसकोडिंग द्वारा विकसित किया गया था |

अन्य अनुप्रयोग

एकीकृत परिपथ के उदय के साथ, सिलिकॉन डाई क्षेत्र के संदर्भ में ट्रांजिस्टर सस्ते हो गए हैं। विशेष रूप से एमओएसएफईटी प्रौद्योगिकी में, आउटपुट वर्तमान स्रोत के आउटपुट प्रतिबाधा को बढ़ाने के लिए वर्तमान दर्पण में कैसकोडिंग का उपयोग किया जा सकता है।

कैस्कोड का संशोधित संस्करण भी मॉडुलन के रूप में उपयोग किया जा सकता है l विशेष रूप से आयाम मॉड्यूलेशन के लिए ऊपरी उपकरण ऑडियो संकेत की आपूर्ति करता है, और निचला RF न्यूनाधिक एम्पलीफायर उपकरण है।

उच्च-वोल्टेज ट्रांजिस्टर बनाने के लिए कैस्कोड को वोल्टेज सीढ़ी के साथ भी जोड़ा जा सकता है। इनपुट ट्रांजिस्टर किसी भी लो-UCEO का हो सकता है | जबकि अन्य, स्टैक्ड रैखिक नियामक सरल श्रृंखला नियामक वोल्टेज नियामकों के रूप में कार्य करते हुए, आपूर्ति वोल्टेज के अधिक अंश का सामना करने में सक्षम होना चाहिए। ध्यान दें कि बड़े आउटपुट-वोल्टेज स्विंग के लिए, उनके बेस वोल्टेज को कैपेसिटर द्वारा ग्राउंड पर बायपास नहीं किया जाना चाहिए, और ऊपरवाला सीढ़ी रोकनेवाला पूर्ण आपूर्ति वोल्टेज का सामना करने में सक्षम होना चाहिए।

इससे पता चलता है कि रैखिक श्रृंखला वोल्टेज नियामक वास्तव में वर्तमान बफर है | जिसके इनपुट और आउटपुट पदनामों की अदला-बदली होती है।

दो-पोर्ट मापदंड

कैस्कोड विन्यास को इसके इनपुट प्रतिबाधा, आउटपुट प्रतिबाधा और वोल्टेज लाभ (इलेक्ट्रॉनिक्स) का उपयोग करके साधारण वोल्टेज एम्पलीफायर (या अधिक स्पष्ट रूप से, g-मापदंड दो-पोर्ट नेटवर्क के रूप में) के रूप में दर्शाया जा सकता है। ये मापदंड नीचे दिए गए संबंधित g-मापदंड से संबंधित हैं।[5] अन्य उपयोगी गुणों पर यहां विचार नहीं किया गया है | परिपथ बैंडविड्थ (संकेत प्रोसेसिंग) और डायनेमिक स्तर इलेक्ट्रॉनिक्स होते है।

बीजेटी कैस्कोड: कम-आवृत्ति वाले छोटे-संकेत मापदंड

चित्र 2 में परिपथ के लिए आदर्श छोटे-संकेत समतुल्य परिपथ का निर्माण खुले परिपथ के साथ वर्तमान स्रोतों और शॉर्ट परिपथ वाले कैपेसिटर को बदलकर किया जा सकता है, यह मानते हुए कि वे आवृत्तियों पर शॉर्ट परिपथ के रूप में कार्य करने के लिए पर्याप्त हैं। बीजेटी को छोटे-संकेत परिपथ में हाइब्रिड-पी मॉडल हाइब्रिड-π मॉडल द्वारा दर्शाया जा सकता है।[6]

| परिभाषा | अभिव्यक्ति | |

|---|---|---|

| वोल्टेज में वृद्धि | ||

| इनपुट प्रतिरोध | ||

| आउटपुट प्रतिरोध |

एमओएसएफईटी कैस्कोड: कम-आवृत्ति वाले छोटे-संकेत मापदंड

इसी तरह, एमओएसएफईटी संस्करण के लिए छोटे-संकेत मापदंड प्राप्त किए जा सकते हैं | एमओएसएफईटी को इसके हाइब्रिड-π मॉडल समकक्ष द्वारा भी प्रतिस्थापित किया जा सकता है। इस व्युत्पत्ति को यह देखते हुए सरल किया जा सकता है कि एमओएसएफईटी गेट करंट शून्य है | इसलिए बीजेटी के लिए छोटा-संकेत मॉडल शून्य बेस करंट की सीमा में एमओएसएफईटी का बन जाता है |

जहां vT बोल्ट्जमान स्थिरांक है | अर्धचालक भौतिकी में भूमिका: थर्मल वोल्टेज है।[7]

| परिभाषा | अभिव्यक्ति | |

|---|---|---|

| वोल्टेज में वृद्धि | ||

| इनपुट प्रतिरोध | ||

| आउटपुट प्रतिरोध |

कारकों का संयोजन gmrO उपरोक्त सूत्रों में अधिकांशतः होता है | जो आगे की परीक्षा को आमंत्रित करता है। द्विध्रुवी ट्रांजिस्टर के लिए यह उत्पाद है | ( हाइब्रिड-पाई मॉडल देखें):

विशिष्ट असतत द्विध्रुवी उपकरण में प्रारंभिक वोल्टेज VA≈ 100 V और कमरे के तापमान के पास थर्मल वोल्टेज VT≈ 25 mV, है | जिससे gmrO≈ 4000 बनता है, किन्तु एक बड़ी संख्या है।

हाइब्रिड-पीआई मॉडल पर लेख से, हम एमओएसएफईटी को सक्रिय मोड में पाते हैं |

65 नैनोमीटर प्रौद्योगिकी नोड पर, ID≈ 1.2 mA/μ चौड़ाई, आपूर्ति वोल्टेज VDD= 1.1 V है | Vth≈ 165 mV, और Vov = VGS-Vth ≈ 5% VDD≈ 55 mV है। सामान्य लंबाई को न्यूनतम L = 2 Lmin= 0.130 सुक्ष्ममापी और λ ≈ 1/(4 V/μm L) का विशिष्ट मान दो बार लेते हुए, हम 1/λ ≈ 2 V, और gmrO≈ 110, पाते हैं जो अभी भी बड़ा मान है।[8][9] बात यह है कि क्योंकि gmrOप्रौद्योगिकी की परवाह किए बिना लगभग बड़ा है | एमओएसएफईटी और द्विध्रुवी कैस्कोड दोनों के लिए सारणीबद्ध लाभ और आउटपुट प्रतिरोध बहुत बड़ा है। इस तथ्य का आगामी चर्चा में निहितार्थ है।

कम आवृत्ति रचना

उपरोक्त सूत्रों में पाए जाने वाले g-मापदंड का उपयोग मूल कैस्कोड (समतुल्य परिपथ) के समान लाभ, इनपुट और आउटपुट प्रतिरोध के साथ छोटे-संकेत वोल्टेज एम्पलीफायर के निर्माण के लिए किया जा सकता है। यह परिपथ केवल इतनी कम आवृत्तियों पर प्रयुक्त होता है कि ट्रांजिस्टर परजीवी कोई मायने नहीं रखती। यह आंकड़ा मूल कैस्कोड (चित्र 1) और समतुल्य वोल्टेज एम्पलीफायर या g-समतुल्य दो-पोर्ट (चित्र 4) दिखाता है। समतुल्य परिपथ विभिन्न चालकों और भारों के लिए परिपथ के व्यवहार की सरल गणना की अनुमति देता है। चित्र में थेवेनिन प्रतिरोध RS के साथ थेवेनिन समकक्ष वोल्टेज स्रोतएम्पलीफायर ड्राइव करता है, और आउटपुट पर साधारण लोड रेसिस्टर RLसंलग्न है। समतुल्य परिपथ का उपयोग करते हुए, एम्पलीफायर के लिए इनपुट वोल्टेज है | ( वोल्टेज विभक्त देखें):

- ,

जो RS << Rin प्रतिरोध वाले ड्राइवर के उपयोग के महत्व को दर्शाता हैl एम्पलीफायर में प्रवेश करने वाले संकेत के क्षीणन से बचने के लिए। उपरोक्त प्रवर्धक विशेषताओं से, हम देखते हैं कि Rin एमओएसएफईटी कैस्कोड के लिए अनंत है, इसलिए उस स्थिति में इनपुट संकेत का कोई क्षीणन नहीं होता है। बीजेटी कैस्कोड अधिक प्रतिबंधात्मक है | क्योंकि Rin = Rπ2.

इसी तरह, समतुल्य परिपथ से आउटपुट संकेत है |

- .

कम-आवृत्ति परिपथ में, उच्च वोल्टेज लाभ सामान्यतः वांछित होता है | इसलिए प्रतिरोध RL >> Rout के साथ लोड का उपयोग करने का महत्व लोड तक पहुँचने वाले संकेत के क्षीणन से बचने के लिए Rout के लिए सूत्र लोड की तुलना में पर्याप्त रूप से छोटे आउटपुट प्रतिरोध के साथ एम्पलीफायर को रचना करने के लिए उपयोग किया जा सकता है या, यदि ऐसा नहीं किया जा सकता है, तो संशोधित परिपथ पर निर्णय लेने के लिए, उदाहरण के लिए, वोल्टेज अनुयायी जोड़ने के लिए जो लोड से उत्तम मेल खाता है।

पहले के अनुमान से पता चला है कि कैस्कोड आउटपुट प्रतिरोध बहुत बड़ा है। निहितार्थ यह है कि कई लोड प्रतिरोध RL >> Rout को संतुष्ट नहीं करेंगे( महत्वपूर्ण अपवाद एमओएसएफईटी को लोड के रूप में चला रहा है, जिसमें अनंत कम आवृत्ति इनपुट प्रतिबाधा है)। चूँकि, पूरा करने में विफलता RL >> Routआपदाजनक नहीं है क्योंकि कैस्कोड लाभ भी बहुत बड़ा है। यदि रचनार तैयार है, तो कम भार प्रतिरोध की अनुमति देने के लिए बड़े लाभ का त्याग किया जा सकता है | RL<< Rout के लिए लाभ निम्नानुसार सरल होता है |

- .

यह लाभ उतना ही है जितना अकेले अभिनय करने वाले इनपुट ट्रांजिस्टर के लिए इस प्रकार, यहां तक कि लाभ का त्याग करते हुए, कैस्कोड एकल-ट्रांजिस्टर ट्रांसकंडक्शन एम्पलीफायर के समान लाभ उत्पन्न करता है, किन्तु व्यापक बैंडविड्थ के साथ उत्पन्न नहीं करता है।

चूंकि एम्पलीफायर व्यापक बैंडविड्थ हैं | वही दृष्टिकोण परिपथ की बैंडविड्थ निर्धारित कर सकता है | जब भार संधारित्र संलग्न होता है (बिना या बिना) लोड प्रतिरोधी). आवश्यक धारणा यह है कि भार अधिक बड़ा है कि यह आवृत्ति निर्भरता को नियंत्रित करता है, और बैंडविड्थ स्वयं ट्रांजिस्टर के उपेक्षित परजीवी कैपेसिटेंस द्वारा नियंत्रित नहीं होता है।

उच्च आवृत्ति रचना

उच्च आवृत्तियों पर, स्पष्ट आवृत्ति प्रतिक्रिया प्राप्त करने के लिए ट्रांजिस्टर (गेट-टू-ड्रेन, गेट-टू-सोर्स, ड्रेन-टू बॉडी, और बाइपोलर समतुल्य) के परजीवी को हाइब्रिड-π मॉडल में सम्मिलित किया जाना चाहिए। कम आवृत्ति वाले रचना के लिए ऊपर वर्णित समग्र उच्च लाभ पर जोर देने से रचना लक्ष्य भी भिन्न होते हैं। उच्च आवृत्ति परिपथ में, संकेत प्रतिबिंबों को खत्म करने और शक्ति लाभ को अधिकतम करने के लिए एम्पलीफायर के इनपुट और आउटपुट पर प्रतिबाधा मिलान सामान्यतः वांछित होता है। कैस्कोड में, इनपुट और आउटपुट बंदरगाह (परिपथ सिद्धांत) के बीच अभी भी छोटे से रिवर्स ट्रांसमिशन टर्म g12 द्वारा विशेषता है | मेल खाने वाले नेटवर्क को रचना करना सरल बनाता है | क्योंकि एम्पलीफायर लगभग एकतरफा है।

संदर्भ

- ↑ Phillip A. Laplante (2005). Comprehensive Dictionary of Electrical Engineering (Second ed.). Boca Raton: CRC Press. p. 97. ISBN 0-8493-3086-6.

- ↑ S. W. Amos; Roger S. Amos (2002). Newnes Dictionary of Electronics (Fourth ed.). Oxford: Newnes. pp. 46. ISBN 0-7506-4331-5.

- ↑ Hunt, Frederick Vinton; Hickman, Roger Wayne (1939). "इलेक्ट्रॉनिक वोल्टेज स्टेबलाइजर्स पर" (PDF). Review of Scientific Instruments. 10 (1): 6. doi:10.1063/1.1751443. Retrieved 20 March 2016.

- ↑ "Cathode Ray", "The Cascode and its Advantages for Band III Reception", Wireless World, vol. 61, p. 397 (August 1955).

- ↑ In the g-parameter two-port, g12 is the reverse current gain. When no such feedback occurs, g12 = 0, and the network is called unilateral.

- ↑ Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer; et al. (2001). Analysis and Design of Analog Integrated Circuits (Fourth ed.). New York: Wiley. pp. 206–208. ISBN 0-471-32168-0.

- ↑ Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer; et al. (2001). Analysis and Design of Analog Integrated Circuits (Fourth ed.). New York: Wiley. pp. 208–211. ISBN 0-471-32168-0.

- ↑ R. Jacob Baker (2010). CMOS Circuit Design, Layout, and Simulation, Third Edition. New York: Wiley-IEEE. pp. 297–301. ISBN 978-0-470-88132-3.

- ↑ W. M. C. Sansen (2006). Analog Design Essentials. Dordrecht: Springer. p. 13 (§0124). ISBN 0-387-25746-2.