फ्लैश मेमोरी: Difference between revisions

No edit summary |

No edit summary |

||

| Line 315: | Line 315: | ||

== फ्लैश फ़ाइल | == फ्लैश फ़ाइल तंत्र (Flash File System) == | ||

{{Main|Flash file system}} | {{Main|Flash file system}} | ||

फ्लैश मेमोरी की | फ्लैश मेमोरी की व्यक्तिगत विशेषताओं के कारण, या तो इसका सबसे अच्छा उपयोग घिसाव स्तर और त्रुटि सुधार के लिए नियंत्रक के साथ या विशेष रूप से बनाए गए फ्लैश फाइल तंत्र के साथ किया जाता है, जो मीडिया पर लिखता है, और NOR फ्लैश ब्लॉक के लंबे समय तक डेटा को मिटाने के समय का वर्णन करता है। फ्लैश फ़ाइल तंत्र के पीछे मूल अवधारणा यह है कि जब फ्लैश स्टोर को अपडेट करना होता है, तो फाइल तंत्र बदले हुए डेटा की नई प्रति एक नए ब्लॉक में लिखता है, फाइल बिन्दुओं को पुनः अंकित करता है, फिर उसके बाद समय होने पर पुराने ब्लॉक को मिटा देता है। | ||

फ्लैश फाइल तंत्र का उपयोग व्यावहारिक रूप में केवल मेमोरी तकनीक युक्ति (MDT) के लिए किया जाता है, जो ऐसे अन्तर्निहित फ्लैश मेमोरी होते हैं, जिनमें नियंत्रक नहीं होता है। हटाने योग्य फ्लैश मेमोरी कार्ड (removable memory cards), एसएसडी (SSD), ईएमएमसी/ईयूएफएस (eMMC/eUFS) चिपों और यूएसबी फ्लैश ड्राइव (USB flash drive) में घिसाव स्तर और त्रुटि सुधार के लिए पहले से ही नियंत्रक लगे होते हैं, इसलिए इनमें एक विशिष्ट फ्लैश फाइल तंत्र का उपयोग नया लाभ नहीं प्रदान कर सकता है। | |||

== क्षमता == | == क्षमता == | ||

| Line 419: | Line 419: | ||

{{Main|List of flash memory controller manufacturers|List of solid-state drive manufacturers}} | {{Main|List of flash memory controller manufacturers|List of solid-state drive manufacturers}} | ||

वर्ष 2019 की पहली तिमाही तक सबसे बड़े NAND फ्लैश मेमोरी निर्माता निम्न थे।<ref>{{cite web |title=NAND Flash manufacturers' market share 2019 |url=https://www.statista.com/statistics/275886/market-share-held-by-leading-nand-flash-memory-manufacturers-worldwide/ |website=[[Statista]] |access-date=3 July 2019}}</ref> | वर्ष 2019 की पहली तिमाही तक सबसे बड़े NAND फ्लैश मेमोरी निर्माता निम्न थे।<ref>{{cite web |title=NAND Flash manufacturers' market share 2019 |url=https://www.statista.com/statistics/275886/market-share-held-by-leading-nand-flash-memory-manufacturers-worldwide/ |website=[[Statista]] |access-date=3 July 2019}}</ref> | ||

# | #सैमसंग इलेक्ट्रॉनिक्स {{ndash}} 34.9% | ||

# | #किओक्सिया (Kioxia) {{ndash}} 18.1% | ||

# | #पश्चिमी डिजिटल निगम {{ndash}} 14% | ||

#Micron प्रौद्योगिकी {{ndash}} 13.5% | #माइक्रोन (Micron) प्रौद्योगिकी {{ndash}} 13.5% | ||

#SK | #SK हाइनिक्स {{ndash}} 10.3% | ||

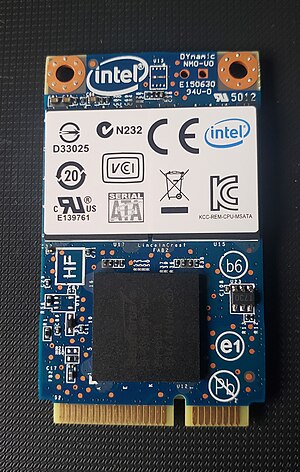

# | #इन्टेल {{ndash}} 8.7% (नोट: SK Hynix ने 2021 के अंत में इंटेल के NAND व्यवसाय का अधिग्रहण किया)<ref>{{cite news | ||

|url=https://www.reuters.com/technology/sk-hynix-completes-first-phase-9-bln-intel-nand-business-buy-2021-12-29/ | |url=https://www.reuters.com/technology/sk-hynix-completes-first-phase-9-bln-intel-nand-business-buy-2021-12-29/ | ||

|title=SK Hynix completes first phase of $9 bln Intel NAND business buy |newspaper=Reuters |date=29 December 2021 |access-date=June 27, 2022}}</ref> | |title=SK Hynix completes first phase of $9 bln Intel NAND business buy |newspaper=Reuters |date=29 December 2021 |access-date=June 27, 2022}}</ref> | ||

वर्ष 2022 की पहली तिमाही तक सैमसंग सबसे बड़ा NAND फ्लैश मेमोरी निर्माता है।<ref>{{cite web | |||

|url=https://businessquant.com/nand-revenue-by-manufacturer-worldwide#:~:text=NAND%20manufacturers%20collectively%20generated%20%2417.91,third%20and%20fourth%20positions%2C%20respectively. | |url=https://businessquant.com/nand-revenue-by-manufacturer-worldwide#:~:text=NAND%20manufacturers%20collectively%20generated%20%2417.91,third%20and%20fourth%20positions%2C%20respectively. | ||

|title=NAND Revenue by Manufacturers Worldwide (2014-2022) |date=26 May 2020 |access-date=June 27, 2022}}</ref> | |title=NAND Revenue by Manufacturers Worldwide (2014-2022) |date=26 May 2020 |access-date=June 27, 2022}}</ref> | ||

| Line 553: | Line 553: | ||

!2,321,421,837,044+ अरब कोश | !2,321,421,837,044+ अरब कोश | ||

|} | |} | ||

एकल फ्लैश मेमोरी चिपों को छोड़कर फ्लैश मेमोरी को माइक्रोकंट्रोलर (MCU) चिपों और सिस्टम-ऑन-चिप (SoC) उपकरणों में भी अन्तर्निहित (embed) किया जाता है।<ref name="arm">{{cite web |last1=Yiu |first1=Joseph |title=Embedded Processors |url=https://community.arm.com/cfs-file/__key/telligent-evolution-components-attachments/01-2142-00-00-00-00-70-29/Embedded-SoC-Design-for-High-Reliability-Systems-1.02.pdf |website=[[Arm Holdings|ARM]] |publisher=Embedded World 2015 |date=February 2015 |access-date=23 October 2019}}</ref> फ्लैश मेमोरी एआरएम चिप्स में अंतर्निहित है<ref name="arm"/>, जिसने 2019 तक दुनिया भर में 150 बिलियन यूनिट्स की बिक्री की है<ref>{{cite news |last1=Smith |first1=Ryan |title=Arm TechCon 2019 Keynote Live Blog (Starts at 10am PT/17:00 UTC) |url=https://www.anandtech.com/show/14959/arm-techcon-2019-keynote-live-blog |access-date=15 October 2019 |work=[[AnandTech]] |date=8 October 2019}}</ref>, और प्रोग्रामेबल सिस्टम-ऑन-चिप (पीएसओसी) उपकरणों में, जो 2012 तक 1.1 बिलियन यूनिट्स की बिक्री कर चुके हैं।<ref name="cypress">{{cite web |title=2011 Annual Report |url=http://investors.cypress.com/static-files/62237288-5a22-4903-9ef8-3719d37ea699 |website=[[Cypress Semiconductor]] |year=2012 |access-date=16 October 2019 |archive-date=16 October 2019 |archive-url=https://web.archive.org/web/20191016115727/http://investors.cypress.com/static-files/62237288-5a22-4903-9ef8-3719d37ea699 |url-status=dead }}</ref> इसके बाद कम से कम 151.1 अरब अन्तर्निहित (embedded) फ्लैश मेमोरी वाली MCU और SoC चिपों की चिपों की बिक्री हुई, और वर्ष 2015 तक 45.4 अरब प्रसिद्ध एकल फ्लैश चिप बिक्री के अलावा, कम से कम 196.5 बिलियन फ्लैश मेमोरी वाले चिपों की बिक्री हुई। | |||

== फ्लैश मापनीयता (Flash Scalability) == | == फ्लैश मापनीयता (Flash Scalability) == | ||

Revision as of 15:47, 31 August 2022

| कंप्यूटर मेमोरी और डेटा स्टोरेज प्रकार |

|---|

| वाष्पशील |

| गैर-वाष्पशील |

फ्लैश मेमोरी (Flash Memory) कंप्यूटर मेमोरी संग्रह का एक ऐसा इलेक्ट्रॉनिक अवाष्पशील माध्यम है, जिसे विद्युत रूप से मिटाकर पुनः तैयार किया जा सकता है। NOR फ़्लैश और NAND फ़्लैश, दो मुख्य प्रकार की फ्लैश मेमोरी हैं, जिन्हें NOR और NAND लॉजिक गेट (तर्कद्वार) के नाम से जाना जाता है। ये दोनों मेमोरी एक ही बनावट के कोश का उपयोग करते हैं, जिसमें MOSFETs जैसे चलायमान (floating) गेट सम्मिलित हैं। ये परिपथ स्तर पर भिन्न होते हैं, जो इस बात पर निर्भर करता है कि बिट रेखा (bit line) या शब्द रेखा (word line) की स्थिति को उच्च खींचा गया है या निम्न: बिट रेखा और शब्द रेखा के बीच का संबंध NAND फ़्लैश में NAND गेट जैसा और NOR फ्लैश में NOR गेट जैसा दिखता है।

फ्लैश मेमोरी एक प्रकार की चलायमान-गेट मेमोरी है। इसका आविष्कार वर्ष 1980 में तोशिबा (Toshiba) में हुआ था और जो कि EEPROM तकनीक पर आधारित है। तोशिबा ने वर्ष 1987 में फ्लैश मेमोरी का विपणन (marketing) शुरू किया।[1] EPROMs को पुनः लिखने से पहले पूर्णतः मिटाना पड़ता था। हालांकि NAND फ्लैश मेमोरी को पेज (या ब्लॉक) में लिखा, पढ़ा और मिटाया जा सकता है, जो सामान्पयतः पूरे उपकरण की तुलना में अत्यंत छोटे होते हैं। NOR फ्लैश मेमोरी मिटाए गए स्थान पर केवल एक ही मशीन शब्द को लिखने और स्वतंत्र रूप से पढ़ने की अनुमति देती है। एक फ्लैश मेमोरी उपकरण में सामान्यतः प्रत्येक फ्लैश मेमोरी कोशों को पकड़े हुए एक या एक से अधिक फ्लैश मेमोरी चिपों (Chips) के साथ-साथ एक अलग फ्लैश मेमोरी नियंत्रक चिप होती है।

NAND फ्लैश मेमोरी का प्रयोग मुख्य रूप से मेमोरी कार्ड (memory card), यूएसबी फ्लैश ड्राइव (USB flash drive), वर्ष 2009 के बाद से उत्पादित ठोस अवस्था ड्राइव (solid-state drives), फ़ीचर फोन, स्मार्टफोन और इसी तरह के उत्पादों में सामान्य भंडारण (storage) और डेटा के हस्तांतरण (data transferring) के लिए जाता है। NAND या NOR फ्लैश मेमोरी का उपयोग प्रायः कई डिजिटल उत्पादों में विन्यास डेटा (configuration data) को संग्रहीत करने के लिए किया जाता है, जो पहले EEPROM या बैटरी-संचालित स्थिर RAM (static RAM) द्वारा संभव था। फ्लैश मेमोरी में एक प्रमुख नुकसान यह है कि यह एक विशिष्ट पृष्ठ में अपेक्षाकृत कम लेखन-चक्रों को ही सहन कर सकता है।[2]

फ्लैश मेमोरी[3] का उपयोग कंप्यूटर, पीडीए (PDA), डिजिटल ऑडियो प्लेयर (digital audio players), डिजिटल कैमरा (digital camera), मोबाइल फोन, सिंथेसाइज़र (synthesizers), वीडियो गेम, वैज्ञानिक यंत्रों, औद्योगिक रोबोटिक्स (industrial robotics) और चिकित्सीय इलेक्ट्रॉनिक्स में किया जाता है। फ्लैश मेमोरी तेजी से अध्ययन करती है, लेकिन यह स्थैतिक RAM या ROM जितनी तेज नहीं होती है। इसके यांत्रिक आघात प्रतिरोध (mechanical shock resistance) के कारण वहनीय (portable) उपकरणों में फ्लैश मेमोरी का उपयोग करना ज्यादा पसंद किया जाता है क्योंकि यांत्रिक ड्राइव (mechanical drives) यांत्रिक क्षति के लिए अधिक उन्मुख (ready) होते हैं।

फ़्लैश मेमोरी में डेटा को मिटाने के लिए उपयोग किए जाने वाले बड़े आकार के खाने (blocks) डेटा मिटाने धीमे के कारण इसे गैर-फ्लैश EEPROM में बड़ी मात्रा में डेटा लिखते समय एक महत्वपूर्ण गति लाभ देते हैं। फ्लैश मेमोरी की लागत वर्ष 2019 तक (As of 2019[update]) बाइट-प्रोग्रामेबल EEPROM की तुलना में बहुत कम थी और जहाँ भी तंत्र (system) को महत्वपूर्ण मात्रा में अवाष्पशील ठोस-अवस्था भंडारण की आवश्यकता होती थी, इसका उपयोग प्रमुख रूप से किया जाता था। हालांकि EEPROMs का उपयोग अभी भी क्रमिक उपस्थिति का पता लगाने जैसे अनुप्रयोगों में किया जाता है, जिनके लिए केवल अल्प मात्रा में भंडारण की आवश्यकता होती है।[4][5]

फ्लैश मेमोरी पैकेज थ्रू-सिलिकॉन वाया (through-silicon via) और प्रति डाई 3डी टीएलसी NAND कोशों (3D TLC NAND cells) की कई दर्जन परतों के साथ डाई स्टैकिंग (die stacking) का एक साथ उपयोग कर सकते हैं ताकि 16 स्टैक्ड डाई (stacked die) का उपयोग करके प्रति पैकेज 1 टेबीबाइट (tebibyte) तक की क्षमता प्राप्त की जा सके और पैकेज के अन्दर एक एकीकृत फ्लैश नियंत्रक की एक अलग डाई के रूप में उपयोग किया जा सके।[6][7][8][9]

इतिहास

पृष्ठभूमि (Background)

फ्लैश मेमोरी की उत्पत्ति का पता चलायमान-गेट ट्रांजिस्टर (floating-gate transistor) नाम से प्रचलित चलायमान-गेट MOSFET (FGMOS) के विकास से लगाया जा सकता है।[10][11] मूल MOSFET (मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) का आविष्कार वर्ष 1959 में मिस्र के अभियंता मोहम्मद एम. अताला (Mohamed M. Atalla) और कोरिया के अभियन्ता डावन काहंग (Dawon Kahng) ने बेल प्रयोगशाला में किया था।[12] डावन काहंग ने वर्ष 1967 में बेल प्रयोगशाला में चीन के अभियंता साइमन मिन सेज़ (Simon Min Sze) के साथ फ्लोटिंग-गेट MOSFET के रूप में एक परिवर्तन विकसित किया।[13] उन्होंने प्रस्तावित किया कि इसे प्रोग्रामेबल रीड-ओनली मेमोरी (Programmable Read Only Memory, PROM) के एक रूप को संग्रहीत (store) करने के लिए चलायमान-गेट मेमोरी कोशों (floating-gate memory cells) के रूप में इस्तेमाल किया जा सकता है, जो अवाष्पशील और पुन: लिखने योग्य है।[13]

1970 के दशक में चलायमान-गेट मेमोरी के प्रारम्भिक प्रकारों में EPROM (Erasable PROM) और EEPROM (Electrically Erasable PROM) सम्मिलित थे।[13] हालांकि, प्रारम्भिक चलायमान-गेट मेमोरी में डेटा के प्रत्येक बिट (bit) के लिए एक मेमोरी कोश बनाने में अभियंताओं की आवश्यकता होती है, जो अत्यंत बोझिल[14], धीमा[15], और महंगा साबित हुआ, जो 1970 के दशक में सैन्य उपकरणों और प्रारम्भिक प्रायोगिक मोबाइल फोन जैसे विशिष्ट अनुप्रयोगों के लिए चलायमान-गेट मेमोरी को प्रतिबंधित करता था।[10]

आविष्कार और व्यावसायीकरण

तोशिबा (Toshiba) के लिए काम करते हुए फ़ुजियो मासुओका (Fujio Masuoka) ने एक नए प्रकार की चलायमान-गेट मेमोरी का प्रस्ताव रखा, जिससे कोशों के समूह से जुड़े एकल तार पर विभव (voltage) लगाकर मेमोरी के पूरे भाग (section) को जल्दी और आसानी से मिटाया जा सकता है।[10] इस प्रकार वर्ष 1980 में तोशिबा (Toshiba) में मासुओका (Masuoka) के फ्लैश मेमोरी का आविष्कार हुआ।[15][16][17] तोशिबा के अनुसार, फ्लैश नाम का सुझाव मासुओका के सहयोगी शोजी एरीज़ुमी (Shōji Ariizumi) ने दिया था, क्योंकि मेमोरी के डेटा की मिटाने की प्रक्रिया ने उन्हें एक कैमरे के फ्लैश की याद दिला दी थी।[18] मासुओका और उनके सहकर्मियों ने वर्ष 1984 में NOR फ्लैश का आविष्कार प्रस्तुत किया,[19][20] और उसी समय NAND फ्लैश को सैन फ्रांसिस्को (San Francisco) में आयोजित IEEE 1987 अंतर्राष्ट्रीय इलेक्ट्रॉन युक्ति संगोष्ठी (IEDM) में प्रस्तुत किया।[21]

तोशिबा ने NAND फ्लैश मेमोरी को वर्ष 1987 में व्यावसायिक रूप से प्रस्तुत किया।[1][13] इंटेल कॉरपोरेशन (Intel Corporation) ने वर्ष 1988 में पहला व्यावसायिक NOR फ्लैश चिप प्रस्तुत किया।[22] NOR आधारित फ्लैश में मिटाने और लिखने में अधिक समय लगता है, लेकिन यह पूर्ण पता और डेटा बसें (data buses) प्रदान करता है, जिससे किसी भी मेमोरी के किसी भी स्थान पर यादृच्छिक पहुंच की अनुमति मिलती है। यह पुराने रीड-ओनली मेमोरी (ROM) चिप के लिए एक उपयुक्त प्रतिस्थापक बनता है, जिसका उपयोग प्रोग्राम कोड (program code) को संग्रह करने के लिए किया जाता है, जिसे शायद ही कभी सम्पादित (update) करने की आवश्यकता होती है, जैसे कंप्यूटर के BIOS या सेट-टॉप बक्से (set-top box) प्रक्रिया यन्त्र सामग्री (firmware)। इसकी ऑन-चिप फ्लैश मेमोरी (on-chip flash memory) के लिए डेटा को मिटाने की क्षमता न्यूनतम 100 चक्रों से लेकर,[23] एक अधिक विशिष्ट 10,000 चक्र, 1,00,000 चक्र और अधिकतम 10,00,000 चक्रों तक हो सकती है।[24] NOR-आधारित फ़्लैश प्रारंभिक फ़्लैश-आधारित हटाने योग्य मीडिया का आधार था और कॉम्पैक्ट फ्लैश (CompactFlash) मूल रूप से इस पर आधारित था, हालांकि बाद में कम खर्चीले NAND फ्लैश ने इन कार्डों का स्थान ले लिया।

NAND फ्लैश ने मिटाने और लिखने के समय को कम कर दिया है, और इसमें प्रति सेल कम चिप क्षेत्र की आवश्यकता होती है, इस प्रकार ये अधिक भंडारण घनत्व (storage density) और NOR फ्लैश की तुलना में प्रति बिट कम लागत की अनुमति प्रदान करता है। हालाँकि, NAND फ़्लैश का I/O अंतर्पृष्ठ (input-output interface) यादृच्छिक-पहुँच बाहरी पता बस (random-access external address bus) प्रदान नहीं करता है। बल्कि, डेटा को खंड-वार (block-wise) पढ़ा जाना चाहिए, जिसमें सैकड़ों से हजारों बिट्स के विशिष्ट खंड (block) आकार होते हैं। यह NAND फ्लैश को प्रोग्राम ROM के प्रतिस्थापन के रूप में अनुपयुक्त बनाता है, क्योंकि अधिकांश माइक्रोप्रोसेसरों (microprocessors) और माइक्रोकंट्रोलर्स (microcontrollers) को बाइट-स्तरीय यादृच्छिक-पहुँच की आवश्यकता होती है। इस प्रकार, NAND फ्लैश भी हार्ड डिस्क (hard disk) ऑप्टिकल मीडिया (optical media) जैसे अन्य द्वितीयक डेटा भंडारण उपकरणों के समान ही है, और इस प्रकार यह मेमोरी कार्ड और ठोस-अवस्था ड्राइव (SSD) जैसे बड़े पैमाने पर भंडारण उपकरणों में उपयोग के लिए अत्यधिक उपयुक्त है। फ्लैश मेमोरी कार्ड और ठोस-अवस्था ड्राइव (SSD) कई NAND फ्लैश मेमोरी चिपों का उपयोग करके डेटा का भण्डारण करते हैं।

वर्ष 1995 में जारी स्मार्टमीडिया (SmartMedia) पहला NAND-आधारित हटाने योग्य मेमोरी कार्ड प्रारूप था। कई अन्य लोगों ने मल्टीमीडिया कार्ड (MultiMediaCard), सिक्योर डिजिटल (secure digital), मेमोरी छड़ (memory stick) और एक्सडी-पिक्चर कार्ड (xD-Picture Card) आदि के उपयोग को पसंद किया।

बाद के विकास

RS-MMC, MINISD और माइक्रोएसडी सहित मेमोरी कार्ड प्रारूपों की एक नई पीढ़ी में बेहद छोटे निर्माण कारक (form factors) हैं। उदाहरण के लिए, माइक्रोएसडी कार्ड (microSD card) का क्षेत्रफल लगभग 1.5 वर्गसेमी० और मोटाई 1 मिमी० से कम है।

NAND फ्लैश ने कई प्रमुख तकनीकों के परिणामस्वरूप मेमोरी घनत्व के महत्वपूर्ण स्तरों को हासिल किया है, जिनका व्यावसायीकरण 2000 के दशक के अंत से 2010 के प्रारंभ तक किया गया था।[24]

बहु-स्तरीय कोश (MLC) तकनीक प्रत्येक मेमोरी कोश में एक से अधिक बिट स्टोर करती है। NEC ने वर्ष 1998 में बहु-स्तरीय सेल (MLC) तकनीक का प्रदर्शन किया, जिसमें 80MB की फ्लैश मेमोरी चिप में 2 बिट प्रति सेल का भंडारण किया जा सकता था।[25] एसटीमाइक्रोइलेक्ट्रॉनिक (STmicroelectronics) ने भी वर्ष 2000 में 64MB की NOR फ्लैश मेमोरी चिप के साथ बहु-स्तरीय कोश तकनीक प्रस्तुत की।[26] तोशिबा (Toshiba) और सैनडिस्क (SanDisk) ने भी वर्ष 2009 में QLC तकनीक के साथ NAND फ्लैश चिप प्रस्तुत किए, जिसमें 4 बिट प्रति कोश का भंडारण और 64 Gbit की क्षमता थी।[27][28] सैमसंग इलेक्ट्रॉनिक्स ने त्रि-स्तरीय कोश (TLC) तकनीक प्रस्तुत की,जिसमें 3-बिट प्रति कोश का भंडारण किया जा सकता था। कम्पनी ने त्रि-स्तरीय कोश (TLC) तकनीक के साथ वर्ष 2010 में बड़े पैमाने पर NAND चिपों का उत्पादन शुरू कर दिया।[29]

चार्ज ट्रैप फ्लैश (Charge Trap Flash)

चार्ज ट्रैप फ्लैश (CTF) तकनीक पॉलीसिलिकॉन (polysilicon) चलायमान गेट को प्रतिस्थापित करती है, जिसमें ऊपर एक अवरोधक (blocking) गेट ऑक्साइड और नीचे एक टनलिंग ऑक्साइड (tunneling oxide) के बीच एक विद्युत-रोधी सिलिकॉन नाइट्राइड (silicon nitride) एक परत फंसी होती है। CTF में सैद्धांतिक रूप से इलेक्ट्रॉन रिसाव की संभावना कम होती है, जिससे डेटा प्रतिधारण में सुधार होता है।[30][31][32][33][34][35]

चूँकि चार्ज ट्रैप फ्लैश पॉलीसिलिकॉन को विद्युत रोधी नाइट्राइड के साथ प्रतिस्थापित करता है, अतः यह छोटे कोशों और उच्च सहनशक्ति (कम गिरावट या घिसाव) की अनुमति प्रदान है। हालांकि, इलेक्ट्रॉनों के नाइट्राइड में फंस कर जमा होने के कारण इसमें गिरावट आ सकती है। उच्च तापमान पर रिसाव तेज हो जाता है क्योंकि बढ़ते तापमान के साथ इलेक्ट्रॉन अधिक उत्तेजित हो जाते हैं। हालांकि चार्ज ट्रैप फ्लैश (CTF) तकनीक अभी भी एक टनलिंग ऑक्साइड और अवरुद्ध परत का उपयोग करती है, जो इस तकनीक के कमजोर बिंदु हैं, क्योंकि वे अभी भी सामान्य तरीकों से क्षतिग्रस्त हो सकते हैं, जिनमें टनलिंग ऑक्साइड में अत्यधिक उच्च विद्युत क्षेत्रों के कारण और अवरुद्ध परत में एनोड हॉट होल इंजेक्शन (AHHI) के कारण गिरावट आ सकती है।[36][37]

फ्लैश मेमोरी की सीमित सहनशक्ति ही ऑक्साइड के क्षरण या घिसाव का कारण होती है, और बढ़ते क्षरण के साथ डेटा प्रतिधारण कम हो जाता है अर्थात् डेटा हानि की संभावना बढ़ जाती है, क्योंकि ऑक्साइड में क्षरण के कारण ये अपनी विद्युत अवरोधक विशेषताओं को खो देते हैं। ऑक्साइड को इलेक्ट्रॉनों से अवरोधित करना चाहिए, जिससे लीक होने के कारण होने वाली डेटा हानि को रोका जा सके।

एन. कोडामा (N. Kodama), के. ओयामा (K. Oyama) और हिरोकी शिराई (Hiroki Shirai) सहित एनईसी (NEC) के कई शोधकर्ताओं ने चार्ज ट्रैप तकनीक के साथ एक प्रकार की फ्लैश मेमोरी को प्रस्तुत किया।[38] सैफुन अर्धचालक (बाद में स्पैनसियन द्वारा अधिग्रहित) के बोज़ ईटन (Boaz Eitan) ने वर्ष 1998 में एनआरओएम (NROM) नामक एक फ्लैश मेमोरी तकनीक का एकाधिकरण (patent) कराया, जिसने पारंपरिक फ्लैश मेमोरी की बनावट में उपयोग किए जाने वाले चलायमान गेट को प्रतिस्थापित करके चार्ज ट्रैपिंग परत का लाभ उठाया।[39] रिचर्ड एम. फास्टो (Richard M. Fastow), मिस्र के अभियंता खालिद जेड. अहमद (Khaled Z. Ahmed) और जॉर्डन (Jordan) के अभियंता समीर हदद (Sameer Haddad)(जो बाद में स्पैन्सियन में शामिल हो गए) के नेतृत्व में एक उन्नत सूक्ष्म युक्ति (AMD) अनुसंधान टीम ने NOR फ्लैश मेमोरी कोशों के लिए एक चार्ज-ट्रैपिंग तंत्र प्रस्तुत किया।[40] चार्ज ट्रैप फ्लैश को बाद में वर्ष 2002 में एएमडी (AMD) और फुजित्सु (Fujitsu) द्वारा व्यवसायीकृत किया गया।[41] 3D V-NAND (वर्टिकल NAND) तकनीक 3D चार्ज ट्रैप फ्लैश (CTF) तकनीक का उपयोग करके NAND फ्लैश मेमोरी कोश को एक चिप के भीतर लंबवत रूप से संग्रहित करती है। 3D V-NAND (वर्टिकल NAND) तकनीक की घोषणा सर्वप्रथम वर्ष 2007 में तोशिबा द्वारा की गई थी[43] और 24 परतों वाले पहले उपकरण का व्यावसायीकरण सर्वप्रथम वर्ष 2013 में सैमसंग इलेक्ट्रॉनिक्स (Samsung Electronics) द्वारा किया गया था।।[42][43]

त्रिविमीय एकीकृत परिपथ प्रौद्योगिकी (3D integrated circuit technology)

3डी एकीकृत परिपथ (3D IC) तकनीक एकीकृत परिपथ (IC) चिपों को एकल 3D एकीकृत परिपथ (3D IC) चिप पैकेज में लंबवत रूप से संग्रहित करती है।[24] तोशिबा ने अप्रैल 2007 में NAND फ्लैश मेमोरी के लिए 3डी एकीकृत परिपथ तकनीक पेश की, जब उन्होंने 16 GB ईएमएमसी (eMMC) अनुवर्ती (उत्पाद संख्या THGAM0G7D8DBAI6 जो प्रायः उपभोक्ता वेबसाइटों पर संक्षिप्त रूप में THGAM लिखा होता है) अंतर्निहित NAND फ्लैश मेमोरी चिप की शुरुआत की, जिसे आठ 2 जीबी NAND फ्लैश चिपों के संग्रहण के साथ निर्मित किया गया था।[44] हाइनिक्स अर्धचालक (अब SK Hynix के नाम से जाना जाता है) ने सितंबर 2007 में 24-परतों की 3डी एकीकृत परिपथ तकनीक प्रस्तुत की, जिसमें 16 जीबी फ्लैश मेमोरी चिप थी, और जिसे 24 NAND फ्लैश चिपों के संग्रहण के साथ वेफर बंधन (wafer bonding) प्रक्रिया का उपयोग करके निर्मित किया गया था।।[45] तोशिबा ने भी वर्ष 2008 में अपनी 32 जीबी टीएचजीबीएम (THGBM) फ्लैश चिप के लिए आठ-परत के 3डी एकीकृत परिपथ का इस्तेमाल किया था।[46] तोशिबा ने वर्ष 2010 में अपने 128 GB THGBM2 फ्लैश चिप के लिए 16 परतों वाले 3डी एकीकृत परिपथ का उपयोग किया, जिसे 16, 8 जीबी चिपों के साथ निर्मित किया गया था।[47] 3डी एकीकृत परिपथ 2010 के दशक में मोबाइल उपकरणों में NAND फ्लैश मेमोरी के लिए व्यापक व्यावसायिक उपयोग में आया।[24]

अगस्त 2017 तक 400 जीबी (400 billion bytes) तक की क्षमता वाले माइक्रोएसडी कार्ड उपलब्ध थे।[48][49] उसी वर्ष, सैमसंग ने अपनी 3डी ऊर्ध्वाधर-NAND और टीएलसी (TLC) प्रौद्योगिकियों के साथ 3डी एकीकृत परिपथ चिप संग्रहण को मिलाकर आठ 64-परतों वाली ऊर्ध्वाधर NAND चिपों के साथ अपनी 512 जीबी KLUFG8R1EM फ्लैश मेमोरी चिप का निर्माण किया।[50] सैमसंग ने वर्ष 2019 में आठ 96-परतों वाली ऊर्ध्वाधर-NAND चिपों और क्यूएलसी (QLC) तकनीक के साथ अपनी 1024 जीबी फ्लैश चिप का उत्पादन किया।[51][52]

ऑपरेशन के सिद्धांत

फ्लैश मेमोरी फ्लोटिंग-गेट ट्रांजिस्टर से बने मेमोरी कोशिकाओं की एक सरणी में जानकारी संग्रहित करती है।एकल-स्तरीय सेल (SLC) उपकरणों में, प्रत्येक सेल केवल एक बिट जानकारी को संग्रहीत करता है।मल्टी-लेवल सेल (MLC) डिवाइस, जिनमें ट्रिपल-लेवल सेल (TLC) डिवाइस शामिल हैं, प्रति सेल एक से अधिक बिट स्टोर कर सकते हैं।

फ्लोटिंग गेट प्रवाहकीय हो सकता है (आमतौर पर फ्लैश मेमोरी के अधिकांश प्रकार में पॉलीसिलिकॉन) या गैर-आचरण (जैसा कि सोनोस फ्लैश मेमोरी में)।[53]

फ्लोटिंग-गेट MOSFET

फ्लैश मेमोरी में, प्रत्येक मेमोरी सेल एक मानक धातु-ऑक्साइड-सेमिकंडक्टर फ़ील्ड-इफेक्ट ट्रांजिस्टर (MOSFET) जैसा दिखता है, सिवाय इसके कि ट्रांजिस्टर के बजाय एक के बजाय दो गेट हैं।कोशिकाओं को एक विद्युत स्विच के रूप में देखा जा सकता है जिसमें वर्तमान दो टर्मिनलों (स्रोत और नाली) के बीच प्रवाह होता है और एक फ्लोटिंग गेट (एफजी) और एक नियंत्रण गेट (सीजी) द्वारा नियंत्रित किया जाता है।सीजी अन्य एमओएस ट्रांजिस्टर में गेट के समान है, लेकिन इसके नीचे, एक ऑक्साइड परत द्वारा चारों ओर अछूता एफजी है।FG CG और MOSFET चैनल के बीच परस्पर जुड़ा हुआ है।क्योंकि एफजी इसकी इन्सुलेट परत द्वारा विद्युत रूप से अलग किया जाता है, उस पर रखे गए इलेक्ट्रॉनों को फंसाया जाता है।जब एफजी को इलेक्ट्रॉनों के साथ चार्ज किया जाता है, तो यह चार्ज सीजी से विद्युत क्षेत्र को स्क्रीन करता है, इस प्रकार, थ्रेसहोल्ड वोल्टेज को बढ़ाता है (वी)T1) सेल का।इसका मतलब है कि अब एक उच्च वोल्टेज (v)T2) चैनल प्रवाहकीय बनाने के लिए सीजी पर लागू किया जाना चाहिए।ट्रांजिस्टर से एक मान पढ़ने के लिए, थ्रेशोल्ड वोल्टेज (v) के बीच एक मध्यवर्ती वोल्टेजT1 & VT2) CG पर लागू होता है।यदि चैनल इस इंटरमीडिएट वोल्टेज पर आयोजित करता है, तो एफजी को अनचाहे होना चाहिए (यदि यह चार्ज किया गया था, तो हमें चालन नहीं मिलेगा क्योंकि मध्यवर्ती वोल्टेज वी से कम हैT2), और इसलिए, एक तार्किक 1 गेट में संग्रहीत है। यदि चैनल इंटरमीडिएट वोल्टेज पर संचालन नहीं करता है, तो यह इंगित करता है कि एफजी चार्ज किया जाता है, और इसलिए, एक तार्किक 0 गेट में संग्रहीत है। एक तार्किक 0 या 1 की उपस्थिति को यह निर्धारित करके महसूस किया जाता है कि क्या ट्रांजिस्टर के माध्यम से प्रवाह प्रवाह होता है जब सीजी पर मध्यवर्ती वोल्टेज का दावा किया जाता है। एक बहु-स्तरीय सेल डिवाइस में, जो प्रति सेल एक से अधिक बिट को संग्रहीत करता है, वर्तमान प्रवाह की मात्रा को संवेदी (केवल इसकी उपस्थिति या अनुपस्थिति के बजाय), एफजी पर अधिक सटीक रूप से आवेश का स्तर निर्धारित करने के लिए संवेदी है।

फ्लोटिंग गेट मोसफेट्स का नाम इसलिए रखा गया है क्योंकि फ्लोटिंग गेट और सिलिकॉन के बीच एक विद्युत रूप से इन्सुलेट टनल ऑक्साइड परत है, इसलिए गेट सिलिकॉन के ऊपर तैरता है। ऑक्साइड इलेक्ट्रॉनों को फ्लोटिंग गेट तक सीमित रखता है। गिरावट या पहनने (और फ्लोटिंग गेट फ्लैश मेमोरी का सीमित धीरज) ऑक्साइड द्वारा अनुभव किए गए अत्यधिक उच्च विद्युत क्षेत्र (10 मिलियन वोल्ट प्रति सेंटीमीटर) के कारण होता है। इस तरह के उच्च वोल्टेज घनत्व अपेक्षाकृत पतले ऑक्साइड में समय के साथ परमाणु बॉन्ड को तोड़ सकते हैं, धीरे -धीरे अपने विद्युत रूप से इन्सुलेट गुणों को नीचा दिखाते हैं और इलेक्ट्रॉनों को फ्लोटिंग गेट से ऑक्साइड में स्वतंत्र रूप से (रिसाव) से गुजरने और गुजरने की अनुमति देते हैं, जिससे डेटा हानि की संभावना बढ़ जाती है। चूंकि इलेक्ट्रॉनों (जिनकी मात्रा का उपयोग विभिन्न चार्ज स्तरों का प्रतिनिधित्व करने के लिए किया जाता है, प्रत्येक एमएलसी फ्लैश में बिट्स के एक अलग संयोजन को सौंपा गया है) आम तौर पर फ्लोटिंग गेट में होते हैं। यही कारण है कि डेटा प्रतिधारण कम हो जाता है और बढ़ती गिरावट के साथ डेटा हानि का जोखिम बढ़ जाता है।[54][55][34][56][57]

फाउलर -NOR्डहाइम टनलिंग

नियंत्रण द्वार से और फ्लोटिंग गेट में इलेक्ट्रॉनों को स्थानांतरित करने की प्रक्रिया को फाउलर -NOR्डहाइम टनलिंग कहा जाता है, और यह मौलिक रूप से MOSFET की दहलीज वोल्टेज को बढ़ाकर सेल की विशेषताओं को बदल देता है।यह, बदले में, ड्रेन-सोर्स करंट को बदलता है जो किसी दिए गए गेट वोल्टेज के लिए ट्रांजिस्टर के माध्यम से बहता है, जिसका उपयोग अंततः एक बाइनरी मूल्य को एन्कोड करने के लिए किया जाता है।फाउलर-नॉर्डहाइम टनलिंग प्रभाव प्रतिवर्ती है, इसलिए इलेक्ट्रॉनों को फ्लोटिंग गेट से जोड़ा या हटाया जा सकता है, पारंपरिक रूप से लेखन और मिटाने के रूप में जाना जाता है।[58]

आंतरिक चार्ज पंप

अपेक्षाकृत उच्च प्रोग्रामिंग और मिटाने वाले वोल्टेज की आवश्यकता के बावजूद, लगभग सभी फ्लैश चिप्स को आज केवल एक ही आपूर्ति वोल्टेज की आवश्यकता होती है और उच्च वोल्टेज का उत्पादन होता है जो ऑन-चिप चार्ज पंपों का उपयोग करके आवश्यक होते हैं।

1.8 & nbsp; v NAND फ्लैश चिप द्वारा उपयोग की जाने वाली आधी से अधिक ऊर्जा चार्ज पंप में ही खो जाती है।चूंकि बूस्ट कन्वर्टर्स चार्ज पंपों की तुलना में स्वाभाविक रूप से अधिक कुशल होते हैं, इसलिए कम-शक्ति वाले इलेक्ट्रॉनिक्स विकसित करने वाले शोधकर्ता। कम-शक्ति वाले एसएसडी ने सभी शुरुआती फ्लैश चिप्स पर उपयोग किए जाने वाले दोहरे वीसीसी/वीपीपी आपूर्ति वोल्टेज पर लौटने का प्रस्ताव दिया है, जो सभी फ्लैश चिप्स के लिए उच्च वीपीपी वोल्टेज को ड्राइविंग करते हैं।एक एकल साझा बाहरी बूस्ट कनवर्टर के साथ एक SSD।[59][60][61][62][63][64][65][66] अंतरिक्ष यान और अन्य उच्च-विकिरण वातावरण में, ऑन-चिप चार्ज पंप फ़्लैश चिप का पहला हिस्सा है जो विफल होने के लिए है, हालांकि फ्लैश यादें काम करना जारी रखेगी – पढ़ने के मोड में – बहुत अधिक विकिरण स्तर पर।[67]

और न ही फ्लैश

NOR फ्लैश में, प्रत्येक सेल में एक छोर सीधे जमीन से जुड़ा होता है, और दूसरा छोर सीधे एक बिट लाइन से जुड़ा होता है।इस व्यवस्था को और न ही फ्लैश कहा जाता है क्योंकि यह एक NOR & nbsp; गेट की तरह काम करता है: जब शब्द लाइनों में से एक (सेल के सीजी से जुड़ा हुआ) उच्च लाया जाता है, तो इसी स्टोरेज ट्रांजिस्टर आउटपुट बिट लाइन को कम खींचने के लिए कार्य करता है।न ही फ्लैश एक असतत गैर-वाष्पशील मेमोरी डिवाइस की आवश्यकता वाले एम्बेडेड अनुप्रयोगों के लिए पसंद की तकनीक बनी हुई है।[citation needed] कम पढ़ी जाने वाली विलंबता विशेषताओं और NBSP; डिवाइस एकल मेमोरी उत्पाद में प्रत्यक्ष कोड निष्पादन और डेटा संग्रहण दोनों के लिए अनुमति देते हैं।[68]

प्रोग्रामिंग

अपनी डिफ़ॉल्ट स्थिति में एक एकल-स्तरीय और न ही फ्लैश सेल तार्किक रूप से एक बाइनरी 1 मान के बराबर है, क्योंकि करंट कंट्रोल गेट के लिए एक उपयुक्त वोल्टेज के आवेदन के तहत चैनल के माध्यम से प्रवाहित होगा, ताकि बिटलाइन वोल्टेज को नीचे खींच लिया जाए।A NOR & nbsp; फ्लैश सेल को प्रोग्राम किया जा सकता है, या निम्नलिखित प्रक्रिया द्वारा बाइनरी 0 मान पर सेट किया जा सकता है:

- एक ऊंचा ऑन-वोल्टेज (आमतौर पर> 5 & nbsp; v) सीजी पर लागू होता है

- चैनल अब चालू हो गया है, इसलिए इलेक्ट्रॉन स्रोत से नाली तक प्रवाह कर सकते हैं (एक NMOS & nbsp; ट्रांजिस्टर मानते हुए)

- सोर्स-ड्रेन करंट कुछ उच्च ऊर्जा इलेक्ट्रॉनों को हॉट-इलेक्ट्रॉन इंजेक्शन नामक प्रक्रिया के माध्यम से एफजी पर इंसुलेटिंग लेयर के माध्यम से कूदने के लिए पर्याप्त रूप से उच्च है।

मिटाना

न ही फ्लैश सेल (इसे 1 राज्य को रीसेट करना) को मिटाने के लिए, सीजी और सोर्स टर्मिनल के बीच विपरीत ध्रुवीयता का एक बड़ा वोल्टेज लागू किया जाता है, जो क्वांटम टनलिंग के माध्यम से एफजी से इलेक्ट्रॉनों को खींचता है।आधुनिक और nbsp; फ्लैश मेमोरी चिप्स को मिटाकर सेगमेंट (अक्सर ब्लॉक या सेक्टर कहा जाता है) में विभाजित किया जाता है।ERASE ऑपरेशन केवल ब्लॉक-वार के आधार पर किया जा सकता है;एक इरेज़ सेगमेंट में सभी कोशिकाओं को एक साथ मिटा दिया जाना चाहिए।हालांकि, एनओआर कोशिकाओं की प्रोग्रामिंग, आमतौर पर एक समय में एक बाइट या शब्द किया जा सकता है।

NAND फ्लैश

NAND फ्लैश फ्लोटिंग-गेट ट्रांजिस्टर का भी उपयोग करता है, लेकिन वे एक तरह से जुड़े हुए हैं जो एक NAND & nbsp से मिलता-जुलता है; गेट: कई ट्रांजिस्टर श्रृंखला में जुड़े हुए हैं, और बिट लाइन को केवल तभी खींचा जाता है जब सभी शब्द लाइनें उच्च (ट्रांजिस्टर के ऊपर (ऊपर (ऊपर) खींची जाती हैं'वीT)।इन समूहों को तब कुछ अतिरिक्त ट्रांजिस्टर के माध्यम से NOR-स्टाइल बिट लाइन सरणी से उसी तरह से जोड़ा जाता है, जिस तरह से सिंगल ट्रांजिस्टर NOR & nbsp; फ्लैश में जुड़े होते हैं।

NOR फ्लैश की तुलना में, धारावाहिक-लिंक्ड समूहों के साथ एकल ट्रांजिस्टर को बदलने से अतिरिक्त स्तर का पता होता है।जबकि न ही & nbsp; फ़्लैश मेमोरी को पेज द्वारा संबोधित कर सकता है, फिर वर्ड, NAND & nbsp; फ्लैश इसे पेज, वर्ड और बिट द्वारा संबोधित कर सकता है।बिट-लेवल को संबोधित करने वाले बिट-सेरियल एप्लिकेशन (जैसे हार्ड डिस्क इम्यूलेशन), जो एक समय में केवल एक बिट तक पहुंचते हैं। Execute-in-place दूसरी ओर, अनुप्रयोगों को एक साथ एक साथ एक्सेस करने के लिए एक शब्द में प्रत्येक बिट की आवश्यकता होती है।इसके लिए शब्द-स्तरीय संबोधन की आवश्यकता होती है।किसी भी मामले में, बिट और वर्ड एड्रेसिंग मोड दोनों या तो या NAND या nbsp; फ्लैश के साथ संभव हैं।

डेटा पढ़ने के लिए, पहले वांछित समूह का चयन किया जाता है (उसी तरह जैसे कि एक एकल ट्रांजिस्टर को NOR सरणी से चुना जाता है)।अगला, अधिकांश शब्द लाइनें V के ऊपर खींची जाती हैंT एक प्रोग्राम किए गए बिट की, जबकि उनमें से एक को सिर्फ v पर खींच लिया गया हैT एक मिट गए बिट की।यदि चयनित बिट को प्रोग्राम नहीं किया गया है तो श्रृंखला समूह का संचालन (और बिट लाइन को कम खींचेगा)।

अतिरिक्त ट्रांजिस्टर के बावजूद, जमीन के तारों और बिट लाइनों में कमी एक सघन लेआउट और प्रति चिप अधिक भंडारण क्षमता की अनुमति देती है।।दोष-मुक्त होने की उम्मीद है)।निर्माता ट्रांजिस्टर के आकार को सिकोड़कर प्रयोग करने योग्य भंडारण की मात्रा को अधिकतम करने का प्रयास करते हैं।

विभिन्न वोल्टेज पर उनकी प्रतिक्रिया का विश्लेषण करके NAND फ्लैश कोशिकाओं को पढ़ा जाता है।[56]

लेखन और मिटाना

NAND फ्लैश लेखन के लिए सुरंग इंजेक्शन का उपयोग करता है और मिटाने के लिए सुरंग रिलीज करता है। NAND & NBSP; फ्लैश मेमोरी USB फ्लैश ड्राइव के रूप में जाना जाने वाले हटाने योग्य USB स्टोरेज डिवाइसेस का कोर बनाती है, साथ ही साथ अधिकांश मेमोरी कार्ड प्रारूप और ठोस-राज्य ड्राइव आज भी उपलब्ध हैं।

NAND फ्लैश की पदानुक्रमित संरचना एक सेल स्तर पर शुरू होती है जो तार, फिर पृष्ठ, ब्लॉक, विमान और अंततः एक मर जाती है। एक स्ट्रिंग कनेक्टेड NAND कोशिकाओं की एक श्रृंखला है जिसमें एक सेल का स्रोत अगले एक की नाली से जुड़ा होता है। NAND तकनीक के आधार पर, एक स्ट्रिंग में आमतौर पर 32 से 128 NAND कोशिकाएं होती हैं। स्ट्रिंग्स को उन पृष्ठों में व्यवस्थित किया जाता है, जिन्हें तब ब्लॉक में व्यवस्थित किया जाता है जिसमें प्रत्येक स्ट्रिंग को एक अलग लाइन से जोड़ा जाता है जिसे एक बिटलाइन (बीएल) कहा जाता है, जो स्ट्रिंग में एक ही स्थिति के साथ सभी कोशिकाएं एक वर्डलाइन (डब्ल्यूएल) द्वारा नियंत्रण द्वार के माध्यम से जुड़े होते हैं। एक निश्चित संख्या में ब्लॉक होते हैं जो एक ही बीएल के माध्यम से जुड़े होते हैं। एक फ्लैश डाई में एक या एक से अधिक विमान होते हैं, और परिधीय सर्किटरी जो सभी पढ़ने/ लिखने/ मिटाने के लिए आवश्यक होती है।

NAND फ्लैश की वास्तुकला का अर्थ है कि डेटा को पेजों में पढ़ा और प्रोग्राम किया जा सकता है, आमतौर पर 4 KIB और 16 KIB के आकार के बीच, लेकिन केवल पूरे ब्लॉकों के स्तर पर कई पृष्ठों और आकार में MB से मिलकर मिटाया जा सकता है। जब एक ब्लॉक को मिटा दिया जाता है, तो सभी कोशिकाओं को तार्किक रूप से 1 पर सेट किया जाता है। प्रोग्रामिंग द्वारा 0 पर सेट की गई कोई भी कोशिकाएं केवल पूरे ब्लॉक को मिटाकर 1 पर रीसेट कर सकती हैं। इसका मतलब यह है कि नए डेटा को एक पृष्ठ में प्रोग्राम किया जा सकता है जिसमें पहले से ही डेटा होता है, पृष्ठ की वर्तमान सामग्री और साथ ही नए डेटा को एक नए, मिटाए गए पृष्ठ पर कॉपी किया जाना चाहिए। यदि कोई उपयुक्त पृष्ठ उपलब्ध है, तो डेटा तुरंत इसे लिखा जा सकता है। यदि कोई मिटा हुआ पृष्ठ उपलब्ध नहीं है, तो उस ब्लॉक में किसी पृष्ठ पर डेटा की प्रतिलिपि बनाने से पहले एक ब्लॉक को मिटा दिया जाना चाहिए। पुराने पृष्ठ को तब अमान्य के रूप में चिह्नित किया जाता है और इसे मिटाने और पुन: उपयोग के लिए उपलब्ध है।[69]

ऊर्ध्वाधर NAND

वर्टिकल NAND (वी-NAND) या 3 डी NAND मेमोरी मेमोरी सेल को लंबवत रूप से ढेर कर देता है और एक चार्ज ट्रैप फ्लैश आर्किटेक्चर का उपयोग करता है।ऊर्ध्वाधर परतें छोटी व्यक्तिगत कोशिकाओं की आवश्यकता के बिना बड़े क्षेत्र बिट घनत्व की अनुमति देती हैं।[70] यह ट्रेडमार्क BICS फ्लैश के तहत भी बेचा जाता है, जो किक्सिया कॉर्पोरेशन (पूर्व तोशिबा मेमोरी कॉरपोरेशन) का ट्रेडमार्क है।3 डी NAND को पहली बार 2007 में तोशिबा द्वारा घोषित किया गया था।[71] वी-NAND पहली बार 2013 में सैमसंग इलेक्ट्रॉनिक्स द्वारा व्यावसायिक रूप से निर्मित किया गया था।[42][43][72][73]

संरचना

V-NAND एक चार्ज ट्रैप फ्लैश ज्यामिति का उपयोग करता है (जिसे 2002 में AMD और FUJITSU द्वारा व्यावसायिक रूप से पेश किया गया था)[41]यह स्टोर एक एम्बेडेड सिलिकॉन नाइट्राइड फिल्म पर चार्ज करते हैं।इस तरह की फिल्म बिंदु दोषों के खिलाफ अधिक मजबूत है और बड़ी संख्या में इलेक्ट्रॉनों को रखने के लिए मोटी बनाई जा सकती है।वी-NAND एक प्लानर चार्ज ट्रैप सेल को एक बेलनाकार रूप में लपेटता है।[70]2020 तक, माइक्रोन और इंटेल द्वारा 3 डी NAND फ्लैश यादें फ्लोटिंग गेट्स का उपयोग करती हैं, हालांकि, माइक्रोन 128 लेयर और 3 डी NAND यादें से ऊपर एक पारंपरिक चार्ज ट्रैप संरचना का उपयोग करती हैं, माइक्रोन और इंटेल के बीच साझेदारी के विघटन के कारण।चार्ज ट्रैप 3 डी NAND फ्लैश फ्लोटिंग गेट 3 डी NAND की तुलना में पतला है।फ्लोटिंग गेट 3 डी NAND में, मेमोरी सेल पूरी तरह से एक दूसरे से अलग हो जाते हैं, जबकि चार्ज ट्रैप 3 डी NAND में, मेमोरी सेल के ऊर्ध्वाधर समूह समान सिलिकॉन नाइट्राइड सामग्री साझा करते हैं।[74] एक व्यक्तिगत मेमोरी सेल एक प्लानर पॉलीसिलिकॉन परत से बना होता है, जिसमें कई गाढ़ा ऊर्ध्वाधर सिलेंडर द्वारा भरा हुआ छेद होता है।छेद की पॉलीसिलिकॉन सतह गेट इलेक्ट्रोड के रूप में कार्य करती है।सबसे बाहरी सिलिकॉन डाइऑक्साइड सिलेंडर गेट ढांकता हुआ के रूप में कार्य करता है, एक सिलिकॉन नाइट्राइड सिलेंडर को संलग्न करता है जो स्टोर करता है, एक सिलिकॉन डाइऑक्साइड सिलेंडर को सुरंग के ढांकता हुआ के रूप में संलग्न करता है जो पॉलीसिलिकॉन के संचालन की एक केंद्रीय छड़ को घेरता है जो चालन चैनल के रूप में कार्य करता है।[70]

विभिन्न ऊर्ध्वाधर परतों में मेमोरी कोशिकाएं एक -दूसरे के साथ हस्तक्षेप नहीं करती हैं, क्योंकि चार्ज सिलिकॉन नाइट्राइड स्टोरेज माध्यम के माध्यम से लंबवत रूप से आगे नहीं बढ़ सकते हैं, और गेट्स से जुड़े विद्युत क्षेत्र प्रत्येक परत के भीतर बारीकी से सीमित होते हैं।ऊर्ध्वाधर संग्रह विद्युत रूप से सीरियल-लिंक्ड समूहों के समान है जिसमें पारंपरिक NAND & nbsp; फ्लैश मेमोरी कॉन्फ़िगर किया गया है।[70]

निर्माण

वी-NAND कोशिकाओं के एक समूह की वृद्धि संचालन (डोपेड) पॉलीसिलिकॉन परतों और इंसुलेटिंग सिलिकॉन डाइऑक्साइड परतों के एक वैकल्पिक ढेर के साथ शुरू होती है।[70]

अगला कदम इन परतों के माध्यम से एक बेलनाकार छेद बनाना है।व्यवहार में, मेमोरी कोशिकाओं की 24 परतों के साथ एक 128 & nbsp; गिबिट वी-NAND चिप में लगभग 2.9 बिलियन ऐसे छेद की आवश्यकता होती है।इसके बाद, छेद की आंतरिक सतह को कई कोटिंग्स, पहले सिलिकॉन डाइऑक्साइड, फिर सिलिकॉन नाइट्राइड, फिर सिलिकॉन डाइऑक्साइड की दूसरी परत प्राप्त होती है।अंत में, छेद संचालन (डोपेड) पॉलीसिलिकॉन से भरा है।[70]

प्रदर्शन

As of 2013,[update] वी-NAND फ्लैश आर्किटेक्चर पारंपरिक NAND के रूप में दो बार पढ़ने और लिखने की अनुमति देता है और 50 प्रतिशत कम शक्ति का उपभोग करते हुए, 10 गुना तक लंबे समय तक रह सकता है।वे 10-एनएम लिथोग्राफी का उपयोग करके तुलनीय भौतिक बिट घनत्व प्रदान करते हैं, लेकिन कई सौ परतों तक वी-NAND के उपयोग को देखते हुए, परिमाण के दो आदेशों तक बिट घनत्व बढ़ाने में सक्षम हो सकते हैं।[70]2020 तक, 160 परतों के साथ वी-NAND चिप्स सैमसंग द्वारा विकास के अधीन हैं।[75]

लागत

3 डी NAND की वेफर लागत स्केल्ड डाउन (32 & nbsp; nm या उससे कम) प्लानर NAND फ्लैश के साथ तुलनीय है।[76] हालांकि, प्लानर NAND स्केलिंग के साथ 16 & nbsp; एनएम पर रोक, प्रति बिट कमी की लागत 3 डी NAND द्वारा 16 परतों के साथ शुरू हो सकती है।हालांकि, परतों के माध्यम से छेद किए गए छेद के गैर-वर्टिकल फुटपाथ के कारण;यहां तक कि एक मामूली विचलन एक न्यूनतम बिट लागत, अर्थात्, न्यूनतम समतुल्य डिजाइन नियम (या अधिकतम घनत्व), परतों की एक संख्या के लिए;यह न्यूनतम बिट लागत परत संख्या छोटे छेद व्यास के लिए कम हो जाती है।[77]

सीमाएँ

ब्लॉक ERASURE

फ्लैश मेमोरी की एक सीमा यह है कि, इसे एक समय में केवल एक ब्लॉक मिटा दिया जा सकता है।यह आम तौर पर ब्लॉक में सभी बिट्स को 1 पर सेट करता है। एक हौसले से मिटाए गए ब्लॉक के साथ शुरू होता है, उस ब्लॉक के भीतर किसी भी स्थान को प्रोग्राम किया जा सकता है।हालाँकि, एक बार एक बार 0 पर सेट कर दिया गया है, केवल पूरे ब्लॉक को मिटाकर इसे वापस 1 में बदल दिया जा सकता है। दूसरे शब्दों में, फ्लैश मेमोरी (विशेष रूप से और न ही & nbsp; फ्लैश) यादृच्छिक-एक्सेस रीड और प्रोग्रामिंग संचालन प्रदान करता है, लेकिन मनमानी की पेशकश नहीं करता हैयादृच्छिक-पहुंच फिर से लिखें या संचालन को मिटा दें।हालांकि, एक स्थान को फिर से लिखा जा सकता है जब तक कि नए मूल्य के 0 बिट्स ओवर-लिखित मूल्यों का एक सुपरसेट हैं।उदाहरण के लिए, एक कुतरने का मूल्य 1111 तक मिटा दिया जा सकता है, फिर 1110 के रूप में लिखा जा सकता है। क्रमिक लिखते हैं कि निबेल इसे 1010, फिर 0010, और अंत में 0000 में बदल सकता है। अनिवार्य रूप से, इरेज़्योर सभी बिट्स को 1 पर सेट करता है, और प्रोग्रामिंग केवल बिट्स को स्पष्ट कर सकता है, जो कि बिट्स को स्पष्ट कर सकते हैं0 से।[78] फ्लैश उपकरणों के लिए डिज़ाइन किए गए कुछ फ़ाइल सिस्टम इस पुनर्लेखन क्षमता का उपयोग करते हैं, उदाहरण के लिए YAFFS1, सेक्टर मेटाडेटा का प्रतिनिधित्व करने के लिए। अन्य फ्लैश फ़ाइल सिस्टम, जैसे कि YAFFS2, कभी भी इस पुनर्लेखन क्षमता का उपयोग नहीं करते हैं - वे एक बार एक नियम को पूरा करने के लिए बहुत सारे अतिरिक्त काम करते हैं।

यद्यपि फ्लैश मेमोरी में डेटा संरचनाओं को पूरी तरह से सामान्य तरीकों से अपडेट नहीं किया जा सकता है, लेकिन यह सदस्यों को उन्हें अमान्य के रूप में चिह्नित करके हटा दिया जा सकता है।इस तकनीक को बहु-स्तरीय सेल उपकरणों के लिए संशोधित करने की आवश्यकता हो सकती है, जहां एक मेमोरी सेल एक से अधिक बिट रखती है।

USB & NBSP; फ्लैश ड्राइव और मेमोरी कार्ड जैसे सामान्य फ्लैश डिवाइस केवल एक ब्लॉक-लेवल इंटरफ़ेस, या फ्लैश ट्रांसलेशन लेयर (FTL) प्रदान करते हैं, जो डिवाइस को पहनने के लिए हर बार एक अलग सेल को लिखता है।यह एक ब्लॉक के भीतर वृद्धिशील लेखन को रोकता है;हालांकि, यह डिवाइस को समय से पहले गहन लेखन पैटर्न द्वारा पहने जाने में मदद करता है।

डेटा प्रतिधारण

फ्लैश कोशिकाओं पर संग्रहीत इलेक्ट्रॉन डिट्रेपिंग डेटा के कारण, पूर्ण तापमान में वृद्धि के साथ तेजी से बढ़ते हुए नुकसान की दर के साथ लगातार खो रहा है;45 एनएम और न ही फ्लैश के लिए, 1000 घंटे में, 25 डिग्री सेल्सियस पर दहलीज वोल्टेज (वीटी) का नुकसान लगभग 90 डिग्री सेल्सियस पर है।[79]

मेमोरी वियर

एक और सीमा यह है कि फ्लैश मेमोरी में प्रोग्राम की एक सीमित संख्या है – साइकिल मिटाएं (आमतौर पर P/E & NBSP; चक्र) के रूप में लिखा गया है।अधिकांश व्यावसायिक रूप से उपलब्ध फ्लैश उत्पादों को लगभग 100,000 p/e & nbsp का सामना करने की गारंटी दी जाती है; पहनने से पहले साइकिल भंडारण की अखंडता को बिगड़ने के लिए शुरू होती है।[80] माइक्रोन टेक्नोलॉजी और सन माइक्रोसिस्टम्स ने 17 दिसंबर 2008 को 1,000,000 & nbsp; p/e & nbsp; के लिए रेटेड एक SLC & nbsp; Nand फ्लैश मेमोरी चिप की घोषणा की।[81] औद्योगिक एसएसडी के लंबे समय तक पी/ई चक्र अपने धीरज स्तर के लिए बोलते हैं और उन्हें औद्योगिक उपयोग के लिए अधिक विश्वसनीय बनाते हैं।

गारंटीकृत चक्र गणना केवल शून्य को ब्लॉक करने पर लागू हो सकती है (जैसा कि पतले छोटे-आउटलाइन पैकेज के साथ होता है। tsop & nbsp; nand डिवाइस), या सभी ब्लॉकों (नॉन के रूप में)। इस प्रभाव को कुछ चिप फर्मवेयर या फाइल सिस्टम ड्राइवरों में लिखते हुए और डायनामिक रूप से रीमैपिंग ब्लॉक की गिनती करके कम किया जाता है ताकि सेक्टरों के बीच लिखने के संचालन को फैलाया जा सके; इस तकनीक को वियर लेवलिंग कहा जाता है। एक अन्य दृष्टिकोण लिखने की विफलता के मामले में राइट वेरिफिकेशन और स्पेयर सेक्टरों को रीमैपिंग करना है, जो बैड ब्लॉक मैनेजमेंट (बीबीएम) नामक एक तकनीक है। पोर्टेबल उपभोक्ता उपकरणों के लिए, ये पहनने वाली प्रबंधन तकनीकें आमतौर पर डिवाइस के जीवन से परे फ्लैश मेमोरी के जीवन का विस्तार करती हैं, और इन अनुप्रयोगों में कुछ डेटा हानि स्वीकार्य हो सकती है। उच्च-विश्वसनीयता डेटा स्टोरेज के लिए, हालांकि, फ्लैश मेमोरी का उपयोग करना उचित नहीं है, जिसे बड़ी संख्या में प्रोग्रामिंग चक्रों से गुजरना होगा। यह सीमा पतले ग्राहकों और राउटर जैसे 'रीड-ओनली' अनुप्रयोगों के लिए अर्थहीन है, जो कि उनके जीवनकाल के दौरान केवल एक बार या अधिकांश समय केवल एक बार प्रोग्राम किए जाते हैं।

दिसंबर 2012 में, मैक्रोनिक्स के ताइवान के इंजीनियरों ने 2012 के IEEE इंटरनेशनल इलेक्ट्रॉन डिवाइसेस मीटिंग में घोषणा करने की घोषणा की कि उन्होंने यह पता लगाया था कि NAND & nbsp को कैसे बेहतर बनाया जाए; फ्लैश स्टोरेज पढ़ें/10,000 से 100 मिलियन साइकिल से एक सेल्फ-हीलिंग प्रक्रिया का उपयोग करके साइकिल लिखें। ऑनबोर्ड हीटर के साथ एक फ्लैश चिप का उपयोग किया जो मेमोरी कोशिकाओं के छोटे समूहों की घोषणा कर सकता है।[82] अंतर्निहित थर्मल एनीलिंग एक स्थानीय उच्च तापमान प्रक्रिया के साथ सामान्य मिटने वाले चक्र को बदलने के लिए था, जो न केवल संग्रहीत चार्ज को मिटा देता है, बल्कि चिप में इलेक्ट्रॉन-प्रेरित तनाव की मरम्मत भी करता है, जिससे कम से कम 100 मिलियन के चक्र लिखते हैं।[83] परिणाम एक ऐसी चिप थी जिसे मिटाया जा सकता था और फिर से लिखा जा सकता था, तब भी जब इसे सैद्धांतिक रूप से टूटना चाहिए।मैक्रोनिक्स की सफलता के रूप में आशाजनक मोबाइल उद्योग के लिए हो सकता है, हालांकि, निकट भविष्य में किसी भी समय जारी होने वाली इस क्षमता की विशेषता वाले वाणिज्यिक उत्पाद के लिए कोई योजना नहीं थी।[84]

पढ़ें डिस्टर्ब

NAND & nbsp; फ्लैश मेमोरी पढ़ने के लिए उपयोग की जाने वाली विधि समय के साथ एक ही मेमोरी ब्लॉक में आस -पास की कोशिकाओं का कारण बन सकती है (प्रोग्राम्ड हो जाती है)।इसे रीड डिस्टर्ब के रूप में जाना जाता है।रीड्स की दहलीज संख्या आम तौर पर हस्तक्षेप करने वाले संचालन के बीच सैकड़ों हजारों रीड्स में होती है।यदि एक सेल से लगातार पढ़ते हैं, तो वह सेल विफल नहीं होगा, बल्कि बाद में पढ़ने पर आसपास की कोशिकाओं में से एक है।रीड डिस्टर्ब प्रॉब्लम से बचने के लिए फ्लैश कंट्रोलर आमतौर पर अंतिम मिटने के बाद से एक ब्लॉक में रीड्स की कुल संख्या की गिनती करेगा।जब गिनती एक लक्ष्य सीमा से अधिक हो जाती है, तो प्रभावित ब्लॉक को एक नए ब्लॉक पर कॉपी किया जाता है, मिटा दिया जाता है, फिर ब्लॉक पूल में जारी किया जाता है।मूल ब्लॉक मिटने के बाद उतना ही अच्छा है।यदि फ्लैश कंट्रोलर समय में हस्तक्षेप नहीं करता है, हालांकि, एक रीड डिस्टर्ब एरर संभावित डेटा लॉस के साथ होगा यदि त्रुटियां एक त्रुटि-सुधार कोड के साथ सही करने के लिए बहुत अधिक हैं।[85][86][87]

एक्स-रे प्रभाव

अधिकांश फ्लैश आईसीएस बॉल ग्रिड एरे (बीजीए) पैकेज में आते हैं, और यहां तक कि जो अक्सर अन्य बीजीए पैकेजों के बगल में एक पीसीबी पर नहीं लगे होते हैं।पीसीबी असेंबली के बाद, बीजीए पैकेज के साथ बोर्ड अक्सर एक्स-रे होते हैं यह देखने के लिए कि क्या गेंद उचित पैड से उचित कनेक्शन बना रही हैं, या यदि बीजीए को फिर से काम करने की आवश्यकता है।ये एक्स-रे एक फ्लैश चिप में प्रोग्राम किए गए बिट्स को मिटा सकते हैं (प्रोग्राम किए गए 0 बिट्स को मिटाए गए 1 बिट्स में परिवर्तित करें)।मिटाए गए बिट्स (1 बिट्स) एक्स-रे से प्रभावित नहीं होते हैं।[88][89] कुछ निर्माता अब एक्स-रे प्रूफ एसडी बना रहे हैं[90] और USB[91] मेमोरी डिवाइस।

निम्न-स्तरीय पहुंच

फ्लैश मेमोरी चिप्स के लिए निम्न-स्तरीय इंटरफ़ेस अन्य मेमोरी प्रकारों जैसे कि DRAM, Read-only मेमोरी | ROM, और EEPROM से भिन्न होता है, जो बिट-अल्टरबिलिटी (दोनों शून्य से एक और एक से शून्य) और बाहरी रूप से एक्सेस का समर्थन करते हैं और बाहरी रूप से यादृच्छिक पहुंच का समर्थन करते हैं।सुलभ पता बसें।

न ही मेमोरी में पढ़ने और प्रोग्रामिंग के लिए एक बाहरी पता बस है।NOR मेमोरी के लिए, रीडिंग और प्रोग्रामिंग यादृच्छिक-पहुंच है, और अनलॉकिंग और इरेज़िंग ब्लॉक-वार हैं।NAND मेमोरी के लिए, पढ़ना और प्रोग्रामिंग पेज-वार हैं, और अनलॉकिंग और इरेज़िंग ब्लॉक-वार हैं।

और न ही यादें

NOR फ्लैश से पढ़ना यादृच्छिक-एक्सेस मेमोरी से पढ़ने के समान है, बशर्ते कि पता और डेटा बस को सही ढंग से मैप किया गया हो। इस वजह से, अधिकांश माइक्रोप्रोसेसर्स न तो उपयोग कर सकते हैं और न ही & nbsp; फ़्लैश मेमोरी के रूप में जगह (XIP) मेमोरी में निष्पादित कर सकते हैं, जिसका अर्थ है कि NOR & nbsp में संग्रहीत प्रोग्राम; फ्लैश को सीधे NOR & nbsp से निष्पादित किया जा सकता है; फ्लैश को पहले राम में कॉपी किए जाने की आवश्यकता के बिना। न ही & nbsp; फ्लैश को पढ़ने के समान यादृच्छिक-पहुंच तरीके से प्रोग्राम किया जा सकता है। प्रोग्रामिंग एक तार्किक से एक शून्य में बिट्स को बदलता है। बिट्स जो पहले से ही शून्य हैं, वे अपरिवर्तित हैं। ERASURE एक समय में एक ब्लॉक होना चाहिए, और मिटाए गए ब्लॉक में सभी बिट्स को वापस एक पर रीसेट करता है। विशिष्ट ब्लॉक आकार 64, 128, या 256 & nbsp; kib हैं।

खराब ब्लॉक प्रबंधन NOR & nbsp; चिप्स में एक अपेक्षाकृत नई सुविधा है। पुराने और न ही डिवाइस में खराब ब्लॉक प्रबंधन का समर्थन नहीं है, मेमोरी चिप को नियंत्रित करने वाले सॉफ़्टवेयर या डिवाइस ड्राइवर को ब्लॉकों के लिए सही होना चाहिए जो पहनते हैं, या डिवाइस मज़बूती से काम करना बंद कर देगा।

विशिष्ट कमांड लॉक, अनलॉक, प्रोग्राम या मिटाने के लिए उपयोग किए जाते हैं और न ही यादें प्रत्येक निर्माता के लिए भिन्न होती हैं। किए गए प्रत्येक डिवाइस के लिए अद्वितीय ड्राइवर सॉफ़्टवेयर की आवश्यकता से बचने के लिए, विशेष सामान्य फ्लैश मेमोरी इंटरफ़ेस (CFI) कमांड डिवाइस को खुद और इसके महत्वपूर्ण परिचालन मापदंडों की पहचान करने की अनुमति देते हैं।

यादृच्छिक-पहुंच वाले रोम के रूप में इसके उपयोग के अलावा, न ही & nbsp; फ्लैश का उपयोग यादृच्छिक-एक्सेस प्रोग्रामिंग का लाभ उठाकर, स्टोरेज डिवाइस के रूप में भी किया जा सकता है। कुछ डिवाइस रीड-व्हाइल-राइट कार्यक्षमता की पेशकश करते हैं ताकि पृष्ठभूमि में एक प्रोग्राम या इरेज़ ऑपरेशन होने पर भी कोड निष्पादित हो जाए। अनुक्रमिक डेटा लिखते हैं, न ही & nbsp; फ्लैश चिप्स में आमतौर पर NAND & nbsp; फ्लैश की तुलना में धीमी गति से लिखने की गति होती है।

विशिष्ट और न ही फ्लैश को एक त्रुटि सही कोड की आवश्यकता नहीं है।[92]

NAND यादें

1989 में तोशिबा द्वारा NAND फ्लैश आर्किटेक्चर पेश किया गया था।[93] इन यादों को ब्लॉक डिवाइस, जैसे हार्ड डिस्क की तरह बहुत एक्सेस किया जाता है।प्रत्येक ब्लॉक में कई पृष्ठ होते हैं।पृष्ठ आमतौर पर 512 हैं,[94] 2,048 या 4,096 बाइट्स आकार में।प्रत्येक पृष्ठ के साथ संबद्ध कुछ बाइट्स (आमतौर पर डेटा आकार के 1/32) हैं जिनका उपयोग एक त्रुटि सही कोड (ईसीसी) चेकसम के भंडारण के लिए किया जा सकता है।

विशिष्ट ब्लॉक आकार में शामिल हैं:

- 16 & nbsp; KIB के ब्लॉक आकार (प्रभावी) के लिए प्रत्येक 512+16 बाइट्स के 32 पृष्ठ

- 128 & nbsp के ब्लॉक आकार के लिए प्रत्येक 2,048+64 बाइट्स के 64 पृष्ठ; Ref> TN-29-07: छोटे-ब्लॉक बनाम बड़े-ब्लॉक NAND फ्लैश डिवाइस] Archived 8 June 2013 at the Wayback Machine 512+16 और 2048+64-बाइट ब्लॉक </ref> बताते हैं

- 256 & nbsp के ब्लॉक आकार के लिए प्रत्येक 4,096+128 बाइट्स के 64 पृष्ठ;

Ref> AN10860 LPC313X NAND फ्लैश डेटा और खराब ब्लॉक प्रबंधन Archived 3 March 2016 at the Wayback Machine 4096+128-बाइट ब्लॉक बताते हैं। </ref>

- 512 & nbsp; kib के ब्लॉक आकार के लिए प्रत्येक 4,096+128 बाइट्स के 128 पृष्ठ।

जबकि पढ़ना और प्रोग्रामिंग एक पृष्ठ के आधार पर किया जाता है, Erasure केवल एक ब्लॉक आधार पर किया जा सकता है। रेफ नाम = एल स्मिथ>Thatcher, Jonathan (18 August 2009). "NAND Flash Solid State Storage Performance and Capability – an In-depth Look" (PDF). SNIA. Archived (PDF) from the original on 7 September 2012. Retrieved 2012-08-28.</ref>

NAND डिवाइस को डिवाइस ड्राइवर सॉफ़्टवेयर या एक अलग कंट्रोलर चिप द्वारा खराब ब्लॉक प्रबंधन की भी आवश्यकता होती है।उदाहरण के लिए, SD & NBSP; कार्ड, खराब ब्लॉक प्रबंधन और पहनने के स्तर को करने के लिए नियंत्रक सर्किटरी को शामिल करें।जब एक तार्किक ब्लॉक को उच्च-स्तरीय सॉफ़्टवेयर द्वारा एक्सेस किया जाता है, तो इसे डिवाइस ड्राइवर या कंट्रोलर द्वारा एक भौतिक ब्लॉक में मैप किया जाता है।फ्लैश चिप पर कई ब्लॉक को खराब ब्लॉकों से निपटने के लिए मैपिंग टेबल के भंडारण के लिए अलग सेट किया जा सकता है, या सिस्टम केवल रैम में एक खराब ब्लॉक मैप बनाने के लिए पावर-अप पर प्रत्येक ब्लॉक की जांच कर सकता है।समग्र मेमोरी क्षमता धीरे -धीरे सिकुड़ जाती है क्योंकि अधिक ब्लॉक खराब हैं।

NAND BITS की भरपाई करने के लिए ECC पर निर्भर करता है जो सामान्य डिवाइस ऑपरेशन के दौरान अनायास विफल हो सकता है।एक विशिष्ट ईसीसी प्रत्येक 2048 & nbsp; बिट्स (256 & nbsp; बाइट्स) में 22 & nbsp; बिट्स के बिट्स, या प्रत्येक 4096 & nbsp; बिट्स (512 & nbsp; बाइट्स) में 24 & nbsp; बिट्स का उपयोग करते हुए एक-बिट त्रुटि का उपयोग करके एक-बिट त्रुटि को सही करेगा।[95] यदि ईसीसी रीड के दौरान त्रुटि को ठीक नहीं कर सकता है, तो यह अभी भी त्रुटि का पता लगा सकता है।जब मिटते हैं या कार्यक्रम संचालन करते हैं, तो डिवाइस ब्लॉकों का पता लगा सकता है जो प्रोग्राम या मिटाने में विफल होते हैं और उन्हें खराब करते हैं।डेटा तब एक अलग, अच्छे ब्लॉक में लिखा जाता है, और खराब ब्लॉक मैप को अपडेट किया जाता है।

हैमिंग कोड SLC & nbsp; Nand फ्लैश के लिए सबसे अधिक इस्तेमाल किया जाने वाला ECC है।रीड-सोलोमन त्रुटि सुधार | रीड-सोलोमन कोड और बीसीएच कोड (बोस-चौधुरी-होकक्वेनघम कोड) आमतौर पर एमएलसी और एनबीएसपी के लिए ईसीसी का उपयोग किया जाता है; NAND फ्लैश।कुछ MLC & nbsp; Nand फ्लैश चिप्स आंतरिक रूप से उपयुक्त BCH & nbsp; त्रुटि सुधार कोड उत्पन्न करते हैं।[92]

अधिकांश NAND उपकरणों को कारखाने से कुछ खराब ब्लॉकों के साथ भेज दिया जाता है। इन्हें आमतौर पर एक निर्दिष्ट खराब ब्लॉक मार्किंग रणनीति के अनुसार चिह्नित किया जाता है। कुछ खराब ब्लॉकों की अनुमति देकर, निर्माताओं को प्राप्त करने की तुलना में कहीं अधिक पैदावार प्राप्त करना संभव होगा यदि सभी ब्लॉकों को अच्छा होने के लिए सत्यापित किया जाना था। यह NAND & nbsp; फ्लैश लागत को काफी कम कर देता है और केवल भागों की भंडारण क्षमता को थोड़ा कम करता है।

NAND यादों से सॉफ़्टवेयर को निष्पादित करते समय, वर्चुअल मेमोरी रणनीतियों का अक्सर उपयोग किया जाता है: मेमोरी सामग्री को पहले मेमोरी-मैप किए गए रैम में पेज या कॉपी किया जाना चाहिए और वहां निष्पादित किया जाना चाहिए (NAND + RAM के सामान्य संयोजन के लिए)। सिस्टम में एक मेमोरी मैनेजमेंट यूनिट (MMU) सहायक है, लेकिन इसे ओवरले के साथ भी पूरा किया जा सकता है। इस कारण से, कुछ सिस्टम NOR और NAND यादों के संयोजन का उपयोग करेंगे, जहां एक छोटी और मेमोरी का उपयोग सॉफ्टवेयर ROM के रूप में किया जाता है और एक बड़ी NAND मेमोरी को एक गैर-वाष्पशील डेटा स्टोरेज क्षेत्र के रूप में उपयोग के लिए एक फ़ाइल सिस्टम के साथ विभाजित किया जाता है।

NAND यादृच्छिक-पहुंच और NOR के निष्पादित लाभ के लाभ का त्याग करता है। NAND उच्च क्षमता वाले डेटा स्टोरेज की आवश्यकता वाले सिस्टम के लिए सबसे उपयुक्त है। यह उच्च घनत्व, बड़ी क्षमता और कम लागत प्रदान करता है। इसमें तेजी से मिटने वाले, अनुक्रमिक लिखते हैं, और अनुक्रमिक रीड्स हैं।

मानकीकरण

ओपन NAND फ्लैश इंटरफ़ेस वर्किंग ग्रुप (ONFI) नामक एक समूह ने NAND & NBSP; फ्लैश चिप्स के लिए एक मानकीकृत निम्न-स्तरीय इंटरफ़ेस विकसित किया है।यह विभिन्न विक्रेताओं से NAND उपकरणों के अनुरूप अंतर की अनुमति देता है।ONFI विनिर्देश संस्करण 1.0[96] 28 दिसंबर 2006 को जारी किया गया था। यह निर्दिष्ट करता है:

- पतले छोटे-आउटलाइन पैकेज में NAND फ्लैश के लिए एक मानक भौतिक इंटरफ़ेस (पिनआउट) | TSOP-48, WSOP-48, LGA-52, और BGA-63 पैकेज

- NAND फ्लैश चिप्स को पढ़ने, लिखने और मिटाने के लिए एक मानक कमांड सेट

- स्व-पहचान के लिए एक तंत्र (SDRAM मेमोरी मॉड्यूल की सीरियल उपस्थिति का पता लगाने की सुविधा के लिए)

ONFI समूह को प्रमुख NAND फ्लैश निर्माताओं द्वारा समर्थित किया जाता है, जिसमें Hynix, Intel, Micron Technology, और Numonyx शामिल हैं, साथ ही NAND & NBSP; फ्लैश चिप्स को शामिल करने वाले उपकरणों के प्रमुख निर्माताओं द्वारा भी।[97] दो प्रमुख फ्लैश डिवाइस निर्माता, तोशिबा और सैमसंग ने अपने स्वयं के डिजाइन के एक इंटरफ़ेस का उपयोग करने के लिए चुना है जिसे टॉगल मोड (और अब टॉगल v2.0) के रूप में जाना जाता है।यह इंटरफ़ेस पिन संगतता नहीं है#पिन-टू-पिन संगतता | ONFI विनिर्देश के साथ पिन-टू-पिन संगत नहीं है।नतीजा यह है कि एक विक्रेता के उपकरणों के लिए डिज़ाइन किया गया उत्पाद दूसरे विक्रेता के उपकरणों का उपयोग करने में सक्षम नहीं हो सकता है।[98] इंटेल, डेल और माइक्रोसॉफ्ट सहित विक्रेताओं के एक समूह ने एक गैर-वाष्पशील मेमोरी होस्ट कंट्रोलर इंटरफ़ेस (NVMHCI) वर्किंग ग्रुप का गठन किया।[99] समूह का लक्ष्य पीसीआई एक्सप्रेस बस से जुड़े फ्लैश कैश डिवाइस सहित, गैर -मेमोरी मेमोरी सबसिस्टम के लिए मानक सॉफ्टवेयर और हार्डवेयर प्रोग्रामिंग इंटरफेस प्रदान करना है।

== NOR और NAND फ्लैश == के बीच का अंतर न ही और NAND फ्लैश दो महत्वपूर्ण तरीकों से भिन्न हैं:

- व्यक्तिगत मेमोरी कोशिकाओं के कनेक्शन अलग -अलग हैं।[citation needed]

- मेमोरी को पढ़ने और लिखने के लिए प्रदान किया गया इंटरफ़ेस अलग है;न ही यादृच्छिक पहुंच की अनुमति देता है, जबकि NAND केवल पेज एक्सेस की अनुमति देता है।[100]

न ही और NAND फ्लैश मेमोरी कोशिकाओं के बीच अंतर्संबंधों की संरचना से उनके नाम प्राप्त करते हैं।[citation needed] NOR & nbsp; फ्लैश में, कोशिकाएं बिट लाइनों के समानांतर जुड़ी हुई हैं, जिससे कोशिकाओं को व्यक्तिगत रूप से पढ़ने और प्रोग्राम करने की अनुमति मिलती है।कोशिकाओं के समानांतर कनेक्शन एक CMOS NOR गेट में ट्रांजिस्टर के समानांतर कनेक्शन से मिलता जुलता है।NAND & nbsp; फ्लैश में, कोशिकाएं श्रृंखला में जुड़ी हुई हैं, एक CMOS NAND गेट से मिलती जुलती हैं।श्रृंखला कनेक्शन समानांतर लोगों की तुलना में कम स्थान का उपभोग करते हैं, NAND & nbsp; फ्लैश की लागत को कम करते हैं।यह अपने आप में, NAND कोशिकाओं को व्यक्तिगत रूप से पढ़ने और प्रोग्राम किए जाने से नहीं रोकता है।[citation needed] प्रत्येक और न ही फ्लैश सेल एक NAND & nbsp; फ्लैश सेल से बड़ा है – 10 & nbsp; f2 बनाम 4 & nbsp; f2 – यहां तक कि एक ही अर्धचालक डिवाइस निर्माण का उपयोग करते समय और इसलिए प्रत्येक ट्रांजिस्टर, संपर्क, आदि बिल्कुल एक ही आकार है – क्योंकि न ही & nbsp; फ्लैश कोशिकाओं को प्रत्येक सेल के लिए एक अलग धातु संपर्क की आवश्यकता होती है।[101] श्रृंखला कनेक्शन और वर्ल्डलाइन संपर्क को हटाने के कारण, NAND & NBSP का एक बड़ा ग्रिड; फ्लैश मेमोरी सेल शायद समतुल्य और न ही कोशिकाओं के क्षेत्र का केवल 60% पर कब्जा कर लेगा।[102] (एक ही CMOS प्रक्रिया संकल्प को मानते हुए, उदाहरण के लिए, 130 & nbsp; nm, 90 & nbsp; nm, या 65 & nbsp; nm)।NAND & NBSP; फ्लैश के डिजाइनरों ने महसूस किया कि एक NAND चिप का क्षेत्र, और इस प्रकार लागत, बाहरी पते और डेटा बस सर्किटरी को हटाकर और कम किया जा सकता है।इसके बजाय, बाहरी उपकरण NAND & NBSP के साथ संवाद कर सकते हैं; अनुक्रमिक-दुर्घटनाग्रस्त कमांड और डेटा रजिस्टर के माध्यम से फ्लैश, जो आंतरिक रूप से आवश्यक डेटा को पुनः प्राप्त और आउटपुट करेगा।इस डिजाइन विकल्प ने NAND & nbsp की यादृच्छिक-पहुंच बनाई; फ्लैश मेमोरी असंभव, लेकिन NAND & nbsp का लक्ष्य; फ्लैश यांत्रिक हार्ड डिस्क को बदलने के लिए था, रोम को बदलने के लिए नहीं।

| Attribute | NAND | NOR |

|---|---|---|

| Main application | File storage | Code execution |

| Storage capacity | High | Low |

| Cost per bit | Low | |

| Active power | Low | |

| Standby power | Low | |

| Write speed | Fast | |

| Read speed | Fast | |

| Execute in place (XIP) | No | Yes |

| Reliability | High |

धीरज लिखें

SLC फ़्लोटिंग-गेट और न ही फ्लैश का लेखन धीरज आम तौर पर NAND & nbsp; फ्लैश की तुलना में अधिक या उससे अधिक होता है, जबकि MLC & nbsp; न ही और Nand & nbsp; फ्लैश में समान धीरज क्षमताएं हैं।NAND और NOR & NBSP; फ्लैश के साथ -साथ फ़्लैश मेमोरी का उपयोग करके स्टोरेज डिवाइसों में Datasheets में सूचीबद्ध धीरज चक्र रेटिंग के उदाहरण प्रदान किए जाते हैं।[103]

| Type of flash memory | Endurance rating (erases per block) | Example(s) of flash memory or storage device |

|---|---|---|

| SLC NAND | 100,000 | Samsung OneNAND KFW4G16Q2M, Toshiba SLC NAND Flash chips,[104][105][106][107][108] Transcend SD500, Fujitsu S26361-F3298 |

| MLC NAND | 5,000 to 10,000 for medium-capacity applications; 1,000 to 3,000 for high-capacity applications[109] |

Samsung K9G8G08U0M (Example for medium-capacity applications), Memblaze PBlaze4,[110] ADATA SU900, Mushkin Reactor |

| TLC NAND | 1,000 | Samsung SSD 840 |

| QLC NAND | ? | SanDisk X4 NAND flash SD cards[111][112][113][114] |

| 3D SLC NAND | 100,000 | Samsung Z-NAND[115] |

| 3D MLC NAND | 6,000 to 40,000 | Samsung SSD 850 PRO, Samsung SSD 845DC PRO,[116][117] Samsung 860 PRO |

| 3D TLC NAND | 1,000 to 3,000 | Samsung SSD 850 EVO, Samsung SSD 845DC EVO, Crucial MX300[118][119][120],Memblaze PBlaze5 900, Memblaze PBlaze5 700, Memblaze PBlaze5 910/916,Memblaze PBlaze5 510/516,[121][122][123][124] ADATA SX 8200 PRO (also being sold under "XPG Gammix" branding, model S11 PRO) |

| 3D QLC NAND | 100 to 1,000 | Samsung SSD 860 QVO SATA, Intel SSD 660p, Samsung SSD 980 QVO NVMe, Micron 5210 ION, Samsung SSD BM991 NVMe[125][126][127][128][129][130][131][132] |

| 3D PLC NAND | Unknown | In development by SK Hynix (formerly Intel)[133] and Kioxia (formerly Toshiba Memory).[109] |

| SLC (floating-gate) NOR | 100,000 to 1,000,000 | Numonyx M58BW (Endurance rating of 100,000 erases per block); Spansion S29CD016J (Endurance rating of 1,000,000 erases per block) |

| MLC (floating-gate) NOR | 100,000 | Numonyx J3 flash |

हालांकि, कुछ एल्गोरिदम और डिज़ाइन प्रतिमानों को लागू करने से जैसे कि वियर लेवलिंग और फ्लैश ओवर-प्रिसिजनिंग | मेमोरी ओवर-प्रिसिजनिंग, स्टोरेज सिस्टम के धीरज को विशिष्ट आवश्यकताओं की सेवा के लिए ट्यून किया जा सकता है।[134] NAND & nbsp; फ्लैश की दीर्घायु की गणना करने के लिए, किसी को मेमोरी चिप के आकार, मेमोरी के प्रकार (जैसे SLC/MLC/TLC) के लिए जिम्मेदार होना चाहिए, और पैटर्न का उपयोग करना चाहिए।औद्योगिक NAND उनकी क्षमता, लंबे समय तक धीरज और संवेदनशील वातावरण में विश्वसनीयता के कारण मांग में हैं।

3 डी NAND प्रदर्शन परतों को जोड़ने के रूप में नीचा हो सकता है।[115]

फ्लैश फ़ाइल तंत्र (Flash File System)

फ्लैश मेमोरी की व्यक्तिगत विशेषताओं के कारण, या तो इसका सबसे अच्छा उपयोग घिसाव स्तर और त्रुटि सुधार के लिए नियंत्रक के साथ या विशेष रूप से बनाए गए फ्लैश फाइल तंत्र के साथ किया जाता है, जो मीडिया पर लिखता है, और NOR फ्लैश ब्लॉक के लंबे समय तक डेटा को मिटाने के समय का वर्णन करता है। फ्लैश फ़ाइल तंत्र के पीछे मूल अवधारणा यह है कि जब फ्लैश स्टोर को अपडेट करना होता है, तो फाइल तंत्र बदले हुए डेटा की नई प्रति एक नए ब्लॉक में लिखता है, फाइल बिन्दुओं को पुनः अंकित करता है, फिर उसके बाद समय होने पर पुराने ब्लॉक को मिटा देता है।

फ्लैश फाइल तंत्र का उपयोग व्यावहारिक रूप में केवल मेमोरी तकनीक युक्ति (MDT) के लिए किया जाता है, जो ऐसे अन्तर्निहित फ्लैश मेमोरी होते हैं, जिनमें नियंत्रक नहीं होता है। हटाने योग्य फ्लैश मेमोरी कार्ड (removable memory cards), एसएसडी (SSD), ईएमएमसी/ईयूएफएस (eMMC/eUFS) चिपों और यूएसबी फ्लैश ड्राइव (USB flash drive) में घिसाव स्तर और त्रुटि सुधार के लिए पहले से ही नियंत्रक लगे होते हैं, इसलिए इनमें एक विशिष्ट फ्लैश फाइल तंत्र का उपयोग नया लाभ नहीं प्रदान कर सकता है।

क्षमता

कई चिप्स अक्सर उच्च क्षमता प्राप्त करने के लिए खड़ी या मर जाती हैं[135] मल्टीमीडिया खिलाड़ियों या जीपीएस जैसे उपभोक्ता इलेक्ट्रॉनिक उपकरणों में उपयोग के लिए।फ्लैश चिप्स की क्षमता स्केलिंग (वृद्धि) का उपयोग मूर के कानून का पालन करने के लिए किया जाता है क्योंकि वे एक ही एकीकृत सर्किट तकनीकों और उपकरणों में से कई के साथ निर्मित होते हैं।3 डी NAND की शुरूआत के बाद से, स्केलिंग अब आवश्यक रूप से मूर के कानून से जुड़ा नहीं है क्योंकि कभी भी छोटे ट्रांजिस्टर (कोशिकाओं) का उपयोग नहीं किया जाता है।

उपभोक्ता फ़्लैश स्टोरेज डिवाइस आमतौर पर दो (2, 4, 8, आदि) की एक छोटी पूर्णांक शक्ति के रूप में व्यक्त किए गए उपयोग करने योग्य आकारों के साथ विज्ञापित किए जाते हैं और मेगाबाइट्स (एमबी) या गीगाबाइट्स (जीबी) का एक पदनाम;जैसे, 512 & nbsp; mb, 8 & nbsp; gb।इसमें सॉलिड-स्टेट ड्राइव शामिल है। पारंपरिक हार्ड ड्राइव के अनुसार हार्ड ड्राइव रिप्लेसमेंट के रूप में विपणन किया गया एसएसडी, जो दशमलव उपसर्गों का उपयोग करता है।[136] इस प्रकार, एक SSD को 64 & nbsp; GB के रूप में चिह्नित किया गया है 64 × 10003 बाइट्स (64 & nbsp; gb)।फाइल सिस्टम मेटाडेटा द्वारा लिए गए स्थान के कारण अधिकांश उपयोगकर्ताओं को अपनी फ़ाइलों के लिए उपलब्ध इससे थोड़ी कम क्षमता होगी।

उनके अंदर फ्लैश मेमोरी चिप्स सख्त बाइनरी गुणकों में आकार के हैं, लेकिन चिप्स की वास्तविक कुल क्षमता ड्राइव इंटरफ़ेस में उपयोग करने योग्य नहीं है। यह विज्ञापित क्षमता से काफी बड़ा है ताकि राइट्स (वियर लेवलिंग) के वितरण की अनुमति दी जा सके, बख्शने के लिए, त्रुटि सुधार कोड के लिए, और डिवाइस के आंतरिक फर्मवेयर द्वारा आवश्यक अन्य मेटाडेटा के लिए।

2005 में, तोशिबा और सैंडिस्क ने एक NAND & nbsp; फ्लैश चिप विकसित की, जो कि मल्टी-लेवल सेल (MLC) तकनीक का उपयोग करके 1 & nbsp; GB डेटा का संग्रह करने में सक्षम है, जो प्रति सेल डेटा के दो बिट्स को संग्रहीत करने में सक्षम है।सितंबर 2005 में, सैमसंग इलेक्ट्रॉनिक्स ने घोषणा की कि उसने दुनिया का पहला 2 & nbsp; GB चिप विकसित किया है।[137] मार्च 2006 में, सैमसंग ने 4 & nbsp; GB की क्षमता के साथ फ्लैश हार्ड ड्राइव की घोषणा की, अनिवार्य रूप से छोटे लैपटॉप हार्ड ड्राइव के रूप में परिमाण का एक ही क्रम, और सितंबर 2006 में, सैमसंग ने 8 & nbsp; GB चिप की घोषणा की।[138] जनवरी 2008 में, सैंडिस्क ने अपने 16 & nbsp; GB MicroSDHC और 32 & nbsp; GB SDHC प्लस कार्ड की उपलब्धता की घोषणा की।[139][140] अधिक हालिया फ्लैश ड्राइव (2012 तक) में बहुत अधिक क्षमता है, 64, 128, और 256 & nbsp; GB को पकड़े हुए।[141] इंटेल और माइक्रोन में एक संयुक्त विकास 32-लेयर 3.5 टेराबाइट (टीबी (टीबी) के उत्पादन की अनुमति देगा[clarification needed]) NAND & nbsp; फ्लैश स्टिक और 10 & nbsp; टीबी मानक-आकार SSDs।डिवाइस में 16 × 48 & nbsp के 5 पैकेज शामिल हैं; GB & nbsp; TLC मर जाता है, एक फ्लोटिंग गेट सेल डिज़ाइन का उपयोग करके।[142] फ्लैश चिप्स को 1 & nbsp; एमबी (जैसे बायोस-रोम और एम्बेडेड अनुप्रयोगों के लिए) के तहत क्षमताओं के साथ निर्मित किया जाता है।

जुलाई 2016 में, सैमसंग ने 4 टीबी की घोषणा की[clarification needed] सैमसंग 850 ईवो जो उनके 256 & nbsp; gbit 48-लेयर TLC 3D V-NAND का उपयोग करता है।[143] अगस्त 2016 में, सैमसंग ने एक 32 & nbsp की घोषणा की; TB 2.5-इंच SAS & nbsp; SSD उनके 512 & nbsp; Gbit 64-लेयर TLC 3D & nbsp; v-nand पर आधारित है।इसके अलावा, सैमसंग ने 2020 तक 100 & nbsp तक SSDs का अनावरण करने की उम्मीद की है।[144]

स्थानांतरण दरें

फ्लैश मेमोरी युक्ति सामान्यतः लिखने की तुलना में पढ़ने में बहुत तेज होती हैं।[145] इनका प्रदर्शन भंडारण नियंत्रकों की गुणवत्ता पर भी निर्भर करता है, जो आंशिक रूप से भरे होने पर अधिक महत्वपूर्ण हो जाते हैं।[vague][145] यहाँ तक कि जब विनिर्माण में डाइ का सिकुड़ना एकमात्र परिवर्तन होता है, तो एक उपयुक्त नियंत्रक की अनुपस्थिति के परिणामस्वरूप गति में गिरावट हो सकती है।[146]

अनुप्रयोग

सीरियल फ्लैश

सीरियल फ्लैश एक छोटा, कम -शक्ति वाला फ्लैश मेमोरी है जो डेटा के लिए केवल सीरियल एक्सेस प्रदान करता है - व्यक्तिगत बाइट्स को संबोधित करने के बजाय, उपयोगकर्ता पते की जगह में बाइट्स के बड़े सन्निहित समूहों को पढ़ता है या लिखता है। सीरियल पेरिफेरल इंटरफ़ेस बस (SPI) डिवाइस तक पहुंचने के लिए एक विशिष्ट प्रोटोकॉल है। जब एक एम्बेडेड सिस्टम में शामिल किया जाता है, तो सीरियल फ्लैश को समानांतर फ्लैश यादों की तुलना में पीसीबी पर कम तारों की आवश्यकता होती है, क्योंकि यह एक समय में एक बिट डेटा प्रसारित और प्राप्त करता है। यह बोर्ड स्पेस, बिजली की खपत और कुल सिस्टम लागत में कमी की अनुमति दे सकता है।

कई कारण हैं कि एक सीरियल डिवाइस, एक समानांतर डिवाइस की तुलना में कम बाहरी पिन के साथ, समग्र लागत को काफी कम कर सकता है:

- कई अनुप्रयोग-विशिष्ट एकीकृत सर्किट | ASICS पैड-सीमित हैं, जिसका अर्थ है कि डाई का आकार वायर बॉन्ड पैड की संख्या से विवश है, बजाय डिवाइस लॉजिक के लिए उपयोग किए जाने वाले गेटों की जटिलता और संख्या के बजाय। इस प्रकार बॉन्ड पैड को खत्म करना एक छोटे से मरने पर एक अधिक कॉम्पैक्ट एकीकृत सर्किट की अनुमति देता है; यह मरने की संख्या को बढ़ाता है जो एक वेफर पर गढ़ा जा सकता है, और इस तरह प्रति लागत को कम करता है।

- बाहरी पिन की संख्या को कम करने से विधानसभा और पैकेजिंग लागत भी कम हो जाती है। एक सीरियल डिवाइस को समानांतर डिवाइस की तुलना में छोटे और सरल पैकेज में पैक किया जा सकता है।

- छोटे और निचले पिन-काउंट पैकेज कम पीसीबी क्षेत्र पर कब्जा करते हैं।

- लोअर पिन-काउंट डिवाइस पीसीबी रूटिंग को सरल बनाते हैं।

दो प्रमुख एसपीआई फ्लैश प्रकार हैं। पहले प्रकार को छोटे पृष्ठों और एक या एक से अधिक आंतरिक SRAM पेज बफ़र्स की विशेषता है, जो एक पूर्ण पृष्ठ को बफर को पढ़ने की अनुमति देता है, आंशिक रूप से संशोधित किया गया है, और फिर वापस लिखा गया है (उदाहरण के लिए, ATMEL AT45 DataFlash या माइक्रोन टेक्नोलॉजी पेज मिटाएं और न ही NBSP; चमक)। दूसरे प्रकार के बड़े क्षेत्र हैं जहां सबसे छोटे क्षेत्र आमतौर पर इस प्रकार के एसपीआई फ्लैश में पाए जाते हैं, 4 & nbsp; kb, लेकिन वे 64 & nbsp; kb के रूप में बड़े हो सकते हैं। चूंकि इस प्रकार के SPI फ्लैश में एक आंतरिक SRAM बफर का अभाव है, इसलिए पूर्ण पृष्ठ को वापस लिखने से पहले पढ़ा और संशोधित किया जाना चाहिए, जिससे इसे प्रबंधित करने के लिए धीमा हो जाता है। हालांकि, दूसरा प्रकार पहले की तुलना में सस्ता है और इसलिए एप्लिकेशन कोड शैडोइंग होने पर एक अच्छा विकल्प है।

दो प्रकार आसानी से विनिमेय नहीं हैं, क्योंकि उनके पास एक ही पिनआउट नहीं है, और कमांड सेट असंगत हैं।

अधिकांश FPGAs SRAM कॉन्फ़िगरेशन कोशिकाओं पर आधारित होते हैं और एक बाहरी कॉन्फ़िगरेशन डिवाइस की आवश्यकता होती है, जो अक्सर एक सीरियल फ्लैश चिप, कॉन्फ़िगरेशन बिटस्ट्रीम को हर पावर चक्र को फिर से लोड करने के लिए होती है।[147]

फर्मवेयर स्टोरेज

आधुनिक सीपीयू की बढ़ती गति के साथ, समानांतर फ्लैश डिवाइस अक्सर उस कंप्यूटर की मेमोरी बस की तुलना में बहुत धीमे होते हैं जिससे वे जुड़े होते हैं।इसके विपरीत, आधुनिक SRAM 10 & nbsp; ns से नीचे का समय प्रदान करता है, जबकि DDR2 SDRAM 20 & nbsp; ns से नीचे का समय प्रदान करता है।इस वजह से, यह अक्सर रैम में फ़्लैश में संग्रहीत छाया कोड के लिए वांछनीय होता है;यही है, कोड को निष्पादन से पहले फ्लैश से रैम में कॉपी किया जाता है, ताकि सीपीयू इसे पूरी गति से एक्सेस कर सके।डिवाइस फर्मवेयर को सीरियल फ्लैश चिप में संग्रहीत किया जा सकता है, और फिर डिवाइस को संचालित होने पर SDRAM या SRAM में कॉपी किया जा सकता है।[148] ऑन-चिप फ्लैश के बजाय एक बाहरी सीरियल फ्लैश डिवाइस का उपयोग करना महत्वपूर्ण प्रक्रिया समझौता की आवश्यकता को हटा देता है (एक विनिर्माण प्रक्रिया जो उच्च गति के तर्क के लिए अच्छी है, आमतौर पर फ्लैश और इसके विपरीत के लिए अच्छा नहीं है)।एक बार जब एक बड़े ब्लॉक के रूप में फर्मवेयर को पढ़ने का निर्णय लिया जाता है, तो एक छोटे फ्लैश चिप को उपयोग करने के लिए संपीड़न को जोड़ना आम है।सीरियल फ्लैश के लिए विशिष्ट अनुप्रयोगों में हार्ड ड्राइव, ईथरनेट नेटवर्क इंटरफ़ेस एडेप्टर, डीएसएल मोडेम, आदि के लिए फर्मवेयर स्टोर करना शामिल है।

फ्लैश मेमोरी हार्ड ड्राइव के लिए एक प्रतिस्थापन के रूप में

फ्लैश मेमोरी के लिए एक और हालिया एप्लिकेशन हार्ड डिस्क के लिए एक प्रतिस्थापन के रूप में है।फ्लैश मेमोरी में हार्ड ड्राइव की यांत्रिक सीमाएं और विलंबता नहीं होती है, इसलिए गति, शोर, बिजली की खपत और विश्वसनीयता पर विचार करते समय एक ठोस-राज्य ड्राइव (एसएसडी) आकर्षक है।फ्लैश ड्राइव मोबाइल डिवाइस माध्यमिक भंडारण उपकरणों के रूप में कर्षण प्राप्त कर रहे हैं;वे उच्च प्रदर्शन वाले डेस्कटॉप कंप्यूटरों में हार्ड ड्राइव के विकल्प के रूप में भी उपयोग किए जाते हैं और RAID और SAN आर्किटेक्चर के साथ कुछ सर्वर।

फ्लैश-आधारित एसएसडी के कुछ पहलू बने हुए हैं जो उन्हें बदसूरत बनाते हैं।फ्लैश मेमोरी के प्रति गीगाबाइट की लागत हार्ड डिस्क की तुलना में काफी अधिक है।[149] इसके अलावा फ्लैश मेमोरी में पी/ई (प्रोग्राम/इरेज़) चक्रों की एक सीमित संख्या होती है, लेकिन यह वर्तमान में नियंत्रण में है क्योंकि फ्लैश-आधारित एसएसडी पर वारंटी वर्तमान हार्ड ड्राइव के संपर्क में हैं।[150] इसके अलावा, एसएसडी पर हटाए गए फाइलें ताजा डेटा द्वारा अधिलेखित होने से पहले अनिश्चित काल के लिए समय के लिए रह सकती हैं;चुंबकीय हार्ड डिस्क ड्राइव पर अच्छी तरह से काम करने वाली ERASURE या SHRED तकनीक या सॉफ़्टवेयर का SSDs, सुरक्षा और फोरेंसिक परीक्षा से समझौता करने पर कोई प्रभाव नहीं पड़ता है।हालाँकि, तथाकथित ट्रिम (कंप्यूटिंग)#SD/MMC के कारण। ट्रिम कमांड को अधिकांश ठोस राज्य ड्राइव द्वारा नियोजित किया गया है, जो हटाए गए फ़ाइल द्वारा कब्जा किए गए तार्किक ब्लॉक पते को चिह्नित करता है, जो कचरा संग्रह को सक्षम करने के लिए अप्रयुक्त है, डेटा रिकवरी सॉफ्टवेयर सक्षम नहीं हैइस तरह से हटाए गए फ़ाइलों को पुनर्स्थापित करने के लिए।

संबंधपरक डेटाबेस या अन्य प्रणालियों के लिए जिन्हें एसिड लेनदेन की आवश्यकता होती है, यहां तक कि फ्लैश स्टोरेज की एक मामूली मात्रा भी डिस्क ड्राइव के सरणियों पर विशाल स्पीडअप की पेशकश कर सकती है।[151][152] मई 2006 में, सैमसंग इलेक्ट्रॉनिक्स ने दो फ्लैश-मेमोरी आधारित पीसी की घोषणा की, Q1-SSD और Q30-SSD को जून 2006 में उपलब्ध होने की उम्मीद थी, दोनों में से दोनों ने 32 & nbsp; GB SSD का उपयोग किया था, और कम से कम शुरू में केवल दक्षिण कोरिया में उपलब्ध थे।।[153] Q1-SSD और Q30-SSD लॉन्च में देरी हुई और अंत में अगस्त 2006 के अंत में भेज दिया गया।[154] उपलब्ध होने वाला पहला फ्लैश-मेमोरी आधारित पीसी सोनी वैयो यूएक्स 90 था, जिसे 27 जून 2006 को प्री-ऑर्डर के लिए घोषित किया गया था और 3 जुलाई 2006 को 16 जीबी फ्लैश मेमोरी हार्ड ड्राइव के साथ जापान में भेज दिया जाना शुरू हुआ।[155] सितंबर 2006 के अंत में सोनी ने VAIO UX90 में फ्लैश-मेमोरी को 32GB में अपग्रेड किया।[156] एक ठोस-राज्य ड्राइव को 2008 में पेश की गई पहली मैकबुक एयर के साथ एक विकल्प के रूप में पेश किया गया था, और 2010 के बाद से, सभी मॉडलों को एक एसएसडी के साथ भेज दिया गया था।2011 के अंत में, इंटेल की अल्ट्राबुक पहल के हिस्से के रूप में, अल्ट्रा-पतली लैपटॉप की बढ़ती संख्या को एसएसडीएस मानक के साथ भेज दिया जा रहा है।

हाइब्रिड ड्राइव और रेडीबॉस्ट जैसी हाइब्रिड तकनीकें भी हैं जो दोनों प्रौद्योगिकियों के लाभों को संयोजित करने का प्रयास करती हैं, डिस्क पर फ़ाइलों के लिए एक उच्च गति वाले गैर-वाष्पशील कैश के रूप में फ्लैश का उपयोग करते हुए, जो अक्सर संदर्भित की जाती हैं, लेकिन शायद ही कभी संशोधित, जैसे कि एप्लिकेशन औरऑपरेटिंग सिस्टम निष्पादन योग्य फ़ाइलें।

फ्लैश मेमोरी के रूप में रैम

As of 2012,[update] मुख्य कंप्यूटर मेमोरी, डायनेमिक रैंडम-एक्सेस मेमोरी के रूप में फ्लैश मेमोरी का उपयोग करने के प्रयास हैं। DRAM।[157]

अभिलेखीय या दीर्घकालिक भंडारण

फ्लैश स्टोरेज डिवाइस होल्ड चार्ज में फ्लोटिंग-गेट ट्रांजिस्टर जो डेटा का प्रतिनिधित्व करता है।यह चार्ज धीरे -धीरे समय के साथ लीक हो जाता है, जिससे तार्किक त्रुटियों का संचय होता है, जिसे बिट रोट या बिट लुप्त होती भी कहा जाता है।[158]

डेटा प्रतिधारण

यह स्पष्ट नहीं है कि फ्लैश मेमोरी पर डेटा कितने समय तक अभिलेखीय परिस्थितियों में बने रहेगा (यानी, सौम्य तापमान और नमी के साथ या बिना रोगनिरोधी पुनर्लेखन के बिना पहुंच के साथ)।Atmel के फ्लैश-आधारित Atmega माइक्रोकंट्रोलर्स के Datasheets आमतौर पर 85 & nbsp; ° C (185 & nbsp; ° F) और 100 साल 25 & nbsp; ° C (77 & nbsp; ° F) पर 20 साल के प्रतिधारण समय का वादा करते हैं।[159] रिटेंशन स्पैन फ्लैश स्टोरेज के प्रकारों और मॉडलों के बीच भिन्न होता है।जब बिजली और निष्क्रिय के साथ आपूर्ति की जाती है, तो डेटा रखने वाले ट्रांजिस्टर का प्रभार फ्लैश स्टोरेज के फर्मवेयर द्वारा नियमित रूप से ताज़ा किया जाता है।[158] डेटा को बनाए रखने की क्षमता फर्मवेयर, डेटा अतिरेक और त्रुटि सुधार एल्गोरिदम में अंतर के कारण फ्लैश स्टोरेज उपकरणों के बीच भिन्न होती है।[160] 2015 में सीएमयू के एक लेख में आज के फ्लैश डिवाइस हैं, जिन्हें फ्लैश रिफ्रेश की आवश्यकता नहीं है, कमरे के तापमान पर 1 वर्ष की एक विशिष्ट अवधारण आयु है।और यह प्रतिधारण समय बढ़ते तापमान के साथ तेजी से कम हो जाता है।घटना को अरहेनियस समीकरण द्वारा मॉडल किया जा सकता है।[161][162]

FPGA कॉन्फ़िगरेशन

कुछ FPGA फ्लैश कॉन्फ़िगरेशन कोशिकाओं पर आधारित होते हैं, जिनका उपयोग सीधे (प्रोग्रामेबल) के रूप में किया जाता है, जो आंतरिक तत्वों को एक साथ जोड़ने के लिए स्विच करता है, उसी तरह के फ्लोटिंग-गेट ट्रांजिस्टर का उपयोग करके डेटा स्टोरेज डिवाइसेस में फ्लैश डेटा स्टोरेज सेल के रूप में।[147]

उद्योग

एक स्रोत के अनुसार, वर्ष 2008 में फ्लैश मेमोरी उद्योग में उत्पादन और बिक्री में लगभग 9.1 अरब अमेरिकी डॉलर का व्यय सम्मिलित था। अन्य स्रोतों ने वर्ष 2006 में फ्लैश मेमोरी बाजार को 20 अरब अमेरिकी डॉलर से अधिक के व्ययक्षेत्र में सम्मिलित किया, जो संपूर्ण अर्धचालक बाजार के 8 प्रतिशत से और संपूर्ण अर्धचालक मेमोरी बाजार के 34 प्रतिशत से अधिक था।[163] बाजार का अनुमानित व्यय वर्ष 2012 में 26.8 अरब डॉलर था।[164] एक फ्लैश मेमोरी चिप का उत्पादन करने में लगभग 10 सप्ताह तक का समय लगता है।[165]

निर्माता

वर्ष 2019 की पहली तिमाही तक सबसे बड़े NAND फ्लैश मेमोरी निर्माता निम्न थे।[166]

- सैमसंग इलेक्ट्रॉनिक्स – 34.9%

- किओक्सिया (Kioxia) – 18.1%

- पश्चिमी डिजिटल निगम – 14%

- माइक्रोन (Micron) प्रौद्योगिकी – 13.5%

- SK हाइनिक्स – 10.3%

- इन्टेल – 8.7% (नोट: SK Hynix ने 2021 के अंत में इंटेल के NAND व्यवसाय का अधिग्रहण किया)[167]

वर्ष 2022 की पहली तिमाही तक सैमसंग सबसे बड़ा NAND फ्लैश मेमोरी निर्माता है।[168]

शिपमेंट

| वर्ष | असतत फ़्लैश मेमोरी चिप | फ़्लैश मेमोरी की डेटा क्षमता (गीगाबाईट में) | चलायमान गेट MOSFET मेमोरी कोश (बिलियन में) |

|---|---|---|---|

| 1992 | 26,000,000[169] | 3[169] | 24[lower-alpha 1] |

| 1993 | 73,000,000[169] | 17[169] | 139[lower-alpha 1] |

| 1994 | 112,000,000[169] | 25[169] | 203[lower-alpha 1] |

| 1995 | 235,000,000[169] | 38[169] | 300[lower-alpha 1] |

| 1996 | 359,000,000[169] | 140[169] | 1,121[lower-alpha 1] |

| 1997 | 477,200,000+[170] | 317+ | 2,533+[lower-alpha 1] |

| 1998 | 762,195,122[171] | 455+ | 3,642+[lower-alpha 1] |

| 1999 | 12,800,000,000[172] | 635+ | 5,082+[lower-alpha 1] |

| 2000–2004 | 134,217,728,000 (NAND)[173] | 1,073,741,824,000 (NAND)[173] | |

| 2005–2007 | ? | ||

| 2008 | 1,226,215,645 (mobile NAND)[174] | ||

| 2009 | 1,226,215,645+ (mobile NAND) | ||

| 2010 | 7,280,000,000+[lower-alpha 2] | ||

| 2011 | 8,700,000,000[176] | ||

| 2012 | 5,151,515,152 (serial)[177] | ||

| 2013 | ? | ||

| 2014 | ? | 59,000,000,000[178] | 118,000,000,000+[lower-alpha 1] |

| 2015 | 7,692,307,692 (NAND)[179] | 85,000,000,000[180] | 170,000,000,000+[lower-alpha 1] |

| 2016 | ? | 100,000,000,000[181] | 200,000,000,000+[lower-alpha 1] |

| 2017 | ? | 148,200,000,000[lower-alpha 3] | 296,400,000,000+[lower-alpha 1] |

| 2018 | ? | 231,640,000,000[lower-alpha 4] | 463,280,000,000+[lower-alpha 1] |

| 2019 | ? | ? | ? |

| 2020 | ? | ? | ? |

| 1992–2020 | 45,358,454,134+ मेमोरी चिप | 758,057,729,630+ गीगाबाइट | 2,321,421,837,044+ अरब कोश |

एकल फ्लैश मेमोरी चिपों को छोड़कर फ्लैश मेमोरी को माइक्रोकंट्रोलर (MCU) चिपों और सिस्टम-ऑन-चिप (SoC) उपकरणों में भी अन्तर्निहित (embed) किया जाता है।[185] फ्लैश मेमोरी एआरएम चिप्स में अंतर्निहित है[185], जिसने 2019 तक दुनिया भर में 150 बिलियन यूनिट्स की बिक्री की है[186], और प्रोग्रामेबल सिस्टम-ऑन-चिप (पीएसओसी) उपकरणों में, जो 2012 तक 1.1 बिलियन यूनिट्स की बिक्री कर चुके हैं।[187] इसके बाद कम से कम 151.1 अरब अन्तर्निहित (embedded) फ्लैश मेमोरी वाली MCU और SoC चिपों की चिपों की बिक्री हुई, और वर्ष 2015 तक 45.4 अरब प्रसिद्ध एकल फ्लैश चिप बिक्री के अलावा, कम से कम 196.5 बिलियन फ्लैश मेमोरी वाले चिपों की बिक्री हुई।

फ्लैश मापनीयता (Flash Scalability)

इसकी अपेक्षाकृत सरल संरचना और उच्च क्षमता की उच्च माँग के कारण, NAND फ्लैश मेमोरी इलेक्ट्रॉनिक उपकरणों के बीच सबसे मजबूती से मापी गई तकनीक है। कुछ शीर्ष निर्माताओं के बीच भारी प्रतिस्पर्धा चलायमान-गेट MOSFET डिज़ाइन नियम या प्रक्रिया प्रौद्योगिकी नोड को सिकोड़ने में केवल आक्रामकता को जोड़ती है।[86] जबकि अपेक्षित सिकुड़न समयरेखा मूर के नियम के मूल संस्करण के अनुसार दो प्रत्येक तीन साल का एक कारक है, हाल ही में NAND फ्लैश के सम्बन्ध में इसे दो प्रत्येक दो साल के कारक तक बढ़ा दिया गया है।

| ITRS या कम्पनी | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |

|---|---|---|---|---|---|---|---|---|---|

| ITRS फ़्लैश रोडमैप 2011[188] | 32 nm | 22 nm | 20 nm | 18 nm | 16 nm | ||||

| सम्पादित ITRS फ़्लैश रोडमैप[189] | 17 nm | 15 nm | 14 nm | ||||||

| सैमसंग (Samsung)[188][189][190] (सैमसंग 3D NAND)[189] |

35–20 nm[29] | 27 nm | 21 nm (MLC, TLC) |

19–16 nm 19–10 nm (MLC, TLC)[191] |

19–10 nm V-NAND (24L) |

16–10 nm V-NAND (32L) |

16–10 nm | 12–10 nm | 12–10 nm |

| माइक्रोन (Micron), इंटेल (Intel)[188][189][190] | 34–25 nm | 25 nm | 20 nm (MLC + HKMG) |

20 nm (TLC) |

16 nm | 16 nm 3D NAND |

16 nm 3D NAND |

12 nm 3D NAND |

12 nm 3D NAND |

| तोशीबा (Toshiba), WD (SanDisk)[188][189][190] | 43–32 nm 24 nm (Toshiba)[192] |

24 nm | 19 nm (MLC, TLC) |

15 nm | 15 nm 3D NAND |

15 nm 3D NAND |

12 nm 3D NAND |

12 nm 3D NAND | |

| SK हाइनिक्स (SK Hynix)[188][189][190] | 46–35 nm | 26 nm | 20 nm (MLC) | 16 nm | 16 nm | 16 nm | 12 nm | 12 nm |

जैसे ही फ्लैश मेमोरी सेल के MOSFET फीचर का आकार 15-16 nm की न्यूनतम सीमा तक पहुँच जाता है, फ्लैश घनत्व में वृद्धि TLC (3 बिट प्रति सेल) द्वारा संचालित होती है, जो NAND मेमोरी तलों के ऊर्ध्वाधर संग्रहण के साथ जुड़ा है। सहनशक्ति में कमी और फीचर का आकार सिकुड़ने के साथ-साथ अपरिवर्तनीय बिट त्रुटि दरों में वृद्धि को बेहतर त्रुटि सुधार तंत्र द्वारा सहयोग दिया जा सकता है।[193] इस विकास के साथ भी इलेक्ट्रॉन की संख्या धारण की कम क्षमता के कारण छोटे से छोटे आयामों में फ्लैश को आर्थिक रूप से मापना असंभव हो सकता है। कई आशाजनक नई प्रौद्योगिकियाँ (जैसे कि FeRAM, MRAM, PMC, PCM, ReRAM, और अन्य) फ्लैश के लिए अधिक मापनीय प्रतिस्थापन के रूप में जांच और विकास के कार्यरत हैं।[194]

टाइमलाइन

| आगमन की तिथि | चिप का नाम | मेमोरी पैकेज क्षमता मेगाबाइट (Mb), गीगाबाइट (Gb), टेराबाइट (Tb) |

फ़्लैश का प्रकार | कोश का प्रकार | परतों या परतों के समूहों की संख्या | विनिर्माता | प्रक्रिया | क्षेत्रफल | सन्दर्भ |

|---|---|---|---|---|---|---|---|---|---|

| 1984 | ? | ? | NOR | SLC | 1 | Toshiba | ? | ? | [19] |

| 1985 | ? | 256 kb | NOR | SLC | 1 | Toshiba | 2,000 nm | ? | [26] |

| 1987 | ? | ? | NAND | SLC | 1 | Toshiba | ? | ? | [1] |

| 1989 | ? | 1 Mb | NOR | SLC | 1 | Seeq, Intel | ? | ? | [26] |

| 4 Mb | NAND | SLC | 1 | Toshiba | 1,000 nm | ||||

| 1991 | ? | 16 Mb | NOR | SLC | 1 | Mitsubishi | 600 nm | ? | [26] |

| 1993 | DD28F032SA | 32 Mb | NOR | SLC | 1 | Intel | ? | 280 mm² | [195][196] |

| 1994 | ? | 64 Mb | NOR | SLC | 1 | NEC | 400 nm | ? | [26] |

| 1995 | ? | 16 Mb | DINOR | SLC | 1 | Mitsubishi, Hitachi | ? | ? | [26][197] |

| NAND | SLC | 1 | Toshiba | ? | ? | [198] | |||

| 32 Mb | NAND | SLC | 1 | Hitachi, Samsung, Toshiba | ? | ? | [26] | ||

| 34 Mb | Serial | SLC | 1 | SanDisk | |||||

| 1996 | ? | 64 Mb | NAND | SLC | 1 | Hitachi, Mitsubishi | 400 nm | ? | [26] |

| QLC | 1 | NEC | |||||||

| 128 Mb | NAND | SLC | 1 | Samsung, Hitachi | ? | ||||

| 1997 | ? | 32 Mb | NOR | SLC | 1 | Intel, Sharp | 400 nm | ? | [199] |

| NAND | SLC | 1 | AMD, Fujitsu | 350 nm | |||||

| 1999 | ? | 256 Mb | NAND | SLC | 1 | Toshiba | 250 nm | ? | [26] |

| MLC | 1 | Hitachi | 1 | ||||||

| 2000 | ? | 32 Mb | NOR | SLC | 1 | Toshiba | 250 nm | ? | [26] |

| 64 Mb | NOR | QLC | 1 | STMicroelectronics | 180 nm | ||||

| 512 Mb | NAND | SLC | 1 | Toshiba | ? | ? | [200] | ||

| 2001 | ? | 512 Mb | NAND | MLC | 1 | Hitachi | ? | ? | [26] |

| 1 Gibit | NAND | MLC | 1 | Samsung | |||||

| 1 | Toshiba, SanDisk | 160 nm | ? | [201] | |||||

| 2002 | ? | 512 Mb | NROM | MLC | 1 | Saifun | 170 nm | ? | [26] |

| 2 Gb | NAND | SLC | 1 | Samsung, Toshiba | ? | ? | [202][203] | ||

| 2003 | ? | 128 Mb | NOR | MLC | 1 | Intel | 130 nm | ? | [26] |

| 1 Gb | NAND | MLC | 1 | Hitachi | |||||

| 2004 | ? | 8 Gb | NAND | SLC | 1 | Samsung | 60 nm | ? | [202] |

| 2005 | ? | 16 Gb | NAND | SLC | 1 | Samsung | 50 nm | ? | [29] |

| 2006 | ? | 32 Gb | NAND | SLC | 1 | Samsung | 40 nm | ||

| Apr-07 | THGAM | 128 Gb | Stacked NAND | SLC | Toshiba | 56 nm | 252 mm² | [44] | |

| Sep-07 | ? | 128 Gb | Stacked NAND | SLC | Hynix | ? | ? | [45] | |

| 2008 | THGBM | 256 Gb | Stacked NAND | SLC | Toshiba | 43 nm | 353 mm² | [46] | |

| 2009 | ? | 32 Gb | NAND | TLC | Toshiba | 32 nm | 113 mm² | [27] | |

| 64 Gb | NAND | QLC | Toshiba, SanDisk | 43 nm | ? | [27][28] | |||

| 2010 | ? | 64 Gb | NAND | SLC | Hynix | 20 nm | ? | [204] | |

| TLC | Samsung | 20 nm | ? | [29] | |||||

| THGBM2 | 1 Tb | संगृहीत NAND | QLC | Toshiba | 32 nm | 374 mm² | [47] | ||

| 2011 | KLMCG8GE4A | 512 Gb | संगृहीत NAND | MLC | Samsung | ? | 192 mm² | [205] | |

| 2013 | ? | ? | NAND | SLC | SK Hynix | 16 nm | ? | [204] | |

| 128 Gb | V-NAND | TLC | Samsung | 10 nm | ? | ||||

| 2015 | ? | 256 Gb | V-NAND | TLC | Samsung | ? | ? | [191] | |

| 2017 | eUFS 2.1 | 512 Gb | V-NAND | TLC | 8 of 64 | Samsung | ? | ? | [50] |

| 768 Gb | V-NAND | QLC | Toshiba | ? | ? | [206] | |||

| KLUFG8R1EM | 4 Tb | संगृहीत V-NAND | TLC | Samsung | ? | 150 mm² | [50] | ||

| 2018 | ? | 1 Tb | V-NAND | QLC | Samsung | ? | ? | [207] | |

| 1.33 Tb | V-NAND | QLC | Toshiba | ? | 158 mm² | [208][209] | |||

| 2019 | ? | 512 Gb | V-NAND | QLC | Samsung | ? | ? | [51][52] | |

| 1 Tb | V-NAND | TLC | SK Hynix | ? | ? | [210] | |||

| eUFS 2.1 | 1 Tb | संगृहीत V-NAND[211] | QLC | 16 of 64 | Samsung | ? | 150 mm² | [51][52][212] |

यह भी देखें

- EMMC

- फ्लैश मेमोरी कंट्रोलर

- फ्लैश फ़ाइल सिस्टम की सूची

- फ्लैश मेमोरी कंट्रोलर निर्माताओं की सूची

- microsdxc (2 & nbsp; tb), और उत्तराधिकारी प्रारूप सुरक्षित डिजिटल अल्ट्रा क्षमता (SDUC) 128 & nbsp; tib तक कार्ड का समर्थन करते हैं

- ओपन NAND फ्लैश इंटरफ़ेस वर्किंग ग्रुप

- पढ़ें-मेमोरी (RMM)

- यूनिवर्सल फ्लैश स्टोरेज

- USB फ्लैश ड्राइव सुरक्षा

- प्रवर्धन लिखें

टिप्पणियाँ

- ↑ 1.00 1.01 1.02 1.03 1.04 1.05 1.06 1.07 1.08 1.09 1.10 1.11 1.12 Single-level cell (1-bit per cell) up until 2009. Multi-level cell (up to 4-bit or half-byte per cell) commercialised in 2009.[27][28]

- ↑ Flash memory chip shipments in 2010:

- NOR – 3.64 billion[175]

- NAND – 3.64 billion+ (est.)

- ↑ Flash memory data capacity shipments in 2017:

- NAND non-volatile memory (NVM) – 85 exabytes (est.)[182]

- Solid-state drive (SSD) – 63.2 exabytes[183]

- ↑ Flash memory data capacity shipments in 2018 (est.)

संदर्भ

- ↑ 1.0 1.1 1.2 "1987: Toshiba Launches NAND Flash". eWeek. 11 April 2012. Retrieved 20 June 2019.

- ↑ "A Flash Storage Technical and Economic Primer". FlashStorage.com. 30 March 2015. Archived from the original on 20 July 2015.

- ↑ "What is Flash Memory". Bitwarsoft.com. 22 July 2020.

- ↑ "TN-04-42: Memory Module Serial Presence-Detect Introduction" (PDF). Micron. Retrieved 1 June 2022.

- ↑ "What is serial presence detect (SPD)? - Definition from WhatIs.com". WhatIs.com.

- ↑ Shilov, Anton. "Samsung Starts Production of 1 TB eUFS 2.1 Storage for Smartphones". AnandTech.com.

- ↑ Shilov, Anton. "Samsung Starts Production of 512 GB UFS NAND Flash Memory: 64-Layer V-NAND, 860 MB/s Reads". AnandTech.com.