जेटीजी: Difference between revisions

No edit summary |

No edit summary |

||

| Line 18: | Line 18: | ||

=== [[डिबगिंग]] === | === [[डिबगिंग]] === | ||

हालांकि जेटीएजी के | हालांकि जेटीएजी के प्रारंभिक अनुप्रयोगों ने बोर्ड स्तर के परीक्षण को लक्षित किया, यहाँ जेटीएजी मानक को डिवाइस, बोर्ड और प्रणाली परीक्षण, [[निदान]] और दोष अलगाव में सहायता के लिए डिज़ाइन किया गया था। आज जेटीएजी का उपयोग एकीकृत परिपथों के उप-ब्लॉकों तक पहुँचने के प्राथमिक साधन के रूप में किया जाता है, जिससे यह [[ अंतः स्थापित प्रणाली ]] को डीबग करने के लिए एक आवश्यक तंत्र बन जाता है जिसमें कोई अन्य डीबग-सक्षम संचार चैनल नहीं हो सकता है।{{citation needed|reason=This statement claims that JTAG is of critical use for a certain application but doesn't provide any source that supports the statement.|date=October 2017}} अधिकांश प्रणालियों पर, जेटीएजी-आधारित [[डिबग|डिबगिंग]] सीपीयू रीसेट के बाद पहले निर्देश से उपलब्ध है, जो इसे प्रारंभिक बूट सॉफ़्टवेयर के विकास में सहायता देता है जो कुछ भी सेट होने से पहले चलता है। एक [[इन-सर्किट एमुलेटर]] (या, अधिक सही विधि से, एक जेटीएजी एडॉप्टर) जेटीएजी का उपयोग लक्ष्य सेंट्रल प्रोसेसिंग यूनिट के अंदर ऑन-चिप डिबग मॉड्यूल तक पहुँचने के लिए परिवहन तंत्र के रूप में करता है। वे मॉड्यूल सॉफ़्टवेयर विकासकर्ता को एक एम्बेडेड प्रणाली के सॉफ़्टवेयर को आवश्यकता पड़ने पर सीधे मशीन निर्देश स्तर पर, या (अधिक विशिष्ट रूप से) उच्च स्तरीय भाषा स्रोत कोड के संदर्भ में डीबग करने देते हैं। | ||

प्रणाली सॉफ़्टवेयर डिबग समर्थन कई सॉफ़्टवेयर | प्रणाली सॉफ़्टवेयर डिबग समर्थन कई सॉफ़्टवेयर विकासकर्ता के लिए जेटीएजी में रुचि रखने का मुख्य कारण है। कई सिलिकॉन आर्किटेक्चर जैसे कि पावरपीसी, एमआईपीएस, एआरएम, और एक्स86 ने मूल जेटीएजी प्रोटोकॉल के आसपास एक संपूर्ण सॉफ़्टवेयर डीबग, निर्देश ट्रेसिंग और डेटा ट्रेसिंग इन्फ्रास्ट्रक्चर का निर्माण किया। अक्सर व्यक्तिगत सिलिकॉन विक्रेता इन एक्सटेंशनों के कुछ हिस्सों को ही प्रायुक्त करते हैं। कुछ उदाहरण एआरएम [[कोरसाइट]] और [[नेक्सस (मानक)]] के साथ-साथ इंटेल के बीटीएस (ब्रांच ट्रेस स्टोरेज), एलबीआर (लास्ट ब्रांच रिकॉर्ड), और आईपीटी (इंटेल प्रोसेसर ट्रेस) कार्यान्वयन हैं। ऐसे कई अन्य सिलिकॉन विक्रेता-विशिष्ट एक्सटेंशन हैं, जिन्हें गैर-प्रकटीकरण समझौते के अलावा प्रलेखित नहीं किया जा सकता है। जेटीएजी मानक को अपनाने से जेटीएजी-केंद्रित डिबगिंग वातावरण को प्रारंभिक प्रोसेसर-विशिष्ट डिज़ाइनों से दूर करने में मदद मिली। प्रोसेसर को सामान्य रूप से रोका जा सकता है, सिंगल स्टेप किया जा सकता है, या स्वतंत्र रूप से चलने दिया जा सकता है। रैम में कोड के लिए (अक्सर एक विशेष मशीन निर्देश का उपयोग करके) और रैम/फ़्लैश दोनों में कोड ब्रेकप्वाइंट सेट कर सकते हैं। डेटा ब्रेकप्वाइंट अक्सर उपलब्ध होते हैं, जैसा कि रैम में बल्क डेटा डाउनलोड होता है। अधिकांश डिज़ाइनों में हाल्ट मोड डिबगिंग है, लेकिन कुछ डिबगर्स को रजिस्टरों और डेटा बसों तक पहुंचने की अनुमति देते हैं, बिना कोर को डिबग किए रोकने की आवश्यकता होती है। कुछ टूलचेन एआरएम एंबेडेड ट्रेस मैक्रोसेल (ईटीएम) मॉड्यूल या अन्य आर्किटेक्चर में समकक्ष कार्यान्वयन का उपयोग कर सकते हैं, जो [[तर्क विश्लेषक]] जैसे जटिल हार्डवेयर घटनाओं पर डिबगर (या ट्रेसिंग) गतिविधि को ट्रिगर करने के लिए प्रोग्राम किया जाता है, जो एक विशेष सबरूटीन से एक रजिस्टर में पहले सात एक्सेस को अनदेखा करने के लिए प्रोग्राम किया जाता है। | ||

कभी-कभी [[एफपीजीए]] डेवलपर डीबगिंग टूल विकसित करने के लिए जेटीएजी का भी उपयोग करते हैं।<ref name="fpga">[http://www.embeddeddesignindia.co.in/ART_8800568419_2800006_TA_d2d96055.HTM Select the right FPGA debug method] {{Webarchive|url=https://web.archive.org/web/20100427145744/http://www.embeddeddesignindia.co.in/ART_8800568419_2800006_TA_d2d96055.HTM |date=27 April 2010 }} presents one of the models for such tools.</ref> [[ CPU | सीपीयू]] के अंदर चलने वाले सॉफ़्टवेयर को डिबग करने के लिए उपयोग की जाने वाली वही जेटीएजी तकनीकें | कभी-कभी [[एफपीजीए]] डेवलपर डीबगिंग टूल विकसित करने के लिए जेटीएजी का भी उपयोग करते हैं।<ref name="fpga">[http://www.embeddeddesignindia.co.in/ART_8800568419_2800006_TA_d2d96055.HTM Select the right FPGA debug method] {{Webarchive|url=https://web.archive.org/web/20100427145744/http://www.embeddeddesignindia.co.in/ART_8800568419_2800006_TA_d2d96055.HTM |date=27 April 2010 }} presents one of the models for such tools.</ref> [[ CPU | सीपीयू]] के अंदर चलने वाले सॉफ़्टवेयर को डिबग करने के लिए उपयोग की जाने वाली वही जेटीएजी तकनीकें एफपीजीए के अंदर अन्य डिजिटल डिज़ाइन ब्लॉक को डीबग करने में मदद कर सकती हैं। उदाहरण के लिए, कस्टम जेटीएजी निर्देश एफपीजीए के अंदर संकेतों के मनमाने सेट से निर्मित पठन रजिस्टरों को अनुमति देने के लिए प्रदान किए जा सकते हैं, जो उन व्यवहारों के लिए दृश्यता प्रदान करते हैं जो सीमा स्कैन संचालन के लिए अदृश्य हैं। इसी तरह, ऐसे रजिस्टर लिखने से नियंत्रणीयता मिल सकती है जो अन्यथा उपलब्ध नहीं है। | ||

=== फर्मवेयर भंडारण === | === फर्मवेयर भंडारण === | ||

जेटीएजी [[प्रोग्रामर (हार्डवेयर)]] को डेटा को आंतरिक गैर-वाष्पशील डिवाइस मेमोरी (जैसे [[ जटिल प्रोग्रामेबल लॉजिक डिवाइस ]]) में स्थानांतरित करने की अनुमति देता है। कुछ डिवाइस प्रोग्रामर प्रोग्रामिंग के साथ-साथ डिवाइस को डिबग करने के लिए एक दोहरे उद्देश्य की पूर्ति करते हैं। | जेटीएजी [[प्रोग्रामर (हार्डवेयर)]] को डेटा को आंतरिक गैर-वाष्पशील डिवाइस मेमोरी (जैसे [[ जटिल प्रोग्रामेबल लॉजिक डिवाइस ]]) में स्थानांतरित करने की अनुमति देता है। कुछ डिवाइस प्रोग्रामर प्रोग्रामिंग के साथ-साथ डिवाइस को डिबग करने के लिए एक दोहरे उद्देश्य की पूर्ति करते हैं। एफपीजीए के मामले में, सामान्य रूप से विकास कार्य के दौरान जेटीएजी पोर्ट के माध्यम से अस्थिर स्मृति उपकरणों को भी प्रोग्राम किया जा सकता है। इसके अलावा, आंतरिक निगरानी क्षमताओं (तापमान, वोल्टेज और करंट) को जेटीएजी पोर्ट के माध्यम से एक्सेस किया जा सकता है। | ||

जेटीएजी प्रोग्रामर का उपयोग सॉफ्टवेयर और डेटा को [[फ्लैश मेमोरी]] में लिखने के लिए भी किया जाता है। यह आमतौर पर उसी डेटा बस एक्सेस का उपयोग करके किया जाता है जिसका सीपीयू उपयोग करेगा, और कभी-कभी सीपीयू द्वारा नियंत्रित किया जाता है। अन्य मामलों में मेमोरी चिप्स में स्वयं जेटीएजी इंटरफेस होता है। कुछ आधुनिक डिबग आर्किटेक्चर सीपीयू को रोकने और लेने की आवश्यकता के बिना आंतरिक और बाहरी बस मास्टर एक्सेस प्रदान करते हैं। सबसे खराब स्थिति में, सीमा स्कैन सुविधा का उपयोग करके बाहरी बस संकेतों को चलाना आमतौर पर संभव है। | जेटीएजी प्रोग्रामर का उपयोग सॉफ्टवेयर और डेटा को [[फ्लैश मेमोरी]] में लिखने के लिए भी किया जाता है। यह आमतौर पर उसी डेटा बस एक्सेस का उपयोग करके किया जाता है जिसका सीपीयू उपयोग करेगा, और कभी-कभी सीपीयू द्वारा नियंत्रित किया जाता है। अन्य मामलों में मेमोरी चिप्स में स्वयं जेटीएजी इंटरफेस होता है। कुछ आधुनिक डिबग आर्किटेक्चर सीपीयू को रोकने और लेने की आवश्यकता के बिना आंतरिक और बाहरी बस मास्टर एक्सेस प्रदान करते हैं। सबसे खराब स्थिति में, सीमा स्कैन सुविधा का उपयोग करके बाहरी बस संकेतों को चलाना आमतौर पर संभव है। | ||

एक व्यावहारिक मामले के रूप में, एक एम्बेडेड प्रणाली विकसित करते समय, निर्देश स्टोर का अनुकरण करना डिबग चक्र (संपादन, संकलन, डाउनलोड, परीक्षण और डिबग) को प्रायुक्त करने का सबसे तेज़ तरीका है।{{citation needed|date=June 2015}} इसका कारण यह है कि इन-सर्किट इम्यूलेटर एक इंस्ट्रक्शन स्टोर का अनुकरण करता है, जिसे | एक व्यावहारिक मामले के रूप में, एक एम्बेडेड प्रणाली विकसित करते समय, निर्देश स्टोर का अनुकरण करना डिबग चक्र (संपादन, संकलन, डाउनलोड, परीक्षण और डिबग) को प्रायुक्त करने का सबसे तेज़ तरीका है।{{citation needed|date=June 2015}} इसका कारण यह है कि इन-सर्किट इम्यूलेटर एक इंस्ट्रक्शन स्टोर का अनुकरण करता है, जिसे यूएसबी के माध्यम से डेवलपमेंट होस्ट से बहुत जल्दी अपडेट किया जा सकता है। फ्लैश पर फर्मवेयर अपलोड करने के लिए सीरियल यूएआरटी पोर्ट और बूटलोडर का उपयोग करना इस डीबग चक्र को उपकरणों के मामले में काफी धीमा और संभवतः महंगा बनाता है; जेटीएजी के माध्यम से फर्मवेयर को फ्लैश (या फ्लैश के बजाय एसरैम) में स्थापित करना इन चरम सीमाओं के बीच एक मध्यवर्ती समाधान है। | ||

=== सीमा स्कैन परीक्षण === | === सीमा स्कैन परीक्षण === | ||

| Line 36: | Line 36: | ||

जेटीएजी सीमा स्कैन तकनीक डिवाइस पिन सहित एक जटिल एकीकृत सर्किट के कई तर्क संकेतों तक पहुंच प्रदान करती है। टीएपी के माध्यम से सुलभ सीमा स्कैन रजिस्टर (बीएसआर) में संकेतों का प्रतिनिधित्व किया जाता है। यह परीक्षण और डिबगिंग के लिए संकेतों की स्थिति को नियंत्रित करने के साथ-साथ परीक्षण की अनुमति देता है। इसलिए, सॉफ्टवेयर और हार्डवेयर (निर्माण) दोनों दोषों का पता लगाया जा सकता है और एक ऑपरेटिंग डिवाइस की निगरानी की जा सकती है। | जेटीएजी सीमा स्कैन तकनीक डिवाइस पिन सहित एक जटिल एकीकृत सर्किट के कई तर्क संकेतों तक पहुंच प्रदान करती है। टीएपी के माध्यम से सुलभ सीमा स्कैन रजिस्टर (बीएसआर) में संकेतों का प्रतिनिधित्व किया जाता है। यह परीक्षण और डिबगिंग के लिए संकेतों की स्थिति को नियंत्रित करने के साथ-साथ परीक्षण की अनुमति देता है। इसलिए, सॉफ्टवेयर और हार्डवेयर (निर्माण) दोनों दोषों का पता लगाया जा सकता है और एक ऑपरेटिंग डिवाइस की निगरानी की जा सकती है। | ||

[[ अंतर्निहित स्व-परीक्षण ]] (बिल्ट-इन सेल्फ-टेस्ट) के साथ संयुक्त होने पर, जेटीएजी स्कैन चेन कुछ स्थैतिक दोषों (शॉर्ट्स, ओपन्स और लॉजिक एरर्स) के लिए आईसी का परीक्षण करने के लिए कम ओवरहेड, एम्बेडेड समाधान को सक्षम करती है। स्कैन श्रृंखला तंत्र आम तौर पर होने वाले समय, तापमान या अन्य गतिशील परिचालन त्रुटियों के निदान या परीक्षण में मदद नहीं करता है। [[ परीक्षण मामला ]] अक्सर मानकीकृत प्रारूपों जैसे [[सीरियल वेक्टर प्रारूप]], या इसके बाइनरी सिबलिंग | [[ अंतर्निहित स्व-परीक्षण ]] (बिल्ट-इन सेल्फ-टेस्ट) के साथ संयुक्त होने पर, जेटीएजी स्कैन चेन कुछ स्थैतिक दोषों (शॉर्ट्स, ओपन्स और लॉजिक एरर्स) के लिए आईसी का परीक्षण करने के लिए कम ओवरहेड, एम्बेडेड समाधान को सक्षम करती है। स्कैन श्रृंखला तंत्र आम तौर पर होने वाले समय, तापमान या अन्य गतिशील परिचालन त्रुटियों के निदान या परीक्षण में मदद नहीं करता है। [[ परीक्षण मामला ]] अक्सर मानकीकृत प्रारूपों जैसे [[सीरियल वेक्टर प्रारूप]], या इसके बाइनरी सिबलिंग एक्सएसवीएफ में प्रदान किए जाते हैं, और उत्पादन परीक्षणों में उपयोग किए जाते हैं। तैयार बोर्डों पर इस तरह के परीक्षण करने की क्षमता आज के उत्पादों में [[परीक्षण के लिए डिजाइन]] का एक अनिवार्य हिस्सा है, जिससे ग्राहकों को उत्पाद भेजने से पहले पाए जाने वाले दोषों की संख्या बढ़ जाती है। | ||

== विद्युत विशेषताएँ == | == विद्युत विशेषताएँ == | ||

जेटीएजी इंटरफ़ेस चिप में जोड़ा गया एक विशेष इंटरफ़ेस है। जेटीएजी के संस्करण के आधार पर, दो, चार या पाँच पिन जोड़े जाते हैं। चार और पांच पिन इंटरफेस को डिज़ाइन किया गया है | जेटीएजी इंटरफ़ेस चिप में जोड़ा गया एक विशेष इंटरफ़ेस है। जेटीएजी के संस्करण के आधार पर, दो, चार या पाँच पिन जोड़े जाते हैं। चार और पांच पिन इंटरफेस को डिज़ाइन किया गया है कि यदि विशिष्ट शर्तें पूरी होती हैं तो एक बोर्ड पर कई चिप्स अपनी जेटीएजी लाइनों को एक साथ [[डेज़ी चेन (इलेक्ट्रिकल इंजीनियरिंग)]] से जोड़ सकते हैं।<ref>{{cite web|url=http://www.jtagtest.com/faq/jtag-ieee-1149-1/under-what-conditions-can-i-daisy-chain-jtag|title=FAQ: Under what conditions can I daisy-chain JTAG?|website=www.jtagtest.com}}</ref> दो पिन इंटरफ़ेस को इस तरह से डिज़ाइन किया गया है कि एक [[ तारक संस्थिति ]] में कई चिप्स को जोड़ा जा सकता है। किसी भी मामले में एक [[सर्किट बोर्ड]] पर सभी चिप्स तक पहुंच के लिए एक [[परीक्षण जांच]] को केवल एक जेटीएजी पोर्ट से कनेक्ट करने की आवश्यकता होती है। | ||

=== डेज़ी-जंजीर जेटीएजी (आईईईई 1149.1) === | === डेज़ी-जंजीर जेटीएजी (आईईईई 1149.1) === | ||

[[Image:Jtag chain.svg|center|जेटीएजी श्रृंखला का उदाहरण। टेस्ट रीसेट सिग्नल नहीं दिखाया गया है]]कनेक्टर पिन हैं: | [[Image:Jtag chain.svg|center|जेटीएजी श्रृंखला का उदाहरण। टेस्ट रीसेट सिग्नल नहीं दिखाया गया है]]कनेक्टर पिन हैं: | ||

# | #'''टीडीआई''' (टेस्ट डेटा इन) | ||

# | #'''टीडीओ'''(टेस्ट डेटा आउट) | ||

# | #'''टीकेके''' (परीक्षण घड़ी) | ||

# | #'''टीएमएस''' (टेस्ट मोड सेलेक्ट) | ||

# | #'''टीआरएसटी''' (टेस्ट रीसेट) वैकल्पिक। | ||

टीआरएसटी पिन परीक्षण तर्क के लिए एक वैकल्पिक सक्रिय-निम्न रीसेट है, आमतौर पर एसिंक्रोनस, लेकिन कभी-कभी सिंक्रोनस, चिप पर निर्भर करता है। यदि पिन उपलब्ध नहीं है, तो टीसीके और टीएमएस का उपयोग करके समकालिक रूप से रीसेट स्थिति में स्विच करके परीक्षण तर्क को रीसेट किया जा सकता है। ध्यान दें कि टेस्ट लॉजिक को रीसेट करने का मतलब किसी और चीज को रीसेट करना जरूरी नहीं है। आम तौर पर कुछ प्रोसेसर-विशिष्ट जेटीएजी ऑपरेशन होते हैं जो डिबग किए जा रहे चिप के सभी या हिस्से को रीसेट कर सकते हैं। | |||

चूंकि केवल एक डेटा लाइन उपलब्ध है, प्रोटोकॉल [[सीरियल संचार]] है। क्लॉक इनपुट | चूंकि केवल एक डेटा लाइन उपलब्ध है, प्रोटोकॉल [[सीरियल संचार]] है। क्लॉक इनपुट टीकेके पिन पर है। एक बिट डेटा टीडीआई से स्थानांतरित किया जाता है, और टीडीओप्रति टीकेके राइजिंग क्लॉक एज में स्थानांतरित किया जाता है। विभिन्न निर्देश लोड किए जा सकते हैं। विशिष्ट आईसी के लिए निर्देश चिप आईडी, नमूना इनपुट पिन, ड्राइव (या फ्लोट) आउटपुट पिन पढ़ सकते हैं, चिप कार्यों या बाईपास (कई चिप्स की श्रृंखला को तार्किक रूप से छोटा करने के लिए टीडीओ को पाइप टीडीआई) में हेरफेर कर सकते हैं। | ||

किसी भी क्लॉक्ड सिग्नल की तरह, | किसी भी क्लॉक्ड सिग्नल की तरह, टीडीआई को प्रस्तुत किया गया डेटा कुछ चिप-विशिष्ट ''सेटअप'' समय से पहले और प्रासंगिक (यहाँ, बढ़ते हुए) क्लॉक एज के बाद ''होल्ड'' समय के लिए मान्य होना चाहिए। टीडीओडेटा टीकेके के गिरने के बाद कुछ चिप-विशिष्ट समय के लिए मान्य है। | ||

टीसीके की अधिकतम ऑपरेटिंग आवृत्ति श्रृंखला में सभी चिप्स के आधार पर भिन्न होती है (न्यूनतम गति का उपयोग किया जाना चाहिए), लेकिन यह आमतौर पर 10-100 मेगाहर्ट्ज (100-10 एनएस प्रति बिट) है। साथ ही | टीसीके की अधिकतम ऑपरेटिंग आवृत्ति श्रृंखला में सभी चिप्स के आधार पर भिन्न होती है (न्यूनतम गति का उपयोग किया जाना चाहिए), लेकिन यह आमतौर पर 10-100 मेगाहर्ट्ज (100-10 एनएस प्रति बिट) है। साथ ही टीकेके आवृत्तियाँ बोर्ड लेआउट और जेटीएजी अडैप्टर क्षमताओं और स्थिति पर निर्भर करती हैं। एक चिप में 40 मेगाहर्टज जेटीएजी घड़ी हो सकती है, लेकिन केवल तभी जब वह गैर-जेटीएजी संचालन के लिए 200 मेगाहर्टज घड़ी का उपयोग कर रही हो; और कम पावर मोड में होने पर इसे बहुत धीमी घड़ी का उपयोग करने की आवश्यकता हो सकती है। तदनुसार, कुछ जेटीएजी एडेप्टरों में Rटीकेके (रिटर्न टीकेके) सिग्नल का उपयोग करते हुए ''अनुकूली क्लॉकिंग'' होती है। तेज़ टीकेके फ़्रीक्वेंसी सबसे अधिक उपयोगी होती है जब जेटीएजी का उपयोग बहुत अधिक डेटा स्थानांतरित करने के लिए किया जाता है, जैसे कि किसी प्रोग्राम को निष्पादन योग्य फ्लैश मेमोरी में संग्रहीत करना। | ||

एक मानकीकृत जेटीएजी [[राज्य मशीन]] के माध्यम से | एक मानकीकृत जेटीएजी [[राज्य मशीन]] के माध्यम से टीएमएस चरणों पर क्लॉकिंग परिवर्तन। जेटीएजी स्टेट मशीन रीसेट कर सकती है, एक इंस्ट्रक्शन रजिस्टर को एक्सेस कर सकती है, या इंस्ट्रक्शन रजिस्टर द्वारा चुने गए डेटा को एक्सेस कर सकती है। | ||

जेटीएजी प्लेटफॉर्म अक्सर आईईईई 1149.1 विनिर्देश द्वारा परिभाषित मुट्ठी भर संकेतों को जोड़ते हैं। एक प्रणाली रीसेट ( | जेटीएजी प्लेटफॉर्म अक्सर आईईईई 1149.1 विनिर्देश द्वारा परिभाषित मुट्ठी भर संकेतों को जोड़ते हैं। एक प्रणाली रीसेट (एसआरएसटी) सिग्नल काफी सामान्य है, डिबगर्स को पूरे प्रणाली को रीसेट करने देता है, न कि केवल जेटीएजी समर्थन वाले हिस्से को रीसेट करता है। कभी-कभी मेजबान द्वारा गतिविधि को ट्रिगर करने के लिए या जेटीएजी या शायद अतिरिक्त नियंत्रण रेखाओं के माध्यम से मॉनिटर किए जा रहे डिवाइस द्वारा ईवेंट सिग्नल का उपयोग किया जाता है। | ||

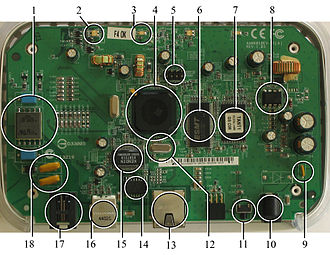

भले ही कुछ उपभोक्ता उत्पाद एक स्पष्ट जेटीएजी पोर्ट कनेक्टर प्रदान करते हैं, संयोजन अक्सर मुद्रित सर्किट बोर्ड पर विकास [[प्रोटोटाइप]] और/या उत्पादन के अवशेष के रूप में उपलब्ध होते हैं। उपयोग किए जाने पर, ये संयोजन अक्सर [[रिवर्स इंजीनियरिंग]] के लिए सबसे व्यवहार्य साधन प्रदान करते हैं। | भले ही कुछ उपभोक्ता उत्पाद एक स्पष्ट जेटीएजी पोर्ट कनेक्टर प्रदान करते हैं, संयोजन अक्सर मुद्रित सर्किट बोर्ड पर विकास [[प्रोटोटाइप]] और/या उत्पादन के अवशेष के रूप में उपलब्ध होते हैं। उपयोग किए जाने पर, ये संयोजन अक्सर [[रिवर्स इंजीनियरिंग]] के लिए सबसे व्यवहार्य साधन प्रदान करते हैं। | ||

| Line 68: | Line 68: | ||

[[File:Example of reduced pin count JTAG interface.svg|thumb|कम पिन संख्या के साथ जेटीएजी का उदाहरण]]कम पिन काउंट जेटीएजी केवल दो तारों, एक क्लॉक वायर और एक डेटा वायर का उपयोग करता है। इसे आईईईई 1149.7 मानक के भाग के रूप में परिभाषित किया गया है।<ref name="ieee-1149.7"/>कनेक्टर पिन हैं: | [[File:Example of reduced pin count JTAG interface.svg|thumb|कम पिन संख्या के साथ जेटीएजी का उदाहरण]]कम पिन काउंट जेटीएजी केवल दो तारों, एक क्लॉक वायर और एक डेटा वायर का उपयोग करता है। इसे आईईईई 1149.7 मानक के भाग के रूप में परिभाषित किया गया है।<ref name="ieee-1149.7"/>कनेक्टर पिन हैं: | ||

# | #टीएमएससी (टेस्ट सीरियल डेटा) | ||

# | #टीकेके (परीक्षण घड़ी) | ||

कॉम्पैक्ट जेटीएजी के लिए इसे | कॉम्पैक्ट जेटीएजी के लिए इसे सीजेटीएजी कहा जाता है। | ||

दो वायर इंटरफेस ने पिनों की संख्या पर दबाव कम कर दिया, और उपकरणों को स्टार टोपोलॉजी में जोड़ा जा सकता है।<ref>{{cite web|url=https://www.corelis.com/education/design-testability-tips-guidelines/major-benefits-ieee-1149-7/|title=Major Benefits of IEEE 1149.7}}</ref> स्टार टोपोलॉजी प्रणाली के कुछ हिस्सों को संचालित करने में सक्षम बनाती है, जबकि अन्य को अभी भी जेटीएजी पर एक्सेस किया जा सकता है; एक डेज़ी श्रृंखला के लिए सभी जेटीएजी इंटरफेस को संचालित करने की आवश्यकता होती है। अन्य दो-तार इंटरफेस मौजूद हैं, जैसे | दो वायर इंटरफेस ने पिनों की संख्या पर दबाव कम कर दिया, और उपकरणों को स्टार टोपोलॉजी में जोड़ा जा सकता है।<ref>{{cite web|url=https://www.corelis.com/education/design-testability-tips-guidelines/major-benefits-ieee-1149-7/|title=Major Benefits of IEEE 1149.7}}</ref> स्टार टोपोलॉजी प्रणाली के कुछ हिस्सों को संचालित करने में सक्षम बनाती है, जबकि अन्य को अभी भी जेटीएजी पर एक्सेस किया जा सकता है; एक डेज़ी श्रृंखला के लिए सभी जेटीएजी इंटरफेस को संचालित करने की आवश्यकता होती है। अन्य दो-तार इंटरफेस मौजूद हैं, जैसे समान इंटरफ़ेस मानक। | ||

== संचार मॉडल == | == संचार मॉडल == | ||

जेटीएजी में, डिवाइस एक या अधिक टेस्ट एक्सेस पोर्ट्स ( | जेटीएजी में, डिवाइस एक या अधिक टेस्ट एक्सेस पोर्ट्स (TAP) को उजागर करते हैं। ऊपर दी गई तस्वीर तीन टीएपी दिखाती है, जो अलग-अलग चिप्स हो सकती हैं या एक चिप के अंदर मॉड्यूल हो सकती हैं। टीएपी की एक डेज़ी श्रृंखला को स्कैन श्रृंखला या (शिथिल रूप से) लक्ष्य कहा जाता है। स्कैन चेन मनमाने विधि से लंबी हो सकती हैं, लेकिन व्यवहार में बीस टीएपी असामान्य रूप से लंबी होती हैं।{{Citation needed|date=June 2010}} | ||

जेटीएजी का उपयोग करने के लिए, एक होस्ट लक्ष्य के जेटीएजी सिग्नल ( | जेटीएजी का उपयोग करने के लिए, एक होस्ट लक्ष्य के जेटीएजी सिग्नल (टीएमएस, टीकेके, टीडीआई, TDO, आदि) से किसी प्रकार के जेटीएजी एडॉप्टर के माध्यम से जुड़ा होता है, जिसे लेवल शिफ्टिंग और [[ विद्युत अपघटन ]] जैसे मुद्दों को संभालने की आवश्यकता हो सकती है। एडॉप्टर कुछ इंटरफ़ेस जैसे यूएसबी, PCI, ईथरनेट, और इसके आगे के उपयोग से होस्ट से जुड़ता है। | ||

=== आदिम === | === आदिम === | ||

मेजबान टीएपी के साथ संचार करता है टीसीएस और टीडीआई को टीसीके के संयोजन के साथ जोड़कर, और टीडीओ (जो केवल मानक होस्ट-साइड इनपुट है) के माध्यम से परिणाम पढ़ता है। | मेजबान टीएपी के साथ संचार करता है टीसीएस और टीडीआई को टीसीके के संयोजन के साथ जोड़कर, और टीडीओ (जो केवल मानक होस्ट-साइड इनपुट है) के माध्यम से परिणाम पढ़ता है। टीएमएस/टीडीआई/टीकेके आउटपुट ट्रांज़िशन मूल जेटीएजी संचार आदिम बनाता है जिस पर उच्च परत प्रोटोकॉल का निर्माण होता है: | ||

* स्टेट स्विचिंग ... सभी TAP एक ही स्थिति में हैं, और | * स्टेट स्विचिंग ... सभी TAP एक ही स्थिति में हैं, और टीकेके ट्रांज़िशन पर वह स्थिति बदल जाती है। यह जेटीएजी स्टेट मशीन जेटीएजी स्पेक का हिस्सा है, और इसमें सोलह राज्य शामिल हैं। छह स्थिर अवस्थाएँ हैं जहाँ टीएमएस को स्थिर रखना अवस्था को बदलने से रोकता है। अन्य सभी राज्यों में, टीसीके हमेशा उस स्थिति को बदलता है। इसके अलावा, टीआरएसटी को जोर देकर उन स्थिर अवस्थाओं (Test_Logic_Reset) में से एक में प्रवेश करने के लिए बाध्य करता है, जो टीएमएस को पांच बार ऊपर रखने और टीसीके को साइकिल चलाने के विकल्प की तुलना में थोड़े तेज तरीके से करता है। | ||

* स्थानांतरण ... जेटीएजी राज्य मशीन के अधिकांश भाग दो स्थिर अवस्थाओं का समर्थन करते हैं जिनका उपयोग डेटा स्थानांतरित करने के लिए किया जाता है। प्रत्येक TAP में एक निर्देश रजिस्टर (IR) और एक डेटा रजिस्टर (DR) होता है। उन रजिस्टरों का आकार | * स्थानांतरण ... जेटीएजी राज्य मशीन के अधिकांश भाग दो स्थिर अवस्थाओं का समर्थन करते हैं जिनका उपयोग डेटा स्थानांतरित करने के लिए किया जाता है। प्रत्येक TAP में एक निर्देश रजिस्टर (IR) और एक डेटा रजिस्टर (DR) होता है। उन रजिस्टरों का आकार TAP के बीच भिन्न होता है, और उन रजिस्टरों को टीडीआई और टीडीओके माध्यम से जोड़कर एक बड़ा शिफ्ट रजिस्टर बनाया जाता है। (DR का आकार उस TAP के वर्तमान IR में मान का एक कार्य है, और संभवतः SCAN_N निर्देश द्वारा निर्दिष्ट मान का है।) उस शिफ्ट रजिस्टर पर परिभाषित तीन ऑपरेशन हैं: | ||

** एक अस्थायी मूल्य पर कब्जा | ** एक अस्थायी मूल्य पर कब्जा | ||

*** Shift_IR स्थिर स्थिति में प्रवेश Capture_IR स्थिति से होकर जाता है, शिफ्ट रजिस्टर को आंशिक रूप से निश्चित मान के साथ लोड करना (वर्तमान निर्देश नहीं) | *** Shift_IR स्थिर स्थिति में प्रवेश Capture_IR स्थिति से होकर जाता है, शिफ्ट रजिस्टर को आंशिक रूप से निश्चित मान के साथ लोड करना (वर्तमान निर्देश नहीं) | ||

| Line 92: | Line 92: | ||

** उस मान को बिट-दर-बिट स्थानांतरित करना, या तो Shift_IR या Shift_DR स्थिर स्थिति में; टीसीके ट्रांज़िशन शिफ्ट रजिस्टर को एक बिट शिफ्ट करता है, टीडीआई से टीडीओ की ओर, बिल्कुल एक [[सीरियल पेरिफेरल इंटरफेस बस]] मोड 1 डेटा ट्रांसफर की तरह डिवाइस की डेज़ी चेन के माध्यम से (टीएमएस = 0 के साथ चिप सेलेक्ट सिग्नल की तरह काम करता है, टीडीआई एमओएसआई, आदि के रूप में)। . | ** उस मान को बिट-दर-बिट स्थानांतरित करना, या तो Shift_IR या Shift_DR स्थिर स्थिति में; टीसीके ट्रांज़िशन शिफ्ट रजिस्टर को एक बिट शिफ्ट करता है, टीडीआई से टीडीओ की ओर, बिल्कुल एक [[सीरियल पेरिफेरल इंटरफेस बस]] मोड 1 डेटा ट्रांसफर की तरह डिवाइस की डेज़ी चेन के माध्यम से (टीएमएस = 0 के साथ चिप सेलेक्ट सिग्नल की तरह काम करता है, टीडीआई एमओएसआई, आदि के रूप में)। . | ||

** अपडेट_आईआर या अपडेट_डीआर स्थिति के माध्यम से संक्रमण पर, स्थानांतरित अस्थायी मूल्य से आईआर या डीआर अपडेट करना। ध्यान दें कि एक रजिस्टर को बिना लिखे (अपडेट) किए पढ़ना (कैप्चर) करना संभव नहीं है, और इसके विपरीत। एक सामान्य मुहावरा यह कहने के लिए फ्लैग बिट्स जोड़ता है कि क्या अपडेट के साइड इफेक्ट होने चाहिए, या हार्डवेयर ऐसे साइड इफेक्ट को निष्पादित करने के लिए तैयार है या नहीं। | ** अपडेट_आईआर या अपडेट_डीआर स्थिति के माध्यम से संक्रमण पर, स्थानांतरित अस्थायी मूल्य से आईआर या डीआर अपडेट करना। ध्यान दें कि एक रजिस्टर को बिना लिखे (अपडेट) किए पढ़ना (कैप्चर) करना संभव नहीं है, और इसके विपरीत। एक सामान्य मुहावरा यह कहने के लिए फ्लैग बिट्स जोड़ता है कि क्या अपडेट के साइड इफेक्ट होने चाहिए, या हार्डवेयर ऐसे साइड इफेक्ट को निष्पादित करने के लिए तैयार है या नहीं। | ||

* चल रहा है ... एक स्थिर अवस्था को रन_टेस्ट/निष्क्रिय कहा जाता है। भेद टीएपी-विशिष्ट है। निष्क्रिय स्थिति में | * चल रहा है ... एक स्थिर अवस्था को रन_टेस्ट/निष्क्रिय कहा जाता है। भेद टीएपी-विशिष्ट है। निष्क्रिय स्थिति में टीकेके को क्लॉक करने का कोई विशेष साइड इफेक्ट नहीं है, लेकिन इसे Run_Test स्थिति में क्लॉक करने से प्रणाली की स्थिति बदल सकती है। उदाहरण के लिए, कुछ [[ARM9]] कोर डिबगिंग मोड का समर्थन करते हैं जहां Run_Test अवस्था में टीकेके चक्र निर्देश पाइपलाइन को चलाते हैं। | ||

एक बुनियादी स्तर पर, जेटीएजी के उपयोग में निर्देश पढ़ना और लिखना और उनसे जुड़े डेटा रजिस्टर शामिल हैं; और कभी-कभी इसमें कई परीक्षण चक्र चलाना शामिल होता है। उन रजिस्टरों के पीछे हार्डवेयर है जो जेटीएजी द्वारा निर्दिष्ट नहीं है, और जिसके अपने राज्य हैं जो जेटीएजी गतिविधियों से प्रभावित हैं। | एक बुनियादी स्तर पर, जेटीएजी के उपयोग में निर्देश पढ़ना और लिखना और उनसे जुड़े डेटा रजिस्टर शामिल हैं; और कभी-कभी इसमें कई परीक्षण चक्र चलाना शामिल होता है। उन रजिस्टरों के पीछे हार्डवेयर है जो जेटीएजी द्वारा निर्दिष्ट नहीं है, और जिसके अपने राज्य हैं जो जेटीएजी गतिविधियों से प्रभावित हैं। | ||

अधिकांश जेटीएजी होस्ट दो राज्यों के बीच सबसे छोटे रास्ते का उपयोग करते हैं, शायद एडॉप्टर की विचित्रताओं से विवश। (उदाहरण के लिए, एक एडेप्टर{{Which|date=March 2010}} केवल उन पथों को संभालता है जिनकी लंबाई सात बिट्स के गुणक हैं।) जेटीएजी के शीर्ष पर निर्मित कुछ परतें राज्य के संक्रमणों की निगरानी करती हैं, और उच्च स्तर के संचालन को ट्रिगर करने के लिए असामान्य पथों का उपयोग करती हैं। कुछ एआरएम कोर दो-तार (गैर-जेटीएजी) [[सीरियल वायर डिबग]] मोड में प्रवेश करने और बाहर निकलने के लिए ऐसे अनुक्रमों का उपयोग करते हैं। आईईईई 1149.7 में जीरो बिट स्कैन (जेडबीएस) अनुक्रम का उपयोग किया जाता है<ref name="ieee-1149.7">Texas Instruments is one adopter behind this standard, and has an [http://tiexpressdsp.com/wiki/index.php?title=IEEE_1149.7 IEEE 1149.7 wiki page] {{Webarchive|url=https://web.archive.org/web/20140406214032/http://tiexpressdsp.com/wiki/index.php?title=IEEE_1149.7 |date=6 April 2014 }} with more information.</ref> उन्नत कार्यक्षमता तक पहुँचने के लिए जैसे | अधिकांश जेटीएजी होस्ट दो राज्यों के बीच सबसे छोटे रास्ते का उपयोग करते हैं, शायद एडॉप्टर की विचित्रताओं से विवश। (उदाहरण के लिए, एक एडेप्टर{{Which|date=March 2010}} केवल उन पथों को संभालता है जिनकी लंबाई सात बिट्स के गुणक हैं।) जेटीएजी के शीर्ष पर निर्मित कुछ परतें राज्य के संक्रमणों की निगरानी करती हैं, और उच्च स्तर के संचालन को ट्रिगर करने के लिए असामान्य पथों का उपयोग करती हैं। कुछ एआरएम कोर दो-तार (गैर-जेटीएजी) [[सीरियल वायर डिबग]] मोड में प्रवेश करने और बाहर निकलने के लिए ऐसे अनुक्रमों का उपयोग करते हैं। आईईईई 1149.7 में जीरो बिट स्कैन (जेडबीएस) अनुक्रम का उपयोग किया जाता है<ref name="ieee-1149.7">Texas Instruments is one adopter behind this standard, and has an [http://tiexpressdsp.com/wiki/index.php?title=IEEE_1149.7 IEEE 1149.7 wiki page] {{Webarchive|url=https://web.archive.org/web/20140406214032/http://tiexpressdsp.com/wiki/index.php?title=IEEE_1149.7 |date=6 April 2014 }} with more information.</ref> उन्नत कार्यक्षमता तक पहुँचने के लिए जैसे TAP को स्कैन चेन, पावर प्रबंधन और एक अलग दो-तार मोड में स्विच करना और बाहर करना। | ||

=== जेटीएजी आईईईई Std 1149.1 (सीमा स्कैन) निर्देश === | === जेटीएजी आईईईई Std 1149.1 (सीमा स्कैन) निर्देश === | ||

| Line 119: | Line 119: | ||

* आंतरिक परीक्षण के लिए रुचि, जैसे ऑन-चिप व्यवहार की जांच के लिए पिन का उपयोग करना | * आंतरिक परीक्षण के लिए रुचि, जैसे ऑन-चिप व्यवहार की जांच के लिए पिन का उपयोग करना | ||

* RUNBIST चिप को सेल्फ-टेस्ट मोड में रखता है | * RUNBIST चिप को सेल्फ-टेस्ट मोड में रखता है | ||

* USERCODE उपयोगकर्ता-परिभाषित कोड लौटाता है, उदाहरण के लिए यह पहचानने के लिए कि कौन सी | * USERCODE उपयोगकर्ता-परिभाषित कोड लौटाता है, उदाहरण के लिए यह पहचानने के लिए कि कौन सी एफपीजीए छवि सक्रिय है | ||

उपकरण अधिक निर्देशों को परिभाषित कर सकते हैं, और वे परिभाषाएँ निर्माता द्वारा प्रदान की गई बीएसडीएल फ़ाइल का हिस्सा होनी चाहिए। उन्हें अक्सर केवल निजी के रूप में चिह्नित किया जाता है। | उपकरण अधिक निर्देशों को परिभाषित कर सकते हैं, और वे परिभाषाएँ निर्माता द्वारा प्रदान की गई बीएसडीएल फ़ाइल का हिस्सा होनी चाहिए। उन्हें अक्सर केवल निजी के रूप में चिह्नित किया जाता है। | ||

| Line 146: | Line 146: | ||

इस कोर के लाइसेंसधारी इसे चिप्स में एकीकृत करते हैं, आमतौर पर इसे अन्य टीएपी के साथ-साथ कई बाह्य उपकरणों और मेमोरी के साथ जोड़ते हैं। उन अन्य टीएपी में से एक संपूर्ण चिप के लिए सीमा स्कैन परीक्षण को संभालता है; यह डीबग टीएपी द्वारा समर्थित नहीं है। ऐसे चिप्स के उदाहरणों में शामिल हैं: | इस कोर के लाइसेंसधारी इसे चिप्स में एकीकृत करते हैं, आमतौर पर इसे अन्य टीएपी के साथ-साथ कई बाह्य उपकरणों और मेमोरी के साथ जोड़ते हैं। उन अन्य टीएपी में से एक संपूर्ण चिप के लिए सीमा स्कैन परीक्षण को संभालता है; यह डीबग टीएपी द्वारा समर्थित नहीं है। ऐसे चिप्स के उदाहरणों में शामिल हैं: | ||

[[टेक्सास इंस्ट्रूमेंट्स ओएमएपी]] OMAP, जिसमें सीमा स्कैन TAP, ARM1136 डिबग TAP, ETB11 ट्रेस बफर TAP, [[टेक्सास इंस्ट्रूमेंट्स TMS320]], और [[ARM7]] TDMI-आधारित इमेजिंग इंजन के लिए एक TAP शामिल है, सीमा स्कैन TAP (ICEpick-B) के साथ ) | [[टेक्सास इंस्ट्रूमेंट्स ओएमएपी]] OMAP, जिसमें सीमा स्कैन TAP, ARM1136 डिबग TAP, ETB11 ट्रेस बफर TAP, [[टेक्सास इंस्ट्रूमेंट्स TMS320|टेक्सास इंस्ट्रूमेंट्स टीएमएस320]], और [[ARM7]] TDMI-आधारित इमेजिंग इंजन के लिए एक TAP शामिल है, सीमा स्कैन TAP (ICEpick-B) के साथ ) TAP को जेटीएजी स्कैन श्रृंखला के अंदर और बाहर विभाजित करने की क्षमता रखता है।<ref name="omap2420">Documentation for the OMAP2420 is not publicly available. However, a [[Texas Instruments]] document [http://wiki.davincidsp.com/images/9/90/Dbjtag_users_guide.pdf The User's Guide to DBGJTAG] discussing a JTAG diagnostic tool presents this OMAP2420 scan chain example (and others).</ref> | ||

* i.MX31 प्रोसेसर, जो समान है, हालांकि इसका प्रणाली जेटीएजी बाउंड्री स्कैन TAP है,<ref name="iMX31">See "i.MX35 (MCIMX35) Multimedia Applications Processor Reference Manual" from the [[Freescale]] web site. Chapter 44 presents its "Secure JTAG Controller" (SJC).</ref> जो ICEpick से बहुत अलग है, और इसमें DSP और इमेजिंग इंजन के बजाय इसके DMA इंजन के लिए TAP शामिल है। | * i.MX31 प्रोसेसर, जो समान है, हालांकि इसका प्रणाली जेटीएजी बाउंड्री स्कैन TAP है,<ref name="iMX31">See "i.MX35 (MCIMX35) Multimedia Applications Processor Reference Manual" from the [[Freescale]] web site. Chapter 44 presents its "Secure JTAG Controller" (SJC).</ref> जो ICEpick से बहुत अलग है, और इसमें DSP और इमेजिंग इंजन के बजाय इसके DMA इंजन के लिए TAP शामिल है। | ||

| Line 169: | Line 169: | ||

पुराने ARM7 और ARM9 कोर में एक एंबेडेडिस मॉड्यूल शामिल है<ref name="arm9ejs">[http://infocenter.arm.com/help/topic/com.arm.doc.ddi0222b/DDI0222.pdf ARM9EJ-S Technical Reference Manual] revision r1p2. Appendix B "Debug in Depth" presents the EmbeddedICE-RT module, as seen in the popular ARM926ejs core.</ref> जो उन अधिकांश सुविधाओं को जोड़ती है, लेकिन निर्देश निष्पादन के लिए एक अजीब तंत्र है: डीबगर को सीपीयू निर्देश पाइपलाइन, घड़ी से घड़ी चलाना चाहिए, और सीपीयू को डेटा पढ़ने और लिखने के लिए डेटा बसों तक सीधे पहुंचना चाहिए। ARM11 उन पुराने कोर के समान ट्रेस सपोर्ट (ETM, ETB) के लिए उसी मॉडल का उपयोग करता है। | पुराने ARM7 और ARM9 कोर में एक एंबेडेडिस मॉड्यूल शामिल है<ref name="arm9ejs">[http://infocenter.arm.com/help/topic/com.arm.doc.ddi0222b/DDI0222.pdf ARM9EJ-S Technical Reference Manual] revision r1p2. Appendix B "Debug in Depth" presents the EmbeddedICE-RT module, as seen in the popular ARM926ejs core.</ref> जो उन अधिकांश सुविधाओं को जोड़ती है, लेकिन निर्देश निष्पादन के लिए एक अजीब तंत्र है: डीबगर को सीपीयू निर्देश पाइपलाइन, घड़ी से घड़ी चलाना चाहिए, और सीपीयू को डेटा पढ़ने और लिखने के लिए डेटा बसों तक सीधे पहुंचना चाहिए। ARM11 उन पुराने कोर के समान ट्रेस सपोर्ट (ETM, ETB) के लिए उसी मॉडल का उपयोग करता है। | ||

नए एआरएम कॉर्टेक्स कोर इस डीबग मॉडल के समान दिखते हैं, लेकिन प्रत्यक्ष सीपीयू एक्सेस के बजाय डीबग एक्सेस पोर्ट (डीएपी) पर निर्मित होते हैं। इस आर्किटेक्चर (नाम CoreSight Technology) में, कोर और जेटीएजी मॉड्यूल पूरी तरह से स्वतंत्र हैं। उन्हें जेटीएजी से भी अलग किया जाता है ताकि उन्हें केवल छह-तार जेटीएजी इंटरफ़ेस के बजाय ARM के दो-तार 'SWD' इंटरफ़ेस (नीचे देखें) पर होस्ट किया जा सके। (एआरएम चार मानक जेटीएजी सिग्नल लेता है और वैकल्पिक | नए एआरएम कॉर्टेक्स कोर इस डीबग मॉडल के समान दिखते हैं, लेकिन प्रत्यक्ष सीपीयू एक्सेस के बजाय डीबग एक्सेस पोर्ट (डीएपी) पर निर्मित होते हैं। इस आर्किटेक्चर (नाम CoreSight Technology) में, कोर और जेटीएजी मॉड्यूल पूरी तरह से स्वतंत्र हैं। उन्हें जेटीएजी से भी अलग किया जाता है ताकि उन्हें केवल छह-तार जेटीएजी इंटरफ़ेस के बजाय ARM के दो-तार 'SWD' इंटरफ़ेस (नीचे देखें) पर होस्ट किया जा सके। (एआरएम चार मानक जेटीएजी सिग्नल लेता है और वैकल्पिक टीआरएसटी जोड़ता है, साथ ही अनुकूली क्लॉकिंग के लिए उपयोग किया जाने वाला आरटीकेके सिग्नल।) CoreSight जेटीएजी-DP कोर घड़ियों के लिए अतुल्यकालिक है, और आरटीकेके को प्रायुक्त नहीं करता है।<ref>{{cite web|url=http://infocenter.arm.com/help/topic/com.arm.doc.ddi0314h/Chdhbbjd.html#Chdihede|title=CoreSight Components Technical Reference Manual: 2.3.2. Implementation specific details|website=infocenter.arm.com}}</ref> साथ ही, नए कोर ने ट्रेस सपोर्ट को अपडेट किया है। | ||

=== हॉल्ट मोड डिबगिंग === | === हॉल्ट मोड डिबगिंग === | ||

सॉफ़्टवेयर डिबग करने का एक मूल तरीका एकल थ्रेडेड मॉडल प्रस्तुत करना है, जहां डीबगर समय-समय पर प्रोग्राम के निष्पादन को रोकता है और रजिस्टर सामग्री और मेमोरी (परिधीय नियंत्रक रजिस्टरों सहित) द्वारा उजागर की गई स्थिति की जांच करता है। जब दिलचस्प कार्यक्रम की घटनाएँ सामने आती हैं, तो एक व्यक्ति एक विशेष दुर्व्यवहार कैसे होता है, यह देखने के लिए एकल चरण निर्देश (या स्रोत कोड की पंक्तियाँ) लेना चाहता है। | सॉफ़्टवेयर डिबग करने का एक मूल तरीका एकल थ्रेडेड मॉडल प्रस्तुत करना है, जहां डीबगर समय-समय पर प्रोग्राम के निष्पादन को रोकता है और रजिस्टर सामग्री और मेमोरी (परिधीय नियंत्रक रजिस्टरों सहित) द्वारा उजागर की गई स्थिति की जांच करता है। जब दिलचस्प कार्यक्रम की घटनाएँ सामने आती हैं, तो एक व्यक्ति एक विशेष दुर्व्यवहार कैसे होता है, यह देखने के लिए एकल चरण निर्देश (या स्रोत कोड की पंक्तियाँ) लेना चाहता है। | ||

तो उदाहरण के लिए एक जेटीएजी होस्ट कोर को रोक सकता है, डिबग मोड में प्रवेश कर सकता है, और फिर ITR और DCC का उपयोग करके सीपीयू रजिस्टर पढ़ सकता है। प्रोसेसर स्थिति को सहेजने के बाद, यह उन रजिस्टरों को किसी भी मूल्य के साथ लिख सकता है, फिर सीपीयू पर मनमाने | तो उदाहरण के लिए एक जेटीएजी होस्ट कोर को रोक सकता है, डिबग मोड में प्रवेश कर सकता है, और फिर ITR और DCC का उपयोग करके सीपीयू रजिस्टर पढ़ सकता है। प्रोसेसर स्थिति को सहेजने के बाद, यह उन रजिस्टरों को किसी भी मूल्य के साथ लिख सकता है, फिर सीपीयू पर मनमाने विधि से एल्गोरिदम निष्पादित कर सकता है, प्रणाली स्थिति को चित्रित करने में सहायता के लिए स्मृति और बाह्य उपकरणों तक पहुंच सकता है। डिबगर द्वारा उन कार्यों को करने के बाद, राज्य को पुनर्स्थापित किया जा सकता है और RESTART निर्देश का उपयोग करके निष्पादन जारी रखा जा सकता है। | ||

डिबग मोड को अतुल्यकालिक रूप से डिबग मॉड्यूल द्वारा वॉचपॉइंट या ब्रेकपॉइंट को ट्रिगर करके, या डीबग किए जा रहे सॉफ़्टवेयर से बीकेपीटी (ब्रेकपॉइंट) निर्देश जारी करके भी दर्ज किया जाता है। जब इसका उपयोग निर्देश अनुरेखण के लिए नहीं किया जा रहा है, तो ETM डिबग मोड में प्रवेश को भी ट्रिगर कर सकता है; यह राज्य और इतिहास के प्रति संवेदनशील जटिल ट्रिगर्स का समर्थन करता है, साथ ही डिबग मॉड्यूल द्वारा उजागर की गई सरल पता तुलनाओं का भी समर्थन करता है। डिबग मोड में एसिंक्रोनस ट्रांज़िशन DSCR रजिस्टर पोलिंग द्वारा पता लगाया जाता है। इस तरह सिंगल स्टेपिंग को प्रायुक्त किया जाता है: कोर को रोकें, अगले निर्देश या अगले उच्च-स्तरीय स्टेटमेंट पर एक अस्थायी ब्रेकपॉइंट सेट करें, RESTART, पोल DSCR जब तक आप डिबग स्टेट में एसिंक्रोनस एंट्री का पता नहीं लगाते हैं, उस अस्थायी ब्रेकपॉइंट को हटा दें, दोहराएं। | डिबग मोड को अतुल्यकालिक रूप से डिबग मॉड्यूल द्वारा वॉचपॉइंट या ब्रेकपॉइंट को ट्रिगर करके, या डीबग किए जा रहे सॉफ़्टवेयर से बीकेपीटी (ब्रेकपॉइंट) निर्देश जारी करके भी दर्ज किया जाता है। जब इसका उपयोग निर्देश अनुरेखण के लिए नहीं किया जा रहा है, तो ETM डिबग मोड में प्रवेश को भी ट्रिगर कर सकता है; यह राज्य और इतिहास के प्रति संवेदनशील जटिल ट्रिगर्स का समर्थन करता है, साथ ही डिबग मॉड्यूल द्वारा उजागर की गई सरल पता तुलनाओं का भी समर्थन करता है। डिबग मोड में एसिंक्रोनस ट्रांज़िशन DSCR रजिस्टर पोलिंग द्वारा पता लगाया जाता है। इस तरह सिंगल स्टेपिंग को प्रायुक्त किया जाता है: कोर को रोकें, अगले निर्देश या अगले उच्च-स्तरीय स्टेटमेंट पर एक अस्थायी ब्रेकपॉइंट सेट करें, RESTART, पोल DSCR जब तक आप डिबग स्टेट में एसिंक्रोनस एंट्री का पता नहीं लगाते हैं, उस अस्थायी ब्रेकपॉइंट को हटा दें, दोहराएं। | ||

| Line 196: | Line 196: | ||

** [[एमआईपीएस आर्किटेक्चर]] प्रोसेसर जेटीएजी सपोर्ट के साथ आते हैं, कभी-कभी टू-वायर SWD वैरिएंट या इंस्ट्रक्शन या डेटा बसों पर ट्रैफिक की हाई स्पीड ट्रेसिंग को सपोर्ट करते हैं। | ** [[एमआईपीएस आर्किटेक्चर]] प्रोसेसर जेटीएजी सपोर्ट के साथ आते हैं, कभी-कभी टू-वायर SWD वैरिएंट या इंस्ट्रक्शन या डेटा बसों पर ट्रैफिक की हाई स्पीड ट्रेसिंग को सपोर्ट करते हैं। | ||

** आधुनिक 8-बिट और 16-बिट [[ microcontroller ]] चिप्स, जैसे [[Atmel AVR]] और [[TI MSP430]] चिप्स, जेटीएजी प्रोग्रामिंग और डिबगिंग का समर्थन करते हैं। हालांकि, सबसे छोटे चिप्स में अतिरिक्त पिन नहीं हो सकते हैं (और इस प्रकार मालिकाना सिंगल-वायर प्रोग्रामिंग इंटरफेस पर भरोसा करते हैं); यदि पिन की संख्या 32 से अधिक है, तो संभवतः एक जेटीएजी विकल्प है। | ** आधुनिक 8-बिट और 16-बिट [[ microcontroller ]] चिप्स, जैसे [[Atmel AVR]] और [[TI MSP430]] चिप्स, जेटीएजी प्रोग्रामिंग और डिबगिंग का समर्थन करते हैं। हालांकि, सबसे छोटे चिप्स में अतिरिक्त पिन नहीं हो सकते हैं (और इस प्रकार मालिकाना सिंगल-वायर प्रोग्रामिंग इंटरफेस पर भरोसा करते हैं); यदि पिन की संख्या 32 से अधिक है, तो संभवतः एक जेटीएजी विकल्प है। | ||

** आज उपयोग किए जाने वाले लगभग सभी | ** आज उपयोग किए जाने वाले लगभग सभी एफपीजीए और [[CPLD]] को जेटीएजी पोर्ट के माध्यम से प्रोग्राम किया जा सकता है। PLD की जेटीएजी प्रोग्रामिंग के लिए JEDEC मानक JESD-71 द्वारा एक [[मानक परीक्षण और प्रोग्रामिंग भाषा]] परिभाषित की गई है। | ||

** कई MIPS आर्किटेक्चर और [[PowerPC]] प्रोसेसर में जेटीएजी सपोर्ट है | ** कई MIPS आर्किटेक्चर और [[PowerPC]] प्रोसेसर में जेटीएजी सपोर्ट है | ||

** Intel Core, Xeon, Atom, और Quark प्रोसेसर सभी जेटीएजी जांच मोड का समर्थन करते हैं, तथाकथित 60-पिन एक्सटेंडेड डिबग पोर्ट [XDP] का उपयोग करके जेटीएजी के Intel विशिष्ट एक्सटेंशन के साथ। इसके अतिरिक्त क्वार्क प्रोसेसर अधिक पारंपरिक 10-पिन कनेक्टर्स का समर्थन करता है। | ** Intel Core, Xeon, Atom, और Quark प्रोसेसर सभी जेटीएजी जांच मोड का समर्थन करते हैं, तथाकथित 60-पिन एक्सटेंडेड डिबग पोर्ट [XDP] का उपयोग करके जेटीएजी के Intel विशिष्ट एक्सटेंशन के साथ। इसके अतिरिक्त क्वार्क प्रोसेसर अधिक पारंपरिक 10-पिन कनेक्टर्स का समर्थन करता है। | ||

**उपभोक्ता उत्पाद जैसे नेटवर्किंग उपकरण और उपग्रह टेलीविजन एकीकृत रिसीवर/डिकोडर अक्सर माइक्रोप्रोसेसर का उपयोग करते हैं जो जेटीएजी का समर्थन करते हैं, फ़र्मवेयर को फिर से लोड करने का वैकल्पिक साधन प्रदान करते हैं यदि मौजूदा [[बूटलोडर]] किसी तरह से दूषित हो गया है। | **उपभोक्ता उत्पाद जैसे नेटवर्किंग उपकरण और उपग्रह टेलीविजन एकीकृत रिसीवर/डिकोडर अक्सर माइक्रोप्रोसेसर का उपयोग करते हैं जो जेटीएजी का समर्थन करते हैं, फ़र्मवेयर को फिर से लोड करने का वैकल्पिक साधन प्रदान करते हैं यदि मौजूदा [[बूटलोडर]] किसी तरह से दूषित हो गया है। | ||

*[[ पेरिफ़ेरल कंपोनेंट इंटरकनेक्ट ]] बस कनेक्टर मानक में पिन 1-5 पर वैकल्पिक जेटीएजी सिग्नल होते हैं;<ref>{{cite web|url=http://www.techfest.com/hardware/bus/pci.htm#4.10|title=PCI Local Bus Technical Summary, 4.10 JTAG/Boundary Scan Pins|access-date=13 July 2007|archive-url=https://web.archive.org/web/20061107201536/http://www.techfest.com/hardware/bus/pci.htm#4.10|archive-date=7 November 2006|url-status=dead}}</ref> [[PCI Express]] में 5-9 पिनों पर जेटीएजी सिग्नल होते हैं।<ref>{{cite web|url=http://www.interfacebus.com/Design_PCI_Express_16x_PinOut.html|title=Serial PCI Express Bus 16x Pinout and PCIe Pin out Signal names|website=www.interfacebus.com}}</ref> एक भ्रष्ट [[BIOS]] को रिफ़्लेश करने के लिए एक विशेष जेटीएजी कार्ड का उपयोग किया जा सकता है। | *[[ पेरिफ़ेरल कंपोनेंट इंटरकनेक्ट ]] बस कनेक्टर मानक में पिन 1-5 पर वैकल्पिक जेटीएजी सिग्नल होते हैं;<ref>{{cite web|url=http://www.techfest.com/hardware/bus/pci.htm#4.10|title=PCI Local Bus Technical Summary, 4.10 JTAG/Boundary Scan Pins|access-date=13 July 2007|archive-url=https://web.archive.org/web/20061107201536/http://www.techfest.com/hardware/bus/pci.htm#4.10|archive-date=7 November 2006|url-status=dead}}</ref> [[PCI Express]] में 5-9 पिनों पर जेटीएजी सिग्नल होते हैं।<ref>{{cite web|url=http://www.interfacebus.com/Design_PCI_Express_16x_PinOut.html|title=Serial PCI Express Bus 16x Pinout and PCIe Pin out Signal names|website=www.interfacebus.com}}</ref> एक भ्रष्ट [[BIOS]] को रिफ़्लेश करने के लिए एक विशेष जेटीएजी कार्ड का उपयोग किया जा सकता है। | ||

* बाउंड्री स्कैन टेस्टिंग और इन-प्रणाली (डिवाइस) प्रोग्रामिंग एप्लिकेशन को कभी-कभी सीरियल वेक्टर फॉर्मेट का उपयोग करके प्रोग्राम किया जाता है, जो एक साधारण सिंटैक्स का उपयोग करके जेटीएजी संचालन का एक शाब्दिक प्रतिनिधित्व है। अन्य प्रोग्रामिंग प्रारूपों में 'JAM' और STAPL और हाल ही में आईईईई Std शामिल हैं। 1532 परिभाषित प्रारूप 'आईएससी' (इन-प्रणाली कॉन्फ़िगरेशन के लिए संक्षिप्त)। ISC प्रारूप का उपयोग प्रोग्रामेबल लॉजिक डिवाइसेस (यानी | * बाउंड्री स्कैन टेस्टिंग और इन-प्रणाली (डिवाइस) प्रोग्रामिंग एप्लिकेशन को कभी-कभी सीरियल वेक्टर फॉर्मेट का उपयोग करके प्रोग्राम किया जाता है, जो एक साधारण सिंटैक्स का उपयोग करके जेटीएजी संचालन का एक शाब्दिक प्रतिनिधित्व है। अन्य प्रोग्रामिंग प्रारूपों में 'JAM' और STAPL और हाल ही में आईईईई Std शामिल हैं। 1532 परिभाषित प्रारूप 'आईएससी' (इन-प्रणाली कॉन्फ़िगरेशन के लिए संक्षिप्त)। ISC प्रारूप का उपयोग प्रोग्रामेबल लॉजिक डिवाइसेस (यानी एफपीजीए और CPLDs) के लिए उन्नत BSDL मॉडल के संयोजन में किया जाता है जिसमें बुनियादी न्यूनतम आईईईई 1149.1 निर्देशों के अलावा अतिरिक्त ISC_<ऑपरेशन> निर्देश शामिल होते हैं। [[Xilinx]], Altera, Lattice, Cypress, Actel, आदि से एफपीजीए प्रोग्रामिंग टूल आमतौर पर ऐसी फ़ाइलों को निर्यात करने में सक्षम होते हैं। | ||

* जैसा कि उल्लेख किया गया है, कई बोर्डों में विनिर्माण कार्यों का समर्थन करने के लिए जेटीएजी कनेक्टर, या सिर्फ पैड शामिल हैं, जहां सीमा स्कैन परीक्षण बोर्ड की गुणवत्ता (खराब मिलाप जोड़ों की पहचान, आदि) को सत्यापित करने और फ्लैश मेमोरी या | * जैसा कि उल्लेख किया गया है, कई बोर्डों में विनिर्माण कार्यों का समर्थन करने के लिए जेटीएजी कनेक्टर, या सिर्फ पैड शामिल हैं, जहां सीमा स्कैन परीक्षण बोर्ड की गुणवत्ता (खराब मिलाप जोड़ों की पहचान, आदि) को सत्यापित करने और फ्लैश मेमोरी या एफपीजीए को आरंभ करने में मदद करता है। | ||

* जेटीएजी फील्ड अपडेट और समस्या निवारण का भी समर्थन कर सकता है। | * जेटीएजी फील्ड अपडेट और समस्या निवारण का भी समर्थन कर सकता है। | ||

| Line 217: | Line 217: | ||

* MIPS Eजेटीएजी (2 × 7 पिन) MIPS टेक्नोलॉजीज आधारित प्रणाली के लिए उपयोग किया जाता है | * MIPS Eजेटीएजी (2 × 7 पिन) MIPS टेक्नोलॉजीज आधारित प्रणाली के लिए उपयोग किया जाता है | ||

* 2 × 5 पिन [[Altera]] ByteBlaster- संगत जेटीएजी कई विक्रेताओं द्वारा विस्तारित | * 2 × 5 पिन [[Altera]] ByteBlaster- संगत जेटीएजी कई विक्रेताओं द्वारा विस्तारित | ||

* 2 × 5 पिन Atmel AVR | * 2 × 5 पिन Atmel AVR एसआरएसटी के साथ Altera जेटीएजी का विस्तार करता है (और कुछ मामलों में टीआरएसटी और एक इवेंट आउटपुट) | ||

* 2 × 7 पिन [[ टेक्सस उपकरण ]] टेक्सास इंस्ट्रूमेंट्स टीएमएस320 और [[ओएमएपी]] जैसे एआरएम-आधारित उत्पादों के साथ प्रयोग किया जाता है | * 2 × 7 पिन [[ टेक्सस उपकरण ]] टेक्सास इंस्ट्रूमेंट्स टीएमएस320 और [[ओएमएपी]] जैसे एआरएम-आधारित उत्पादों के साथ प्रयोग किया जाता है | ||

* 8 पिन (एकल पंक्ति) जेनेरिक PLD जेटीएजी कई जाली ispDOWNLOAD केबलों के साथ संगत | * 8 पिन (एकल पंक्ति) जेनेरिक PLD जेटीएजी कई जाली ispDOWNLOAD केबलों के साथ संगत | ||

* [[MIPI डिबग आर्किटेक्चर]]10-/20-कनेक्टर्स (1.27 mm 050 ) जेटीएजी, cजेटीएजी और SWD के लिए | * [[MIPI डिबग आर्किटेक्चर]]10-/20-कनेक्टर्स (1.27 mm 050 ) जेटीएजी, cजेटीएजी और SWD के लिए | ||

उन कनेक्टर्स में केवल चार मानकीकृत सिग्नल ( | उन कनेक्टर्स में केवल चार मानकीकृत सिग्नल (टीएमएस, टीकेके, टीडीआई, TDO) से अधिक शामिल होते हैं। आमतौर पर रीसेट सिग्नल प्रदान किए जाते हैं, टीआरएसटी (TAP रीसेट) और एसआरएसटी (प्रणाली रीसेट) में से एक या दोनों। कनेक्टर आमतौर पर बोर्ड-अंडर-टेस्ट का लॉजिक सप्लाई वोल्टेज प्रदान करता है ताकि जेटीएजी एडेप्टर उपयुक्त लॉजिक स्तरों का उपयोग करें<!-- eg 5, 3.3, ..., 1V, ... -->. बोर्ड वोल्टेज बोर्ड के वर्तमान डिबगर इनपुट के रूप में भी काम कर सकता है। अधिक जटिल डिबगिंग आर्किटेक्चर का समर्थन करने के लिए अन्य ईवेंट इनपुट या आउटपुट सिग्नल प्रदान किए जा सकते हैं, या सामान्य प्रयोजन इनपुट/आउटपुट | सामान्य प्रयोजन I/O (GPIO) लाइनें। | ||

जेटीएजी संचालन के संयोजन के साथ हाई-स्पीड [[ अनुरेखण (सॉफ्टवेयर) ]] का समर्थन करने के लिए उच्च अंत उत्पाद अक्सर घने कनेक्टर (अक्सर 38-पिन [[MICTOR]] कनेक्टर) का उपयोग करते हैं। एक हालिया चलन है कि विकास बोर्ड जेटीएजी में एक | जेटीएजी संचालन के संयोजन के साथ हाई-स्पीड [[ अनुरेखण (सॉफ्टवेयर) ]] का समर्थन करने के लिए उच्च अंत उत्पाद अक्सर घने कनेक्टर (अक्सर 38-पिन [[MICTOR]] कनेक्टर) का उपयोग करते हैं। एक हालिया चलन है कि विकास बोर्ड जेटीएजी में एक यूएसबी इंटरफ़ेस को एकीकृत करते हैं, जहाँ एक सीरियल पोर्ट के लिए एक दूसरे चैनल का उपयोग किया जाता है। (छोटे बोर्ड यूएसबी के माध्यम से भी संचालित किए जा सकते हैं। चूंकि आधुनिक पीसी सीरियल पोर्ट को छोड़ देते हैं, ऐसे एकीकृत डिबग लिंक विकासकर्ता के लिए अव्यवस्था को काफी कम कर सकते हैं।) प्रोडक्शन बोर्ड अक्सर [[नाखून परीक्षक का बिस्तर]] पर भरोसा करते हैं। परीक्षण बिंदुओं के लिए बेड-ऑफ-नेल संयोजन परीक्षण और प्रोग्रामिंग के लिए। | ||

=== एडेप्टर हार्डवेयर === | === एडेप्टर हार्डवेयर === | ||

एडेप्टर हार्डवेयर व्यापक रूप से भिन्न होता है। जब विकास बोर्ड में एकीकृत नहीं किया जाता है, तो लक्ष्य बोर्ड पर जेटीएजी कनेक्टर से जुड़ने के लिए इसमें एक छोटी केबल शामिल होती है; डिबगिंग होस्ट से संयोजन, जैसे यूएसबी, पीसीआई, या ईथरनेट लिंक; और दो संचार डोमेन को अनुकूलित करने के लिए पर्याप्त इलेक्ट्रॉनिक्स (और कभी-कभी गैल्वेनिक अलगाव प्रदान करते हैं)। एक अलग बिजली आपूर्ति की आवश्यकता हो सकती है। दोनों गूंगे एडेप्टर हैं, जहां मेजबान सभी जेटीएजी संचालन का निर्णय लेता है और करता है; और स्मार्ट वाले, जहां उस काम में से कुछ एडॉप्टर के अंदर किया जाता है, अक्सर एक माइक्रोकंट्रोलर द्वारा संचालित होता है। स्मार्ट एडेप्टर ऑपरेशन अनुक्रमों के लिए लिंक विलंबता को समाप्त करते हैं जिसमें चरणों के बीच स्थिति परिवर्तन के लिए मतदान शामिल हो सकता है, और तदनुसार तेजी से थ्रूपुट की पेशकश कर सकता है। | एडेप्टर हार्डवेयर व्यापक रूप से भिन्न होता है। जब विकास बोर्ड में एकीकृत नहीं किया जाता है, तो लक्ष्य बोर्ड पर जेटीएजी कनेक्टर से जुड़ने के लिए इसमें एक छोटी केबल शामिल होती है; डिबगिंग होस्ट से संयोजन, जैसे यूएसबी, पीसीआई, या ईथरनेट लिंक; और दो संचार डोमेन को अनुकूलित करने के लिए पर्याप्त इलेक्ट्रॉनिक्स (और कभी-कभी गैल्वेनिक अलगाव प्रदान करते हैं)। एक अलग बिजली आपूर्ति की आवश्यकता हो सकती है। दोनों गूंगे एडेप्टर हैं, जहां मेजबान सभी जेटीएजी संचालन का निर्णय लेता है और करता है; और स्मार्ट वाले, जहां उस काम में से कुछ एडॉप्टर के अंदर किया जाता है, अक्सर एक माइक्रोकंट्रोलर द्वारा संचालित होता है। स्मार्ट एडेप्टर ऑपरेशन अनुक्रमों के लिए लिंक विलंबता को समाप्त करते हैं जिसमें चरणों के बीच स्थिति परिवर्तन के लिए मतदान शामिल हो सकता है, और तदनुसार तेजी से थ्रूपुट की पेशकश कर सकता है। | ||

{{As of|2018}}, होस्ट से [[USB]] लिंक वाले एडेप्टर सबसे आम दृष्टिकोण हैं। उच्च अंत उत्पाद अक्सर [[ईथरनेट]] का समर्थन करते हैं, इस लाभ के साथ कि डीबग होस्ट काफी दूरस्थ हो सकता है। एडेप्टर जो हाई स्पीड ट्रेस पोर्ट का समर्थन करते हैं, उनमें आमतौर पर कई मेगाबाइट ट्रेस बफर शामिल होते हैं और उस डेटा को होस्ट तक पहुंचाने के लिए हाई स्पीड लिंक ( | {{As of|2018}}, होस्ट से [[USB|यूएसबी]] लिंक वाले एडेप्टर सबसे आम दृष्टिकोण हैं। उच्च अंत उत्पाद अक्सर [[ईथरनेट]] का समर्थन करते हैं, इस लाभ के साथ कि डीबग होस्ट काफी दूरस्थ हो सकता है। एडेप्टर जो हाई स्पीड ट्रेस पोर्ट का समर्थन करते हैं, उनमें आमतौर पर कई मेगाबाइट ट्रेस बफर शामिल होते हैं और उस डेटा को होस्ट तक पहुंचाने के लिए हाई स्पीड लिंक (यूएसबी या ईथरनेट) प्रदान करते हैं। | ||

समानांतर पोर्ट एडेप्टर सरल और सस्ते हैं, लेकिन वे अपेक्षाकृत धीमे हैं क्योंकि वे प्रत्येक बिट ([[ थोड़ा पीटना ]]) को बदलने के लिए होस्ट सीपीयू का उपयोग करते हैं। उनकी उपयोगिता में गिरावट आई है क्योंकि हाल के वर्षों में अधिकांश कंप्यूटरों में समानांतर पोर्ट नहीं है। ड्राइवर समर्थन भी एक समस्या है, क्योंकि एडेप्टर द्वारा पिन उपयोग व्यापक रूप से भिन्न होता है। चूंकि समांतर बंदरगाह 5V तर्क स्तर पर आधारित है, इसलिए अधिकांश एडाप्टरों में 3.3V या 1.8V लक्ष्य वोल्टेज के लिए वोल्टेज अनुवाद समर्थन की कमी है। | समानांतर पोर्ट एडेप्टर सरल और सस्ते हैं, लेकिन वे अपेक्षाकृत धीमे हैं क्योंकि वे प्रत्येक बिट ([[ थोड़ा पीटना ]]) को बदलने के लिए होस्ट सीपीयू का उपयोग करते हैं। उनकी उपयोगिता में गिरावट आई है क्योंकि हाल के वर्षों में अधिकांश कंप्यूटरों में समानांतर पोर्ट नहीं है। ड्राइवर समर्थन भी एक समस्या है, क्योंकि एडेप्टर द्वारा पिन उपयोग व्यापक रूप से भिन्न होता है। चूंकि समांतर बंदरगाह 5V तर्क स्तर पर आधारित है, इसलिए अधिकांश एडाप्टरों में 3.3V या 1.8V लक्ष्य वोल्टेज के लिए वोल्टेज अनुवाद समर्थन की कमी है। | ||

| Line 240: | Line 240: | ||

एम्बेडेड सॉफ़्टवेयर के लिए अधिकांश विकास परिवेशों में जेटीएजी समर्थन शामिल है। मोटे तौर पर ऐसे सॉफ्टवेयर के तीन स्रोत हैं: | एम्बेडेड सॉफ़्टवेयर के लिए अधिकांश विकास परिवेशों में जेटीएजी समर्थन शामिल है। मोटे तौर पर ऐसे सॉफ्टवेयर के तीन स्रोत हैं: | ||

* चिप विक्रेता उपकरण प्रदान कर सकते हैं, आमतौर पर उनके द्वारा आपूर्ति किए जाने वाले जेटीएजी एडॉप्टर की आवश्यकता होती है। उदाहरणों में | * चिप विक्रेता उपकरण प्रदान कर सकते हैं, आमतौर पर उनके द्वारा आपूर्ति किए जाने वाले जेटीएजी एडॉप्टर की आवश्यकता होती है। उदाहरणों में एफपीजीए विक्रेता जैसे Xilinx और Altera, Atmel अपने AVR8 और AVR32 उत्पाद लाइनों के लिए, और टेक्सास इंस्ट्रूमेंट्स अपने अधिकांश DSP और सूक्ष्म उत्पादों के लिए शामिल हैं। इस तरह के उपकरण अत्यधिक विशिष्ट होते हैं, और एफपीजीए और DSPs जैसे अत्यधिक विशिष्ट चिप्स के लिए एकमात्र वास्तविक विकल्प हो सकते हैं। निचले स्तर के सॉफ्टवेयर उपकरण नि:शुल्क प्रदान किए जा सकते हैं। जेटीएजी एडेप्टर स्वयं मुक्त नहीं हैं, हालांकि कभी-कभी उन्हें विकास बोर्डों के साथ बंडल किया जाता है। | ||

* उपकरण विक्रेता उन्हें आपूर्ति कर सकते हैं, आमतौर पर क्रॉस-प्लेटफ़ॉर्म विकास सहायता प्रदान करने के लिए कई चिप विक्रेताओं के साथ मिलकर। एआरएम आर्किटेक्चर-आधारित उत्पादों में विशेष रूप से समृद्ध तृतीय पक्ष बाजार है, और उनमें से कई विक्रेताओं ने एमआईपीएस आर्किटेक्चर और पावरपीसी जैसे गैर-एआरएम प्लेटफॉर्मों तक विस्तार किया है। टूल विक्रेता कभी-कभी [[जीएनयू संकलक संग्रह]] और [[जीएनयू डीबगर]] जैसे मुफ्त सॉफ्टवेयर के आसपास उत्पादों का निर्माण करते हैं, जीयूआई समर्थन के साथ अक्सर एक्लिप्स (सॉफ्टवेयर) का उपयोग करते हैं। जेटीएजी एडेप्टर कभी-कभी समर्थन बंडलों के साथ बेचे जाते हैं। | * उपकरण विक्रेता उन्हें आपूर्ति कर सकते हैं, आमतौर पर क्रॉस-प्लेटफ़ॉर्म विकास सहायता प्रदान करने के लिए कई चिप विक्रेताओं के साथ मिलकर। एआरएम आर्किटेक्चर-आधारित उत्पादों में विशेष रूप से समृद्ध तृतीय पक्ष बाजार है, और उनमें से कई विक्रेताओं ने एमआईपीएस आर्किटेक्चर और पावरपीसी जैसे गैर-एआरएम प्लेटफॉर्मों तक विस्तार किया है। टूल विक्रेता कभी-कभी [[जीएनयू संकलक संग्रह]] और [[जीएनयू डीबगर]] जैसे मुफ्त सॉफ्टवेयर के आसपास उत्पादों का निर्माण करते हैं, जीयूआई समर्थन के साथ अक्सर एक्लिप्स (सॉफ्टवेयर) का उपयोग करते हैं। जेटीएजी एडेप्टर कभी-कभी समर्थन बंडलों के साथ बेचे जाते हैं। | ||

* ओपन सोर्स टूल्स मौजूद हैं। जैसा कि ऊपर उल्लेख किया गया है, जीसीसी और जीडीबी एक अच्छे टूलचैन के मूल हैं, और उनका समर्थन करने के लिए जीयूआई वातावरण हैं। | * ओपन सोर्स टूल्स मौजूद हैं। जैसा कि ऊपर उल्लेख किया गया है, जीसीसी और जीडीबी एक अच्छे टूलचैन के मूल हैं, और उनका समर्थन करने के लिए जीयूआई वातावरण हैं। | ||

| Line 249: | Line 249: | ||

== समान इंटरफ़ेस मानक == | == समान इंटरफ़ेस मानक == | ||

सीरियल वायर डिबग (SWD) एक वैकल्पिक 2-पिन इलेक्ट्रिकल इंटरफ़ेस है जो समान प्रोटोकॉल का उपयोग करता है। यह मौजूदा जीएनडी संयोजन का उपयोग करता है। SWD ARM डिबग इंटरफ़ेस v5 में परिभाषित ARM सीपीयू मानक द्वि-दिशात्मक वायर प्रोटोकॉल का उपयोग करता है।<ref>{{Cite web|url=http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ihi0031c/index.html|title=एआरएम सूचना केंद्र|website=infocenter.arm.com|access-date=2017-08-10}}</ref> यह डिबगर को प्रणाली मेमोरी और परिधीय या डिबग रजिस्टरों तक पहुंच के लिए एक और [[उन्नत माइक्रोकंट्रोलर बस आर्किटेक्चर]] बस मास्टर बनने में सक्षम बनाता है। डेटा दर तक है {{nowrap|4 MB/s}} {{nowrap|at 50 MHz}}. SWD में बिल्ट-इन एरर डिटेक्शन भी है। SWD क्षमता वाले जेटीएजी उपकरणों पर, | सीरियल वायर डिबग (SWD) एक वैकल्पिक 2-पिन इलेक्ट्रिकल इंटरफ़ेस है जो समान प्रोटोकॉल का उपयोग करता है। यह मौजूदा जीएनडी संयोजन का उपयोग करता है। SWD ARM डिबग इंटरफ़ेस v5 में परिभाषित ARM सीपीयू मानक द्वि-दिशात्मक वायर प्रोटोकॉल का उपयोग करता है।<ref>{{Cite web|url=http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ihi0031c/index.html|title=एआरएम सूचना केंद्र|website=infocenter.arm.com|access-date=2017-08-10}}</ref> यह डिबगर को प्रणाली मेमोरी और परिधीय या डिबग रजिस्टरों तक पहुंच के लिए एक और [[उन्नत माइक्रोकंट्रोलर बस आर्किटेक्चर]] बस मास्टर बनने में सक्षम बनाता है। डेटा दर तक है {{nowrap|4 MB/s}} {{nowrap|at 50 MHz}}. SWD में बिल्ट-इन एरर डिटेक्शन भी है। SWD क्षमता वाले जेटीएजी उपकरणों पर, टीएमएस और टीकेके का उपयोग SWDIO और SWCLK संकेतों के रूप में किया जाता है, जो दोहरे मोड वाले प्रोग्रामर प्रदान करते हैं। | ||

== यह भी देखें == | == यह भी देखें == | ||

Revision as of 14:46, 10 March 2023

जेटीएजी (जॉइंट टेस्ट एक्शन ग्रुप के नाम पर रखा गया है जिसने इसे संहिताबद्ध किया है) निर्माण के बाद मुद्रित सर्किट बोर्डों के डिजाइन और परीक्षण के सत्यापन के लिए एक प्रौद्योगिक मानक है।

जेटीएजी तर्क अनुकरण के पूरक उपकरण के रूप में इलेक्ट्रॉनिक डिजाइन स्वचालन (ईडीए) में ऑन-चिप उपकरण के लिए मानकों को प्रायुक्त करता है।[1] यह प्रणाली एड्रेस और डेटा बसों के लिए सीधे बाहरी एक्सेस की आवश्यकता के बिना लो-ओवरहेड एक्सेस के लिए धारावाहिक संचार इंटरफेस को प्रायुक्त करने वाले एक समर्पित डिबग पोर्ट के उपयोग को निर्दिष्ट करता है। इंटरफ़ेस एक ऑन-चिप टेस्ट एक्सेस पोर्ट (टीएपी) से जुड़ता है जो परीक्षण रजिस्टरों के एक सेट तक पहुंचने के लिए एक राज्य (कंप्यूटर विज्ञान) प्रोटोकॉल को प्रायुक्त करता है जो चिप तर्क स्तर और विभिन्न भागों की डिवाइस क्षमताओं को प्रस्तुत करता है।

निर्माण के बाद मुद्रित सर्किट बोर्डों के डिजाइन और परीक्षण की पुष्टि करने की एक विधि विकसित करने के लिए 1985 में ज्वाइंट टेस्ट एक्शन ग्रुप का गठन किया गया। 1990 में इंस्टीट्यूट ऑफ़ इलेक्ट्रिकल एंड इलेक्ट्रॉनिक्स इंजीनियर्स ने प्रयास के परिणामों को आईईईई मानक 1149.1-1990 में संहिताबद्ध किया, जिसका शीर्षक मानक टेस्ट एक्सेस पोर्ट और सीमा-स्कैन आर्किटेक्चर था।

जेटीएजी मानकों को कई सेमीकंडक्टर चिप निर्माताओं द्वारा विक्रेता-विशिष्ट सुविधाएँ प्रदान करने के लिए विशेष प्रकार के साथ बढ़ाया गया है।[2]

इतिहास

1980 के दशक में, बॉल ग्रिड ऐरे और इसी तरह की माउंटिंग तकनीकों का उपयोग करने वाले मल्टी-लेयर सर्किट बोर्ड और एकीकृत परिपथ (आईसीएस) मानक बन रहे थे, और आईसी के बीच संयोजन बनाए जा रहे थे जो जांच के लिए उपलब्ध नहीं थे। सर्किट बोर्डों में अधिकांश विनिर्माण और फील्ड दोष बोर्डों पर खराब मिलाप जोड़ों, बोर्ड संयोजनों के बीच की खामियों, या आईसी पैड से लीड फ्रेम को पिन करने के लिए बांड और बांड तारों के कारण थे। ज्वाइंट टेस्ट एक्शन ग्रुप (जेटीएजी) का गठन 1985 में एक आईसी पैड से दूसरे में पिन-आउट दृश्य प्रदान करने के लिए किया गया था ताकि इन दोषों का पता लगाया जा सके।

उद्योग मानक 1990 में आईईईई मानक 1149.1-1990[3] के रूप में प्रारंभिक उपयोग के कई वर्षों के बाद आईईईई मानक बन गया। उसी वर्ष, इंटेल ने जेटीएजी (80486) के साथ अपनी पहली सेंट्रल प्रोसेसिंग यूनिट जारी किया, जिसके कारण सभी निर्माताओं ने तेजी से उद्योग को अपना लिया था। 1994 में, एक पूरक जिसमें सीमा स्कैन विवरण भाषा (बीएसडीएल) का विवरण शामिल था, जो जोड़ा गया था। परीक्षा के लिए सभी शून्यों के उपयोग के संबंध में और परिशोधन, मानक के उपयोग को प्रीलोड से अलग करने और केवल अवलोकन के लिए बेहतर कार्यान्वयन के लिए किया गया था और 2001 में जारी किया गया था।[4] 1990 के बाद से, इस मानक को दुनिया भर की इलेक्ट्रानिक्स कंपनियों द्वारा अपनाया गया है। सीमा स्कैन अब ज्यादातर जेटीएजी का पर्याय बन गया है, लेकिन जेटीएजी का ऐसे निर्माण अनुप्रयोगों से परे आवश्यक उपयोग है।

डिबगिंग

हालांकि जेटीएजी के प्रारंभिक अनुप्रयोगों ने बोर्ड स्तर के परीक्षण को लक्षित किया, यहाँ जेटीएजी मानक को डिवाइस, बोर्ड और प्रणाली परीक्षण, निदान और दोष अलगाव में सहायता के लिए डिज़ाइन किया गया था। आज जेटीएजी का उपयोग एकीकृत परिपथों के उप-ब्लॉकों तक पहुँचने के प्राथमिक साधन के रूप में किया जाता है, जिससे यह अंतः स्थापित प्रणाली को डीबग करने के लिए एक आवश्यक तंत्र बन जाता है जिसमें कोई अन्य डीबग-सक्षम संचार चैनल नहीं हो सकता है।[citation needed] अधिकांश प्रणालियों पर, जेटीएजी-आधारित डिबगिंग सीपीयू रीसेट के बाद पहले निर्देश से उपलब्ध है, जो इसे प्रारंभिक बूट सॉफ़्टवेयर के विकास में सहायता देता है जो कुछ भी सेट होने से पहले चलता है। एक इन-सर्किट एमुलेटर (या, अधिक सही विधि से, एक जेटीएजी एडॉप्टर) जेटीएजी का उपयोग लक्ष्य सेंट्रल प्रोसेसिंग यूनिट के अंदर ऑन-चिप डिबग मॉड्यूल तक पहुँचने के लिए परिवहन तंत्र के रूप में करता है। वे मॉड्यूल सॉफ़्टवेयर विकासकर्ता को एक एम्बेडेड प्रणाली के सॉफ़्टवेयर को आवश्यकता पड़ने पर सीधे मशीन निर्देश स्तर पर, या (अधिक विशिष्ट रूप से) उच्च स्तरीय भाषा स्रोत कोड के संदर्भ में डीबग करने देते हैं।

प्रणाली सॉफ़्टवेयर डिबग समर्थन कई सॉफ़्टवेयर विकासकर्ता के लिए जेटीएजी में रुचि रखने का मुख्य कारण है। कई सिलिकॉन आर्किटेक्चर जैसे कि पावरपीसी, एमआईपीएस, एआरएम, और एक्स86 ने मूल जेटीएजी प्रोटोकॉल के आसपास एक संपूर्ण सॉफ़्टवेयर डीबग, निर्देश ट्रेसिंग और डेटा ट्रेसिंग इन्फ्रास्ट्रक्चर का निर्माण किया। अक्सर व्यक्तिगत सिलिकॉन विक्रेता इन एक्सटेंशनों के कुछ हिस्सों को ही प्रायुक्त करते हैं। कुछ उदाहरण एआरएम कोरसाइट और नेक्सस (मानक) के साथ-साथ इंटेल के बीटीएस (ब्रांच ट्रेस स्टोरेज), एलबीआर (लास्ट ब्रांच रिकॉर्ड), और आईपीटी (इंटेल प्रोसेसर ट्रेस) कार्यान्वयन हैं। ऐसे कई अन्य सिलिकॉन विक्रेता-विशिष्ट एक्सटेंशन हैं, जिन्हें गैर-प्रकटीकरण समझौते के अलावा प्रलेखित नहीं किया जा सकता है। जेटीएजी मानक को अपनाने से जेटीएजी-केंद्रित डिबगिंग वातावरण को प्रारंभिक प्रोसेसर-विशिष्ट डिज़ाइनों से दूर करने में मदद मिली। प्रोसेसर को सामान्य रूप से रोका जा सकता है, सिंगल स्टेप किया जा सकता है, या स्वतंत्र रूप से चलने दिया जा सकता है। रैम में कोड के लिए (अक्सर एक विशेष मशीन निर्देश का उपयोग करके) और रैम/फ़्लैश दोनों में कोड ब्रेकप्वाइंट सेट कर सकते हैं। डेटा ब्रेकप्वाइंट अक्सर उपलब्ध होते हैं, जैसा कि रैम में बल्क डेटा डाउनलोड होता है। अधिकांश डिज़ाइनों में हाल्ट मोड डिबगिंग है, लेकिन कुछ डिबगर्स को रजिस्टरों और डेटा बसों तक पहुंचने की अनुमति देते हैं, बिना कोर को डिबग किए रोकने की आवश्यकता होती है। कुछ टूलचेन एआरएम एंबेडेड ट्रेस मैक्रोसेल (ईटीएम) मॉड्यूल या अन्य आर्किटेक्चर में समकक्ष कार्यान्वयन का उपयोग कर सकते हैं, जो तर्क विश्लेषक जैसे जटिल हार्डवेयर घटनाओं पर डिबगर (या ट्रेसिंग) गतिविधि को ट्रिगर करने के लिए प्रोग्राम किया जाता है, जो एक विशेष सबरूटीन से एक रजिस्टर में पहले सात एक्सेस को अनदेखा करने के लिए प्रोग्राम किया जाता है।

कभी-कभी एफपीजीए डेवलपर डीबगिंग टूल विकसित करने के लिए जेटीएजी का भी उपयोग करते हैं।[5] सीपीयू के अंदर चलने वाले सॉफ़्टवेयर को डिबग करने के लिए उपयोग की जाने वाली वही जेटीएजी तकनीकें एफपीजीए के अंदर अन्य डिजिटल डिज़ाइन ब्लॉक को डीबग करने में मदद कर सकती हैं। उदाहरण के लिए, कस्टम जेटीएजी निर्देश एफपीजीए के अंदर संकेतों के मनमाने सेट से निर्मित पठन रजिस्टरों को अनुमति देने के लिए प्रदान किए जा सकते हैं, जो उन व्यवहारों के लिए दृश्यता प्रदान करते हैं जो सीमा स्कैन संचालन के लिए अदृश्य हैं। इसी तरह, ऐसे रजिस्टर लिखने से नियंत्रणीयता मिल सकती है जो अन्यथा उपलब्ध नहीं है।

फर्मवेयर भंडारण

जेटीएजी प्रोग्रामर (हार्डवेयर) को डेटा को आंतरिक गैर-वाष्पशील डिवाइस मेमोरी (जैसे जटिल प्रोग्रामेबल लॉजिक डिवाइस ) में स्थानांतरित करने की अनुमति देता है। कुछ डिवाइस प्रोग्रामर प्रोग्रामिंग के साथ-साथ डिवाइस को डिबग करने के लिए एक दोहरे उद्देश्य की पूर्ति करते हैं। एफपीजीए के मामले में, सामान्य रूप से विकास कार्य के दौरान जेटीएजी पोर्ट के माध्यम से अस्थिर स्मृति उपकरणों को भी प्रोग्राम किया जा सकता है। इसके अलावा, आंतरिक निगरानी क्षमताओं (तापमान, वोल्टेज और करंट) को जेटीएजी पोर्ट के माध्यम से एक्सेस किया जा सकता है।

जेटीएजी प्रोग्रामर का उपयोग सॉफ्टवेयर और डेटा को फ्लैश मेमोरी में लिखने के लिए भी किया जाता है। यह आमतौर पर उसी डेटा बस एक्सेस का उपयोग करके किया जाता है जिसका सीपीयू उपयोग करेगा, और कभी-कभी सीपीयू द्वारा नियंत्रित किया जाता है। अन्य मामलों में मेमोरी चिप्स में स्वयं जेटीएजी इंटरफेस होता है। कुछ आधुनिक डिबग आर्किटेक्चर सीपीयू को रोकने और लेने की आवश्यकता के बिना आंतरिक और बाहरी बस मास्टर एक्सेस प्रदान करते हैं। सबसे खराब स्थिति में, सीमा स्कैन सुविधा का उपयोग करके बाहरी बस संकेतों को चलाना आमतौर पर संभव है।

एक व्यावहारिक मामले के रूप में, एक एम्बेडेड प्रणाली विकसित करते समय, निर्देश स्टोर का अनुकरण करना डिबग चक्र (संपादन, संकलन, डाउनलोड, परीक्षण और डिबग) को प्रायुक्त करने का सबसे तेज़ तरीका है।[citation needed] इसका कारण यह है कि इन-सर्किट इम्यूलेटर एक इंस्ट्रक्शन स्टोर का अनुकरण करता है, जिसे यूएसबी के माध्यम से डेवलपमेंट होस्ट से बहुत जल्दी अपडेट किया जा सकता है। फ्लैश पर फर्मवेयर अपलोड करने के लिए सीरियल यूएआरटी पोर्ट और बूटलोडर का उपयोग करना इस डीबग चक्र को उपकरणों के मामले में काफी धीमा और संभवतः महंगा बनाता है; जेटीएजी के माध्यम से फर्मवेयर को फ्लैश (या फ्लैश के बजाय एसरैम) में स्थापित करना इन चरम सीमाओं के बीच एक मध्यवर्ती समाधान है।

सीमा स्कैन परीक्षण

जेटीएजी सीमा स्कैन तकनीक डिवाइस पिन सहित एक जटिल एकीकृत सर्किट के कई तर्क संकेतों तक पहुंच प्रदान करती है। टीएपी के माध्यम से सुलभ सीमा स्कैन रजिस्टर (बीएसआर) में संकेतों का प्रतिनिधित्व किया जाता है। यह परीक्षण और डिबगिंग के लिए संकेतों की स्थिति को नियंत्रित करने के साथ-साथ परीक्षण की अनुमति देता है। इसलिए, सॉफ्टवेयर और हार्डवेयर (निर्माण) दोनों दोषों का पता लगाया जा सकता है और एक ऑपरेटिंग डिवाइस की निगरानी की जा सकती है।

अंतर्निहित स्व-परीक्षण (बिल्ट-इन सेल्फ-टेस्ट) के साथ संयुक्त होने पर, जेटीएजी स्कैन चेन कुछ स्थैतिक दोषों (शॉर्ट्स, ओपन्स और लॉजिक एरर्स) के लिए आईसी का परीक्षण करने के लिए कम ओवरहेड, एम्बेडेड समाधान को सक्षम करती है। स्कैन श्रृंखला तंत्र आम तौर पर होने वाले समय, तापमान या अन्य गतिशील परिचालन त्रुटियों के निदान या परीक्षण में मदद नहीं करता है। परीक्षण मामला अक्सर मानकीकृत प्रारूपों जैसे सीरियल वेक्टर प्रारूप, या इसके बाइनरी सिबलिंग एक्सएसवीएफ में प्रदान किए जाते हैं, और उत्पादन परीक्षणों में उपयोग किए जाते हैं। तैयार बोर्डों पर इस तरह के परीक्षण करने की क्षमता आज के उत्पादों में परीक्षण के लिए डिजाइन का एक अनिवार्य हिस्सा है, जिससे ग्राहकों को उत्पाद भेजने से पहले पाए जाने वाले दोषों की संख्या बढ़ जाती है।

विद्युत विशेषताएँ

जेटीएजी इंटरफ़ेस चिप में जोड़ा गया एक विशेष इंटरफ़ेस है। जेटीएजी के संस्करण के आधार पर, दो, चार या पाँच पिन जोड़े जाते हैं। चार और पांच पिन इंटरफेस को डिज़ाइन किया गया है कि यदि विशिष्ट शर्तें पूरी होती हैं तो एक बोर्ड पर कई चिप्स अपनी जेटीएजी लाइनों को एक साथ डेज़ी चेन (इलेक्ट्रिकल इंजीनियरिंग) से जोड़ सकते हैं।[6] दो पिन इंटरफ़ेस को इस तरह से डिज़ाइन किया गया है कि एक तारक संस्थिति में कई चिप्स को जोड़ा जा सकता है। किसी भी मामले में एक सर्किट बोर्ड पर सभी चिप्स तक पहुंच के लिए एक परीक्षण जांच को केवल एक जेटीएजी पोर्ट से कनेक्ट करने की आवश्यकता होती है।

डेज़ी-जंजीर जेटीएजी (आईईईई 1149.1)

कनेक्टर पिन हैं:

- टीडीआई (टेस्ट डेटा इन)

- टीडीओ(टेस्ट डेटा आउट)

- टीकेके (परीक्षण घड़ी)

- टीएमएस (टेस्ट मोड सेलेक्ट)

- टीआरएसटी (टेस्ट रीसेट) वैकल्पिक।

टीआरएसटी पिन परीक्षण तर्क के लिए एक वैकल्पिक सक्रिय-निम्न रीसेट है, आमतौर पर एसिंक्रोनस, लेकिन कभी-कभी सिंक्रोनस, चिप पर निर्भर करता है। यदि पिन उपलब्ध नहीं है, तो टीसीके और टीएमएस का उपयोग करके समकालिक रूप से रीसेट स्थिति में स्विच करके परीक्षण तर्क को रीसेट किया जा सकता है। ध्यान दें कि टेस्ट लॉजिक को रीसेट करने का मतलब किसी और चीज को रीसेट करना जरूरी नहीं है। आम तौर पर कुछ प्रोसेसर-विशिष्ट जेटीएजी ऑपरेशन होते हैं जो डिबग किए जा रहे चिप के सभी या हिस्से को रीसेट कर सकते हैं।

चूंकि केवल एक डेटा लाइन उपलब्ध है, प्रोटोकॉल सीरियल संचार है। क्लॉक इनपुट टीकेके पिन पर है। एक बिट डेटा टीडीआई से स्थानांतरित किया जाता है, और टीडीओप्रति टीकेके राइजिंग क्लॉक एज में स्थानांतरित किया जाता है। विभिन्न निर्देश लोड किए जा सकते हैं। विशिष्ट आईसी के लिए निर्देश चिप आईडी, नमूना इनपुट पिन, ड्राइव (या फ्लोट) आउटपुट पिन पढ़ सकते हैं, चिप कार्यों या बाईपास (कई चिप्स की श्रृंखला को तार्किक रूप से छोटा करने के लिए टीडीओ को पाइप टीडीआई) में हेरफेर कर सकते हैं।

किसी भी क्लॉक्ड सिग्नल की तरह, टीडीआई को प्रस्तुत किया गया डेटा कुछ चिप-विशिष्ट सेटअप समय से पहले और प्रासंगिक (यहाँ, बढ़ते हुए) क्लॉक एज के बाद होल्ड समय के लिए मान्य होना चाहिए। टीडीओडेटा टीकेके के गिरने के बाद कुछ चिप-विशिष्ट समय के लिए मान्य है।

टीसीके की अधिकतम ऑपरेटिंग आवृत्ति श्रृंखला में सभी चिप्स के आधार पर भिन्न होती है (न्यूनतम गति का उपयोग किया जाना चाहिए), लेकिन यह आमतौर पर 10-100 मेगाहर्ट्ज (100-10 एनएस प्रति बिट) है। साथ ही टीकेके आवृत्तियाँ बोर्ड लेआउट और जेटीएजी अडैप्टर क्षमताओं और स्थिति पर निर्भर करती हैं। एक चिप में 40 मेगाहर्टज जेटीएजी घड़ी हो सकती है, लेकिन केवल तभी जब वह गैर-जेटीएजी संचालन के लिए 200 मेगाहर्टज घड़ी का उपयोग कर रही हो; और कम पावर मोड में होने पर इसे बहुत धीमी घड़ी का उपयोग करने की आवश्यकता हो सकती है। तदनुसार, कुछ जेटीएजी एडेप्टरों में Rटीकेके (रिटर्न टीकेके) सिग्नल का उपयोग करते हुए अनुकूली क्लॉकिंग होती है। तेज़ टीकेके फ़्रीक्वेंसी सबसे अधिक उपयोगी होती है जब जेटीएजी का उपयोग बहुत अधिक डेटा स्थानांतरित करने के लिए किया जाता है, जैसे कि किसी प्रोग्राम को निष्पादन योग्य फ्लैश मेमोरी में संग्रहीत करना।

एक मानकीकृत जेटीएजी राज्य मशीन के माध्यम से टीएमएस चरणों पर क्लॉकिंग परिवर्तन। जेटीएजी स्टेट मशीन रीसेट कर सकती है, एक इंस्ट्रक्शन रजिस्टर को एक्सेस कर सकती है, या इंस्ट्रक्शन रजिस्टर द्वारा चुने गए डेटा को एक्सेस कर सकती है।

जेटीएजी प्लेटफॉर्म अक्सर आईईईई 1149.1 विनिर्देश द्वारा परिभाषित मुट्ठी भर संकेतों को जोड़ते हैं। एक प्रणाली रीसेट (एसआरएसटी) सिग्नल काफी सामान्य है, डिबगर्स को पूरे प्रणाली को रीसेट करने देता है, न कि केवल जेटीएजी समर्थन वाले हिस्से को रीसेट करता है। कभी-कभी मेजबान द्वारा गतिविधि को ट्रिगर करने के लिए या जेटीएजी या शायद अतिरिक्त नियंत्रण रेखाओं के माध्यम से मॉनिटर किए जा रहे डिवाइस द्वारा ईवेंट सिग्नल का उपयोग किया जाता है।

भले ही कुछ उपभोक्ता उत्पाद एक स्पष्ट जेटीएजी पोर्ट कनेक्टर प्रदान करते हैं, संयोजन अक्सर मुद्रित सर्किट बोर्ड पर विकास प्रोटोटाइप और/या उत्पादन के अवशेष के रूप में उपलब्ध होते हैं। उपयोग किए जाने पर, ये संयोजन अक्सर रिवर्स इंजीनियरिंग के लिए सबसे व्यवहार्य साधन प्रदान करते हैं।

कम पिन काउंट जेटीएजी (आईईईई 1149.7)

कम पिन काउंट जेटीएजी केवल दो तारों, एक क्लॉक वायर और एक डेटा वायर का उपयोग करता है। इसे आईईईई 1149.7 मानक के भाग के रूप में परिभाषित किया गया है।[7]कनेक्टर पिन हैं:

- टीएमएससी (टेस्ट सीरियल डेटा)

- टीकेके (परीक्षण घड़ी)

कॉम्पैक्ट जेटीएजी के लिए इसे सीजेटीएजी कहा जाता है।

दो वायर इंटरफेस ने पिनों की संख्या पर दबाव कम कर दिया, और उपकरणों को स्टार टोपोलॉजी में जोड़ा जा सकता है।[8] स्टार टोपोलॉजी प्रणाली के कुछ हिस्सों को संचालित करने में सक्षम बनाती है, जबकि अन्य को अभी भी जेटीएजी पर एक्सेस किया जा सकता है; एक डेज़ी श्रृंखला के लिए सभी जेटीएजी इंटरफेस को संचालित करने की आवश्यकता होती है। अन्य दो-तार इंटरफेस मौजूद हैं, जैसे समान इंटरफ़ेस मानक।

संचार मॉडल

जेटीएजी में, डिवाइस एक या अधिक टेस्ट एक्सेस पोर्ट्स (TAP) को उजागर करते हैं। ऊपर दी गई तस्वीर तीन टीएपी दिखाती है, जो अलग-अलग चिप्स हो सकती हैं या एक चिप के अंदर मॉड्यूल हो सकती हैं। टीएपी की एक डेज़ी श्रृंखला को स्कैन श्रृंखला या (शिथिल रूप से) लक्ष्य कहा जाता है। स्कैन चेन मनमाने विधि से लंबी हो सकती हैं, लेकिन व्यवहार में बीस टीएपी असामान्य रूप से लंबी होती हैं।[citation needed]

जेटीएजी का उपयोग करने के लिए, एक होस्ट लक्ष्य के जेटीएजी सिग्नल (टीएमएस, टीकेके, टीडीआई, TDO, आदि) से किसी प्रकार के जेटीएजी एडॉप्टर के माध्यम से जुड़ा होता है, जिसे लेवल शिफ्टिंग और विद्युत अपघटन जैसे मुद्दों को संभालने की आवश्यकता हो सकती है। एडॉप्टर कुछ इंटरफ़ेस जैसे यूएसबी, PCI, ईथरनेट, और इसके आगे के उपयोग से होस्ट से जुड़ता है।

आदिम

मेजबान टीएपी के साथ संचार करता है टीसीएस और टीडीआई को टीसीके के संयोजन के साथ जोड़कर, और टीडीओ (जो केवल मानक होस्ट-साइड इनपुट है) के माध्यम से परिणाम पढ़ता है। टीएमएस/टीडीआई/टीकेके आउटपुट ट्रांज़िशन मूल जेटीएजी संचार आदिम बनाता है जिस पर उच्च परत प्रोटोकॉल का निर्माण होता है:

- स्टेट स्विचिंग ... सभी TAP एक ही स्थिति में हैं, और टीकेके ट्रांज़िशन पर वह स्थिति बदल जाती है। यह जेटीएजी स्टेट मशीन जेटीएजी स्पेक का हिस्सा है, और इसमें सोलह राज्य शामिल हैं। छह स्थिर अवस्थाएँ हैं जहाँ टीएमएस को स्थिर रखना अवस्था को बदलने से रोकता है। अन्य सभी राज्यों में, टीसीके हमेशा उस स्थिति को बदलता है। इसके अलावा, टीआरएसटी को जोर देकर उन स्थिर अवस्थाओं (Test_Logic_Reset) में से एक में प्रवेश करने के लिए बाध्य करता है, जो टीएमएस को पांच बार ऊपर रखने और टीसीके को साइकिल चलाने के विकल्प की तुलना में थोड़े तेज तरीके से करता है।

- स्थानांतरण ... जेटीएजी राज्य मशीन के अधिकांश भाग दो स्थिर अवस्थाओं का समर्थन करते हैं जिनका उपयोग डेटा स्थानांतरित करने के लिए किया जाता है। प्रत्येक TAP में एक निर्देश रजिस्टर (IR) और एक डेटा रजिस्टर (DR) होता है। उन रजिस्टरों का आकार TAP के बीच भिन्न होता है, और उन रजिस्टरों को टीडीआई और टीडीओके माध्यम से जोड़कर एक बड़ा शिफ्ट रजिस्टर बनाया जाता है। (DR का आकार उस TAP के वर्तमान IR में मान का एक कार्य है, और संभवतः SCAN_N निर्देश द्वारा निर्दिष्ट मान का है।) उस शिफ्ट रजिस्टर पर परिभाषित तीन ऑपरेशन हैं:

- एक अस्थायी मूल्य पर कब्जा

- Shift_IR स्थिर स्थिति में प्रवेश Capture_IR स्थिति से होकर जाता है, शिफ्ट रजिस्टर को आंशिक रूप से निश्चित मान के साथ लोड करना (वर्तमान निर्देश नहीं)

- Shift_DR स्थिर स्थिति में प्रवेश Capture_DR स्थिति से होकर जाता है, TAP के वर्तमान IR द्वारा निर्दिष्ट डेटा रजिस्टर के मान को लोड करता है।

- उस मान को बिट-दर-बिट स्थानांतरित करना, या तो Shift_IR या Shift_DR स्थिर स्थिति में; टीसीके ट्रांज़िशन शिफ्ट रजिस्टर को एक बिट शिफ्ट करता है, टीडीआई से टीडीओ की ओर, बिल्कुल एक सीरियल पेरिफेरल इंटरफेस बस मोड 1 डेटा ट्रांसफर की तरह डिवाइस की डेज़ी चेन के माध्यम से (टीएमएस = 0 के साथ चिप सेलेक्ट सिग्नल की तरह काम करता है, टीडीआई एमओएसआई, आदि के रूप में)। .

- अपडेट_आईआर या अपडेट_डीआर स्थिति के माध्यम से संक्रमण पर, स्थानांतरित अस्थायी मूल्य से आईआर या डीआर अपडेट करना। ध्यान दें कि एक रजिस्टर को बिना लिखे (अपडेट) किए पढ़ना (कैप्चर) करना संभव नहीं है, और इसके विपरीत। एक सामान्य मुहावरा यह कहने के लिए फ्लैग बिट्स जोड़ता है कि क्या अपडेट के साइड इफेक्ट होने चाहिए, या हार्डवेयर ऐसे साइड इफेक्ट को निष्पादित करने के लिए तैयार है या नहीं।

- एक अस्थायी मूल्य पर कब्जा

- चल रहा है ... एक स्थिर अवस्था को रन_टेस्ट/निष्क्रिय कहा जाता है। भेद टीएपी-विशिष्ट है। निष्क्रिय स्थिति में टीकेके को क्लॉक करने का कोई विशेष साइड इफेक्ट नहीं है, लेकिन इसे Run_Test स्थिति में क्लॉक करने से प्रणाली की स्थिति बदल सकती है। उदाहरण के लिए, कुछ ARM9 कोर डिबगिंग मोड का समर्थन करते हैं जहां Run_Test अवस्था में टीकेके चक्र निर्देश पाइपलाइन को चलाते हैं।

एक बुनियादी स्तर पर, जेटीएजी के उपयोग में निर्देश पढ़ना और लिखना और उनसे जुड़े डेटा रजिस्टर शामिल हैं; और कभी-कभी इसमें कई परीक्षण चक्र चलाना शामिल होता है। उन रजिस्टरों के पीछे हार्डवेयर है जो जेटीएजी द्वारा निर्दिष्ट नहीं है, और जिसके अपने राज्य हैं जो जेटीएजी गतिविधियों से प्रभावित हैं।

अधिकांश जेटीएजी होस्ट दो राज्यों के बीच सबसे छोटे रास्ते का उपयोग करते हैं, शायद एडॉप्टर की विचित्रताओं से विवश। (उदाहरण के लिए, एक एडेप्टर[which?] केवल उन पथों को संभालता है जिनकी लंबाई सात बिट्स के गुणक हैं।) जेटीएजी के शीर्ष पर निर्मित कुछ परतें राज्य के संक्रमणों की निगरानी करती हैं, और उच्च स्तर के संचालन को ट्रिगर करने के लिए असामान्य पथों का उपयोग करती हैं। कुछ एआरएम कोर दो-तार (गैर-जेटीएजी) सीरियल वायर डिबग मोड में प्रवेश करने और बाहर निकलने के लिए ऐसे अनुक्रमों का उपयोग करते हैं। आईईईई 1149.7 में जीरो बिट स्कैन (जेडबीएस) अनुक्रम का उपयोग किया जाता है[7] उन्नत कार्यक्षमता तक पहुँचने के लिए जैसे TAP को स्कैन चेन, पावर प्रबंधन और एक अलग दो-तार मोड में स्विच करना और बाहर करना।

जेटीएजी आईईईई Std 1149.1 (सीमा स्कैन) निर्देश

निर्देश रजिस्टर का आकार छोटा होता है, शायद चार या सात बिट चौड़ा। BYPASS और परीक्षा को छोड़कर, सभी निर्देश ऑपकोड को TAP कार्यान्वयनकर्ता द्वारा परिभाषित किया गया है, जैसा कि उनके संबंधित डेटा रजिस्टर हैं; अपरिभाषित निर्देश कोड का उपयोग नहीं किया जाना चाहिए। दो प्रमुख निर्देश हैं:

- BYPASS निर्देश, TAP के निर्देश रजिस्टर आकार की परवाह किए बिना सभी का एक ओपकोड, सभी TAP द्वारा समर्थित होना चाहिए। निर्देश एक बिट डेटा रजिस्टर (जिसे बायपास भी कहा जाता है) का चयन करता है। निर्देश इस उपकरण को बायपास करने की अनुमति देता है (कुछ नहीं करें) जबकि स्कैन पथ में अन्य उपकरणों का प्रयोग किया जाता है।[4]* वैकल्पिक IDCODE निर्देश, एक कार्यान्वयनकर्ता-परिभाषित ओपकोड के साथ। IDCODE 32-बिट रजिस्टर (IDCODE) से जुड़ा है। इसका डेटा एक मानकीकृत प्रारूप का उपयोग करता है जिसमें एक निर्माता कोड (JEDEC मानक निर्माता की पहचान कोड मानक, JEP-106 से प्राप्त), निर्माता द्वारा निर्दिष्ट एक भाग संख्या और एक भाग संस्करण कोड शामिल होता है। IDCODE व्यापक रूप से समर्थित है, लेकिन सार्वभौमिक रूप से समर्थित नहीं है।

RESET स्थिति से बाहर निकलने पर, निर्देश रजिस्टर या तो BYPASS या IDCODE के साथ पहले से लोड होता है। यह जेटीएजी मेजबानों को स्कैन श्रृंखला के आकार और कम से कम आंशिक रूप से सामग्री की पहचान करने की अनुमति देता है जिससे वे जुड़े हुए हैं। (वे RESET स्थिति में प्रवेश कर सकते हैं और फिर डेटा रजिस्टर को तब तक स्कैन कर सकते हैं जब तक कि वे अपने द्वारा लिखे गए डेटा को वापस न पढ़ लें। एक BYPASS रजिस्टर में केवल एक शून्य बिट होता है, जबकि एक IDCODE रजिस्टर 32-बिट होता है और एक से शुरू होता है। इसलिए बिट्स द्वारा नहीं लिखा जाता है। मेजबान को आसानी से टीएपी में मैप किया जा सकता है।) इस तरह की पहचान अक्सर मैन्युअल कॉन्फ़िगरेशन की जांच करने के लिए उपयोग की जाती है, क्योंकि IDCODE अक्सर विशिष्ट नहीं होता है। उदाहरण के लिए यह माइक्रोकंट्रोलर विक्रेता या मॉडल को निर्दिष्ट किए बिना ARM Cortex-M3 आधारित माइक्रोकंट्रोलर की पहचान कर सकता है; या एक विशेष एफपीजीए, लेकिन यह नहीं कि इसे कैसे प्रोग्राम किया गया है।

एक सामान्य मुहावरे में बायपास को एक को छोड़कर सभी टीएपी के निर्देश रजिस्टरों में स्थानांतरित करना शामिल है, जो कुछ अन्य निर्देश प्राप्त करता है। इस तरह एक को छोड़कर सभी टीएपी एक बिट डेटा रजिस्टर को उजागर करते हैं, और मूल्यों को किसी अन्य टीएपी को प्रभावित किए बिना चुनिंदा रूप से उस एक टीएपी के डेटा रजिस्टर में या उससे बाहर स्थानांतरित किया जा सकता है।

आईईईई 1149.1 (जेटीएजी) मानक सीमा स्कैन अनुप्रयोगों का समर्थन करने के लिए कई निर्देशों का वर्णन करता है। इनमें से कुछ निर्देश अनिवार्य हैं, लेकिन सीमा स्कैन परीक्षण के बजाय डिबग के लिए उपयोग किए जाने वाले टीएपी कभी-कभी इन निर्देशों के लिए न्यूनतम या कोई समर्थन नहीं देते हैं। वे अनिवार्य निर्देश सीमा स्कैन विवरण भाषा फ़ाइल में परिभाषित सीमा स्कैन रजिस्टर (बीएसआर) पर काम करते हैं और इसमें शामिल हैं:

- बाह्य परीक्षण के लिए परीक्षा, जैसे कि बोर्ड स्तर के व्यवहारों की जांच के लिए पिन का उपयोग करना

- परीक्षा से पहले लोड हो रहे पिन आउटपुट मानों को प्रीलोड करें (कभी-कभी मानक के साथ संयुक्त)

- बाउंड्री स्कैन रजिस्टर में सैंपल रीडिंग पिन वैल्यू

आईईईई-परिभाषित वैकल्पिक निर्देशों में शामिल हैं:

- BYPASS के एक वैरिएंट को CLAMP करें जो प्रीलोडेड मानों का उपयोग करके आउटपुट पिन को ड्राइव करता है

- HIGHZ सभी पिनों के आउटपुट को निष्क्रिय कर देता है

- आंतरिक परीक्षण के लिए रुचि, जैसे ऑन-चिप व्यवहार की जांच के लिए पिन का उपयोग करना

- RUNBIST चिप को सेल्फ-टेस्ट मोड में रखता है

- USERCODE उपयोगकर्ता-परिभाषित कोड लौटाता है, उदाहरण के लिए यह पहचानने के लिए कि कौन सी एफपीजीए छवि सक्रिय है

उपकरण अधिक निर्देशों को परिभाषित कर सकते हैं, और वे परिभाषाएँ निर्माता द्वारा प्रदान की गई बीएसडीएल फ़ाइल का हिस्सा होनी चाहिए। उन्हें अक्सर केवल निजी के रूप में चिह्नित किया जाता है।

सीमा स्कैन रजिस्टर

डिवाइस इनपुट और आउटपुट पिन के एक सेट के माध्यम से दुनिया से संवाद करते हैं। अपने आप में, ये पिन डिवाइस की कार्यप्रणाली में सीमित दृश्यता प्रदान करते हैं। हालाँकि, सीमा स्कैन का समर्थन करने वाले उपकरणों में डिवाइस के प्रत्येक सिग्नल पिन के लिए एक शिफ्ट-रजिस्टर सेल होता है। ये रजिस्टर डिवाइस की सीमा (इसलिए नाम) के चारों ओर समर्पित पथ में जुड़े हुए हैं। पथ एक वर्चुअल एक्सेस क्षमता बनाता है जो सामान्य इनपुट और आउटपुट को दरकिनार करता है, डिवाइस का सीधा नियंत्रण प्रदान करता है और सिग्नल के लिए विस्तृत दृश्यता प्रदान करता है।[9] सीमा स्कैन रजिस्टर की सामग्री, सिग्नल I/O क्षमताओं सहित, आमतौर पर निर्माता द्वारा भाग-विशिष्ट सीमा स्कैन विवरण भाषा फ़ाइल का उपयोग करके वर्णित की जाती है। बोर्ड निर्माण में उपयोग किए जाने वाले परीक्षणों को विकसित करने के लिए सीएडी/ईडीए प्रणाली से डिजाइन 'नेटलिस्ट' के साथ इनका उपयोग किया जाता है। एक पूर्ण प्रणाली के लिए वाणिज्यिक परीक्षण प्रणालियों में अक्सर कई हजार डॉलर खर्च होते हैं, और इसमें खुले सर्किट और शॉर्ट्स जैसे दोषों को इंगित करने के लिए नैदानिक विकल्प शामिल होते हैं। वे ग्राफिकल तरीके से गलती को चित्रित करने के लिए योजनाबद्ध या लेआउट दर्शकों को भी पेश कर सकते हैं।

सीमा स्कैनिंग को सक्षम करने के लिए, आईसी विक्रेता प्रत्येक सिग्नल पिन के लिए स्कैन सेल सहित अपने प्रत्येक डिवाइस में तर्क जोड़ते हैं। इन कोशिकाओं को फिर सीमा स्कैन शिफ्ट रजिस्टर (बीएसआर) बनाने के लिए एक साथ जोड़ा जाता है, जो एक टीएपी नियंत्रक से जुड़ा होता है। ये डिज़ाइन अधिकांश Verilog या VHDL पुस्तकालयों के भाग हैं। इस अतिरिक्त तर्क के लिए ओवरहेड न्यूनतम है, और आम तौर पर बोर्ड स्तर पर कुशल परीक्षण को सक्षम करने के लिए कीमत के लायक है।

उदाहरण: ARM11 डिबग TAP

एक उदाहरण वास्तविक प्रणालियों में जेटीएजी के संचालन को दिखाने में मदद करता है। यहाँ उदाहरण ARM11 प्रोसेसर, ARM1136 का डिबग TAP है[10] मुख्य। प्रोसेसर में स्वयं व्यापक जेटीएजी क्षमता है, जो कि अन्य सीपीयू कोर में पाई जाती है, और इसे जेटीएजी के माध्यम से और भी व्यापक क्षमताओं के साथ चिप्स में एकीकृत किया गया है।

यह एक गैर-तुच्छ उदाहरण है, जो जेटीएजी-सक्षम प्रणाली के एक महत्वपूर्ण क्रॉस सेक्शन का प्रतिनिधि है। इसके अलावा, यह दिखाता है कि जेटीएजी के रजिस्टर रीड/राइट प्रिमिटिव का उपयोग करके नियंत्रण तंत्र कैसे बनाए जाते हैं, और कैसे वे जटिल तर्क तत्वों के परीक्षण और डिबगिंग की सुविधा के लिए गठबंधन करते हैं; सीपीयू आम हैं, लेकिन एफपीजीए और एप्लिकेशन-विशिष्ट एकीकृत सर्किट में अन्य जटिल तत्व शामिल हैं जिन्हें डीबग करने की आवश्यकता है।

इस कोर के लाइसेंसधारी इसे चिप्स में एकीकृत करते हैं, आमतौर पर इसे अन्य टीएपी के साथ-साथ कई बाह्य उपकरणों और मेमोरी के साथ जोड़ते हैं। उन अन्य टीएपी में से एक संपूर्ण चिप के लिए सीमा स्कैन परीक्षण को संभालता है; यह डीबग टीएपी द्वारा समर्थित नहीं है। ऐसे चिप्स के उदाहरणों में शामिल हैं:

टेक्सास इंस्ट्रूमेंट्स ओएमएपी OMAP, जिसमें सीमा स्कैन TAP, ARM1136 डिबग TAP, ETB11 ट्रेस बफर TAP, टेक्सास इंस्ट्रूमेंट्स टीएमएस320, और ARM7 TDMI-आधारित इमेजिंग इंजन के लिए एक TAP शामिल है, सीमा स्कैन TAP (ICEpick-B) के साथ ) TAP को जेटीएजी स्कैन श्रृंखला के अंदर और बाहर विभाजित करने की क्षमता रखता है।[11]

- i.MX31 प्रोसेसर, जो समान है, हालांकि इसका प्रणाली जेटीएजी बाउंड्री स्कैन TAP है,[12] जो ICEpick से बहुत अलग है, और इसमें DSP और इमेजिंग इंजन के बजाय इसके DMA इंजन के लिए TAP शामिल है।

वे प्रोसेसर दोनों वायरलेस हैंडसेट जैसे सेल फोन में उपयोग के लिए अभिप्रेत हैं, जो इस कारण का हिस्सा है कि वे TAP नियंत्रकों को शामिल करते हैं जो जेटीएजी स्कैन श्रृंखला को संशोधित करते हैं: कम बिजली के संचालन को डिबग करने के लिए चिप्स तक पहुँचने की आवश्यकता होती है जब वे बड़े पैमाने पर संचालित होते हैं, और इस प्रकार जब नहीं सभी टीएपी चालू हैं। वह स्कैन चेन संशोधन आगामी आईईईई 1149.7 का एक विषय है[7]मानक।

जेटीजी सुविधाएं

यह डिबग TAP कई मानक निर्देशों को उजागर करता है, और कुछ विशेष रूप से हार्डवेयर-सहायता प्राप्त डिबगिंग के लिए डिज़ाइन किए गए हैं, जहाँ एक सॉफ़्टवेयर टूल (डीबगर) जेटीएजी का उपयोग डीबग किए जा रहे प्रणाली के साथ संवाद करने के लिए करता है:

BYPASSऔरIDCODE, मानक निर्देश जैसा कि ऊपर वर्णित हैपरीक्षा,INTEST, मानक निर्देश, लेकिन बाहरी सीमा स्कैन श्रृंखला के बजाय कोर पर काम करना।परीक्षामुख्य रूप से डेटा को कोर में लिखने के लिए है,INTESTनाममात्र इसे पढ़ने के लिए है; लेकिन दो स्कैन चेन उस नियम के अपवाद हैं।SCAN_Nउपयोग की जाने वाली क्रमांकित स्कैन श्रृंखला का चयन करने के लिए एआरएम निर्देशपरीक्षायाINTEST. छह स्कैन चेन हैं:0- डिवाइस आईडी रजिस्टर, रीड-ओनली आइडेंटिफिकेशन डेटा के 40 बिट1- डिबग स्थिति और नियंत्रण रजिस्टर (DSCR), 32 बिट्स का उपयोग डिबग सुविधाओं को संचालित करने के लिए किया जाता है4- इंस्ट्रक्शन ट्रांसफर रजिस्टर (ITR), 33 बिट्स (32 इंस्ट्रक्शन प्लस वन स्टेटस बिट) एक विशेष डिबग मोड में प्रोसेसर निर्देशों को निष्पादित करने के लिए उपयोग किया जाता है (नीचे देखें)5- डिबग कम्युनिकेशंस चैनल (DCC), 34 बिट्स (एक लंबा डेटा शब्द और दो स्टेटस बिट्स) का उपयोग द्विदिश डेटा को कोर में स्थानांतरित करने के लिए किया जाता है। डीबगर-जागरूक सॉफ़्टवेयर से बात करते समय इसका उपयोग डीबग मोड में और संभवतः रनटाइम पर किया जाता है।6- एंबेडेड ट्रेस मॉड्यूल (ईटीएम), 40 बिट्स (7 बिट एड्रेस, एक 32-बिट लंबा डेटा शब्द, और एक आर/डब्ल्यू बिट) एक निष्क्रिय निर्देश और डेटा ट्रेस तंत्र के संचालन को नियंत्रित करने के लिए उपयोग किया जाता है। यह या तो ऑन-चिप एंबेडेड ट्रेस बफर (ETB), या एक बाहरी हाई स्पीड ट्रेस डेटा कलेक्शन पॉड को फीड करता है। ट्रेसिंग निष्क्रिय डिबगिंग (निष्पादन इतिहास की जांच) और प्रदर्शन ट्यूनिंग के लिए प्रोफाइलिंग का समर्थन करता है।7- डिबग मॉड्यूल, 40 बिट्स (7 बिट एड्रेस, एक 32-बिट लंबा डेटा शब्द, और एक आर/डब्ल्यू बिट) हार्डवेयर ब्रेकप्वाइंट, वॉचपॉइंट, और बहुत कुछ एक्सेस करने के लिए उपयोग किया जाता है। इन्हें तब लिखा जा सकता है जब प्रोसेसर चल रहा हो; इसे डिबग मोड में होने की आवश्यकता नहीं है।

HALTऔरRESTART, ARM11-विशिष्ट निर्देश सीपीयू को रोकने और पुनः आरंभ करने के लिए। इसे रोकने से कोर डिबग मोड में आ जाता है, जहां ITR का उपयोग निर्देशों को निष्पादित करने के लिए किया जा सकता है, जिसमें DCC का उपयोग करके डीबग (जेटीएजी) होस्ट और सीपीयू के बीच डेटा स्थानांतरित करना शामिल है।ITRSEL, ITR के साथ कुछ कार्यों में तेजी लाने के लिए ARM11-विशिष्ट निर्देश।

वह मॉडल अन्य एआरएम कोर में प्रयुक्त मॉडल जैसा दिखता है। गैर-एआरएम प्रणाली में आम तौर पर समान क्षमताएं होती हैं, शायद जेटीएजी, या अन्य विक्रेता-विशिष्ट योजनाओं के शीर्ष पर नेक्सस (मानक) प्रोटोकॉल का उपयोग करके प्रायुक्त की जाती हैं।

पुराने ARM7 और ARM9 कोर में एक एंबेडेडिस मॉड्यूल शामिल है[13] जो उन अधिकांश सुविधाओं को जोड़ती है, लेकिन निर्देश निष्पादन के लिए एक अजीब तंत्र है: डीबगर को सीपीयू निर्देश पाइपलाइन, घड़ी से घड़ी चलाना चाहिए, और सीपीयू को डेटा पढ़ने और लिखने के लिए डेटा बसों तक सीधे पहुंचना चाहिए। ARM11 उन पुराने कोर के समान ट्रेस सपोर्ट (ETM, ETB) के लिए उसी मॉडल का उपयोग करता है।

नए एआरएम कॉर्टेक्स कोर इस डीबग मॉडल के समान दिखते हैं, लेकिन प्रत्यक्ष सीपीयू एक्सेस के बजाय डीबग एक्सेस पोर्ट (डीएपी) पर निर्मित होते हैं। इस आर्किटेक्चर (नाम CoreSight Technology) में, कोर और जेटीएजी मॉड्यूल पूरी तरह से स्वतंत्र हैं। उन्हें जेटीएजी से भी अलग किया जाता है ताकि उन्हें केवल छह-तार जेटीएजी इंटरफ़ेस के बजाय ARM के दो-तार 'SWD' इंटरफ़ेस (नीचे देखें) पर होस्ट किया जा सके। (एआरएम चार मानक जेटीएजी सिग्नल लेता है और वैकल्पिक टीआरएसटी जोड़ता है, साथ ही अनुकूली क्लॉकिंग के लिए उपयोग किया जाने वाला आरटीकेके सिग्नल।) CoreSight जेटीएजी-DP कोर घड़ियों के लिए अतुल्यकालिक है, और आरटीकेके को प्रायुक्त नहीं करता है।[14] साथ ही, नए कोर ने ट्रेस सपोर्ट को अपडेट किया है।

हॉल्ट मोड डिबगिंग

सॉफ़्टवेयर डिबग करने का एक मूल तरीका एकल थ्रेडेड मॉडल प्रस्तुत करना है, जहां डीबगर समय-समय पर प्रोग्राम के निष्पादन को रोकता है और रजिस्टर सामग्री और मेमोरी (परिधीय नियंत्रक रजिस्टरों सहित) द्वारा उजागर की गई स्थिति की जांच करता है। जब दिलचस्प कार्यक्रम की घटनाएँ सामने आती हैं, तो एक व्यक्ति एक विशेष दुर्व्यवहार कैसे होता है, यह देखने के लिए एकल चरण निर्देश (या स्रोत कोड की पंक्तियाँ) लेना चाहता है।