इंटेल 4004: Difference between revisions

No edit summary |

m (17 revisions imported from alpha:इंटेल_4004) |

||

| (4 intermediate revisions by 2 users not shown) | |||

| Line 25: | Line 25: | ||

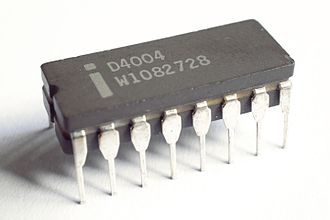

'''[[Intel|इंटेल]]''' '''4004''' [[4-बिट कंप्यूटिंग]] [[सेंट्रल प्रोसेसिंग यूनिट]] (सीपीयू) है। जिसे इंटेल कॉर्पोरेशन द्वारा 1971 में प्रमाणित किया गया था।और US$60 में बेचा गया। और (2022 में $430 के सामान्य ,2023 में $449.43) रखा गया था,<ref>{{cite web|url=https://arstechnica.com/information-technology/2011/11/the-40th-birthday-ofmaybethe-first-microprocessor/|title=The 40th birthday of—maybe—the first microprocessor, the Intel 4004|date=15 November 2011}}</ref> यह प्रथम व्यावसायिक रूप से निर्मित [[माइक्रोप्रोसेसर]] था,<ref>{{cite web |url=http://www.intel.co.uk/content/www/uk/en/history/museum-story-of-intel-4004.html |title=The Story of the Intel 4004 |website=Intel}}</ref> और [[इंटेल माइक्रोप्रोसेसरों की सूची|इंटेल माइक्रोप्रोसेसरों लिस्ट]] में यह प्रथम माइक्रोप्रोसेसर था । | '''[[Intel|इंटेल]]''' '''4004''' [[4-बिट कंप्यूटिंग]] [[सेंट्रल प्रोसेसिंग यूनिट]] (सीपीयू) है। जिसे इंटेल कॉर्पोरेशन द्वारा 1971 में प्रमाणित किया गया था।और US$60 में बेचा गया। और (2022 में $430 के सामान्य ,2023 में $449.43) रखा गया था,<ref>{{cite web|url=https://arstechnica.com/information-technology/2011/11/the-40th-birthday-ofmaybethe-first-microprocessor/|title=The 40th birthday of—maybe—the first microprocessor, the Intel 4004|date=15 November 2011}}</ref> यह प्रथम व्यावसायिक रूप से निर्मित [[माइक्रोप्रोसेसर]] था,<ref>{{cite web |url=http://www.intel.co.uk/content/www/uk/en/history/museum-story-of-intel-4004.html |title=The Story of the Intel 4004 |website=Intel}}</ref> और [[इंटेल माइक्रोप्रोसेसरों की सूची|इंटेल माइक्रोप्रोसेसरों लिस्ट]] में यह प्रथम माइक्रोप्रोसेसर था । | ||

4004 एमओएस सिलिकॉन गेट टेक्नोलॉजी (एसजीटी) की श्रेष्ठता का प्रदर्शन करते हुए बड़े | 4004 एमओएस सिलिकॉन गेट टेक्नोलॉजी (एसजीटी) की श्रेष्ठता का प्रदर्शन करते हुए बड़े मानदंड पर एकीकरण का प्रथम महत्वपूर्ण उदाहरण था। वर्तमान तकनीक की तुलना में, एसजीटी ही चिप क्षेत्र में ट्रांजिस्टर की संख्या से दोगुनी ऑपरेटिंग गति के साथ एकीकृत होती है। प्रदर्शन में इस स्टेप-फंक्शन वृद्धि ने उपिस्थित मल्टी-चिप सीपीयू की स्थान सिंगल-चिप सीपीयू को संभव बनाया था। अभिनव 4004 चिप डिजाइन सम्मिश्र लॉजिक और मेमोरी सर्किट के लिए एसजीटी का उपयोग करने के विधियों पर मॉडल के रूप में कार्य करता है, इस प्रकार विश्व के सेमीकंडक्टर उद्योग द्वारा एसजीटी को अपनाने में शीघ्रता लाता है। फेयरचाइल्ड में मूल एसजीटी के विकासकर्ता [[फेडेरिको फागिन]] थे जिन्होंने प्रथम वाणिज्यिक एकीकृत सर्किट (आईसी) डिजाइन किया था जिसने नवीन तकनीक का प्रयोग किया था, जो एनालॉग/डिजिटल अनुप्रयोगों (1968 में फेयरचाइल्ड 3708) के लिए अपनी श्रेष्ठता प्रमाणित करता है। इसके पश्चात् उन्होंने पहले सिंगल चिप माइक्रोप्रोसेसर बनाने के लिए आवश्यक अभूतपूर्व एकीकरण प्राप्त करने के लिए इंटेल में एसजीटी का उपयोग किया था। | ||

यह परियोजना 1969 में अपने इतिहास का पता लगाती है, जब बिजनेसकॉम | यह परियोजना 1969 में अपने इतिहास का पता लगाती है, जब बिजनेसकॉम को बिजनेसकॉम कार्पोरेशन. ने [[इलेक्ट्रॉनिक कैलकुलेटर]] के लिए सात चिप्स के वर्ग को डिजाइन करने के लिए इंटेल से संपर्क किया, जिनमें से तीन ने भिन्न-भिन्न गणना मशीनों को बनाने के लिए विशेष रूप से सीपीयू का गठन किया। सीपीयू शिफ्ट-रजिस्टरों पर संग्रहीत डेटा और रोम (रीड ओनली मेमोरी) पर संग्रहीत निर्देशों पर आधारित था। तीन-चिप सीपीयू लॉजिक डिज़ाइन की सम्मिश्रता ने [[मार्सियन हॉफ]] को रैम (रैंडम एक्सेस मेमोरी) पर संग्रहीत डेटा के आधार पर अधिक पारंपरिक सीपीयू आर्किटेक्चर का प्रस्ताव दिया। यह आर्किटेक्चर बहुत सरल और अधिक सामान्य-उद्देश्य वाला था और यह संभावित रूप से चिप में एकीकृत किया जा सकता था, इस प्रकार निवेश कम करने और इसकी गति में सुधार हुआ था। डिजाइन की प्रारंभ अप्रैल 1970 में फेडेरिको फागिन के निर्देशन में [[मासाटोशी द्वीप|मासाटोशी शीमा]] द्वारा की गई थी, जिन्होंने आर्किटेक्चर और पश्चात् में लॉजिक डिजाइन में योगदान दिया। पूरी प्रकार से परिचालित 4004 की पहली डिलीवरी मार्च 1971 में बुसीकॉम को इसके 141-पीएफ प्रिंटिंग कैलकुलेटर इंजीनियरिंग प्रोटोटाइप (अब माउंटेन व्यू, कैलिफोर्निया में [[कंप्यूटर इतिहास संग्रहालय]] में प्रदर्शित) के लिए की गई थी।<ref>{{cite web|url=http://www.intel4004.com/proto_calc.htm|title=The Intel 4004 Microprocessor and the Silicon Gate Technology: The Busicom Engineering Prototype|website=Intel4004.com}}</ref> इसकी सामान्य सेल जुलाई 1971 से प्रारंभ हुई। | ||

[[फेयरचाइल्ड सेमीकंडक्टर]] में कार्य करते हुए फागिन द्वारा विकसित किए गए अनेक नवाचारों ने 4004 को चिप पर उत्पादित करने की अनुमति दी थी। मुख्य अवधारणा धातु के अतिरिक्त पॉलीसिलिकॉन से बने [[स्व-संरेखित गेट|सेल्फ-अलिग्नेड गेट]] का उपयोग था, जिसने घटकों को साथ बहुत समीप होने और उच्च गति से कार्य करने की अनुमति दी। 4004 को संभव बनाने के लिए, फागिन ने बूटस्ट्रैप लोड भी विकसित किया था, जिसे सिलिकॉन गेट के साथ अव्यवहार्य माना जाता है, और दबे हुए संपर्क ने सिलिकॉन गेट्स को धातु के उपयोग के बिना सीधे ट्रांजिस्टर के स्रोत और नाली से जोड़ा जा सकता है। इसके साथ में, इन नवाचारों ने सर्किट घनत्व को दोगुना कर दिया, और इस प्रकार निवेश को आधा कर दिया था, जिससे चिप में 2,300 ट्रांजिस्टर सम्मिलित हो गए और एल्यूमीनियम गेट्स के साथ पिछली एमओएस तकनीक का उपयोग करने वाले डिजाइनों की तुलना में पांच गुना तीव्र हो गए। | [[फेयरचाइल्ड सेमीकंडक्टर]] में कार्य करते हुए फागिन द्वारा विकसित किए गए अनेक नवाचारों ने 4004 को चिप पर उत्पादित करने की अनुमति दी थी। मुख्य अवधारणा धातु के अतिरिक्त पॉलीसिलिकॉन से बने [[स्व-संरेखित गेट|सेल्फ-अलिग्नेड गेट]] का उपयोग था, जिसने घटकों को साथ बहुत समीप होने और उच्च गति से कार्य करने की अनुमति दी। 4004 को संभव बनाने के लिए, फागिन ने बूटस्ट्रैप लोड भी विकसित किया था, जिसे सिलिकॉन गेट के साथ अव्यवहार्य माना जाता है, और दबे हुए संपर्क ने सिलिकॉन गेट्स को धातु के उपयोग के बिना सीधे ट्रांजिस्टर के स्रोत और नाली से जोड़ा जा सकता है। इसके साथ में, इन नवाचारों ने सर्किट घनत्व को दोगुना कर दिया, और इस प्रकार निवेश को आधा कर दिया था, जिससे चिप में 2,300 ट्रांजिस्टर सम्मिलित हो गए और एल्यूमीनियम गेट्स के साथ पिछली एमओएस तकनीक का उपयोग करने वाले डिजाइनों की तुलना में पांच गुना तीव्र हो गए। | ||

| Line 45: | Line 45: | ||

</ref> इसका मुख्य अंतर यह था कि बुसीकॉम डिजाइन 101 में महंगे विलंब-लाइन मेमोरी या मैग्नेटोस्ट्रिक्टिव देरी लाइनों के अतिरिक्त भिन्न-भिन्न घटकों से भरे [[मुद्रित सर्किट]] बोर्डों और स्मृति के लिए ठोस-स्थान [[शिफ्ट का रजिस्टर|शिफ्ट का रजिस्टरों]] को परिवर्तित करने के लिए एकीकृत सर्किट का उपयोग करता हैं। | </ref> इसका मुख्य अंतर यह था कि बुसीकॉम डिजाइन 101 में महंगे विलंब-लाइन मेमोरी या मैग्नेटोस्ट्रिक्टिव देरी लाइनों के अतिरिक्त भिन्न-भिन्न घटकों से भरे [[मुद्रित सर्किट]] बोर्डों और स्मृति के लिए ठोस-स्थान [[शिफ्ट का रजिस्टर|शिफ्ट का रजिस्टरों]] को परिवर्तित करने के लिए एकीकृत सर्किट का उपयोग करता हैं। | ||

प्रथम के कैलकुलेटर डिजाइनों के विपरीत, बुसिकॉम ने सामान्य-उद्देश्य प्रोसेसर अवधारणा विकसित की थी, जिसका लक्ष्य इसे कम-अंत वाले डेस्कटॉप प्रिंटिंग कैलकुलेटर में प्रस्तुत करना था, और फिर [[नकदी - रजिस्टर|कैश - रजिस्टर]] और स्वचालित टेलर मशीन जैसी अन्य भूमिकाओं के लिए उसी डिज़ाइन का उपयोग करना था। कंपनी ने पहले ही [[ट्रांजिस्टर-ट्रांजिस्टर तर्क|ट्रांजिस्टर-ट्रांजिस्टर लॉजिक]] [[छोटे पैमाने पर एकीकरण|लघु | प्रथम के कैलकुलेटर डिजाइनों के विपरीत, बुसिकॉम ने सामान्य-उद्देश्य प्रोसेसर अवधारणा विकसित की थी, जिसका लक्ष्य इसे कम-अंत वाले डेस्कटॉप प्रिंटिंग कैलकुलेटर में प्रस्तुत करना था, और फिर [[नकदी - रजिस्टर|कैश - रजिस्टर]] और स्वचालित टेलर मशीन जैसी अन्य भूमिकाओं के लिए उसी डिज़ाइन का उपयोग करना था। कंपनी ने पहले ही [[ट्रांजिस्टर-ट्रांजिस्टर तर्क|ट्रांजिस्टर-ट्रांजिस्टर लॉजिक]] [[छोटे पैमाने पर एकीकरण|लघु मानदंड पर एकीकरण]] लॉजिकआई सीका उपयोग करके कैलकुलेटर का उत्पादन किया था और इंटेल की [[मध्यम स्तर का एकीकरण]] (एमएसआई) तकनीकों का उपयोग करके इंटेल को चिप की संख्या कम करने में रुचि थी।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=10}} | ||

इंटेल ने दो कंपनियों के मध्य संपर्क के रूप में कार्य करने के लिए वर्तमान में नियुक्त मार्सियन हॉफ, कर्मचारी संख्या 12 को नियुक्त किया। जून के अंत में, बिजनेसकॉम के तीन इंजीनियरों, मासाटोशी शिमा और उनके सहयोगियों मसुदा और ताकायामा ने डिजाइन प्रस्तुत करने के लिए इंटेल की यात्रा की थी। चूँकि उन्हें केवल इंजीनियरों के साथ संपर्क करने के लिए नियुक्त किया गया था, हॉफ ने अवधारणा का अध्ययन करना प्रारंभ किया। उनके प्रारंभिक प्रस्ताव में सात आईसी, कार्यक्रम नियंत्रण, अंकगणित इकाई ( | इंटेल ने दो कंपनियों के मध्य संपर्क के रूप में कार्य करने के लिए वर्तमान में नियुक्त मार्सियन हॉफ, कर्मचारी संख्या 12 को नियुक्त किया। जून के अंत में, बिजनेसकॉम के तीन इंजीनियरों, मासाटोशी शिमा और उनके सहयोगियों मसुदा और ताकायामा ने डिजाइन प्रस्तुत करने के लिए इंटेल की यात्रा की थी। चूँकि उन्हें केवल इंजीनियरों के साथ संपर्क करने के लिए नियुक्त किया गया था, हॉफ ने अवधारणा का अध्ययन करना प्रारंभ किया। उनके प्रारंभिक प्रस्ताव में सात आईसी, कार्यक्रम नियंत्रण, अंकगणित इकाई (आईएनएस), समय, कार्यक्रम रोम, अस्थायी मेमोरी, प्रिंटर नियंत्रक और इनपुट/आउटपुट नियंत्रण के लिए शिफ्ट रजिस्टर थे।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=11}} | ||

हॉफ चिंतित हो गए कि चिप्स की संख्या और उनके मध्य आवश्यक अंतर्संबंधों के कारण बुसिकॉम के मूल्य लक्ष्यों को पूरा करना असंभव हो जाएगा। चिप्स को मिलाने से सम्मिश्रता और निवेश कम होगी। उन्हें इस बात की भी चिंता थी कि अभी भी लघु इंटेल के समीप ही समय में सात भिन्न-भिन्न चिप्स बनाने के लिए पर्याप्त डिज़ाइन कर्मचारी नहीं होंगे। उन्होंने ऊपरी प्रबंधन के साथ इन चिंताओं को उठाया, और [[बॉब नोयस]], सीईओ, ने हॉफ से कहा कि यदि यह व्यवहार्य प्रतीत होता है तब वह भिन्न दृष्टिकोण का समर्थन करेंगे।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=11}} | हॉफ चिंतित हो गए कि चिप्स की संख्या और उनके मध्य आवश्यक अंतर्संबंधों के कारण बुसिकॉम के मूल्य लक्ष्यों को पूरा करना असंभव हो जाएगा। चिप्स को मिलाने से सम्मिश्रता और निवेश कम होगी। उन्हें इस बात की भी चिंता थी कि अभी भी लघु इंटेल के समीप ही समय में सात भिन्न-भिन्न चिप्स बनाने के लिए पर्याप्त डिज़ाइन कर्मचारी नहीं होंगे। उन्होंने ऊपरी प्रबंधन के साथ इन चिंताओं को उठाया, और [[बॉब नोयस]], सीईओ, ने हॉफ से कहा कि यदि यह व्यवहार्य प्रतीत होता है तब वह भिन्न दृष्टिकोण का समर्थन करेंगे।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=11}} | ||

=== सरलीकृत डिजाइन === | === सरलीकृत डिजाइन === | ||

बिजनेसकॉम डिज़ाइन में प्रमुख अवधारणा यह थी कि प्रोग्राम नियंत्रण और | बिजनेसकॉम डिज़ाइन में प्रमुख अवधारणा यह थी कि प्रोग्राम नियंत्रण और आईएनएस विशेष रूप से कैलकुलेटर बाज़ार पर लक्षित नहीं थे, यह रोममें प्रोग्राम था जिसने इसे कैलकुलेटर में परिवर्तन कर दिया। मूल विचार यह था कि कंपनी ही चिप्स का उपयोग भिन्न-भिन्न मात्रा में शिफ्ट रजिस्टर रैम और प्रोग्राम रोम के साथ गणना मशीनों की श्रृंखला के उत्पादन के लिए कर सकती है। हॉफ इस बात से चकित थे कि बुसिकॉम के [[निर्देश सेट वास्तुकला|निर्देश सेट आर्किटेक्चर]] का सामान्य-उद्देश्य वाले कंप्यूटरों से कितना मेल खाता है। उन्होंने इस बात पर विचार करना प्रारंभ किया कि क्या वास्तव में सामान्य-उद्देश्य वाले प्रोसेसर को इतना सस्ता बनाया जा सकता है कि उसे कैलकुलेटर में प्रयोग किया जा सकता है।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=12}} जब इसके पश्चात् उनसे पूछा गया कि उन्हें पहले माइक्रोप्रोसेसर की आर्किटेक्चर के लिए विचार कहां से मिले, तब हॉफ ने बताया कि ब्रिटिश ट्रैक्टर कंपनी, [[प्लेसी]],<ref>Possibly he had confused the Plessey name with that of [[Massey Ferguson]], makers of agricultural machinery.</ref> [[स्टैनफोर्ड]] को मिनीकंप्यूटर दान किया था, और जब वह वहां थे तब उन्होंने इसके साथ खेला था। तदाशी सासाकी (इंजीनियर) ने कैलकुलेटर को चार भागों में विभाजित करने के विचार का श्रेय नारा महिला कॉलेज की अज्ञात महिला को दिया था, जो इंटेल के साथ अपनी पहली बैठक से पहले जापान में आयोजित विचार-मंथन बैठक में उपस्थित थी।<ref>{{cite web | ||

|url = http://www.ieeeghn.org/wiki/index.php/Oral-History:Tadashi_Sasaki | |url = http://www.ieeeghn.org/wiki/index.php/Oral-History:Tadashi_Sasaki | ||

|title = Oral-History: Tadashi Sasaki | |title = Oral-History: Tadashi Sasaki | ||

| Line 68: | Line 68: | ||

हॉफ के लिए अज्ञात, बुसिकॉम टीम उनके प्रस्ताव में अत्यधिकरूचि ले रही थी। चूँकि, अनेक विशिष्ट उद्देश्य थे जिनके बारे में वह चिंतित थे। प्रमुख उद्देश्य यह था कि दशमलव एडजस्टमेंट और कीबोर्ड हैंडलिंग जैसे कुछ रूटीन सबरूटीन्स के रूप में प्रयुक्त होने पर बड़ी मात्रा में रोम स्पेस का उपयोग करेंगे। दूसरा यह था कि डिज़ाइन में किसी प्रकार की अवरोध नहीं था इसलिए वास्तविक समय की घटनाओं से निपटना कठिन होगा। अंत में, 4-बिट बीसीडी के रूप में संख्याओं को संग्रहीत करने के लिए साइन और दशमलव स्थान को स्टोर करने के लिए अतिरिक्त मेमोरी की आवश्यकता होती हैं।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=13}} | हॉफ के लिए अज्ञात, बुसिकॉम टीम उनके प्रस्ताव में अत्यधिकरूचि ले रही थी। चूँकि, अनेक विशिष्ट उद्देश्य थे जिनके बारे में वह चिंतित थे। प्रमुख उद्देश्य यह था कि दशमलव एडजस्टमेंट और कीबोर्ड हैंडलिंग जैसे कुछ रूटीन सबरूटीन्स के रूप में प्रयुक्त होने पर बड़ी मात्रा में रोम स्पेस का उपयोग करेंगे। दूसरा यह था कि डिज़ाइन में किसी प्रकार की अवरोध नहीं था इसलिए वास्तविक समय की घटनाओं से निपटना कठिन होगा। अंत में, 4-बिट बीसीडी के रूप में संख्याओं को संग्रहीत करने के लिए साइन और दशमलव स्थान को स्टोर करने के लिए अतिरिक्त मेमोरी की आवश्यकता होती हैं।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=13}} | ||

सितंबर 1969 में, [[स्टेनली मेजर]] फेयरचाइल्ड से इंटेल में सम्मिलित हुए। हॉफ और मजोर शीघ्र ही बुसिकॉम चिंताओं के समाधान के साथ सामने आए। उपनेमकाओं की सम्मिश्रता को संबोधित करने के लिए, मूल रूप से बाइट [[macbook|मैकबुक]] और सम्मिश्र | सितंबर 1969 में, [[स्टेनली मेजर]] फेयरचाइल्ड से इंटेल में सम्मिलित हुए। हॉफ और मजोर शीघ्र ही बुसिकॉम चिंताओं के समाधान के साथ सामने आए। उपनेमकाओं की सम्मिश्रता को संबोधित करने के लिए, मूल रूप से बाइट [[macbook|मैकबुक]] और सम्मिश्र डिको विचार सर्किटरी का उपयोग करके बुसिकॉम के डिजाइन का समाधान किया गया, मजोर ने 20-बाइट लंबा [[दुभाषिया (कंप्यूटिंग)|इंटरप्रेटर (कंप्यूटिंग)]] विकसित किया जो समान मैक्रोइन्स्ट्रक्शन को निष्पादित करता था। शिमा ने नया व्यवधान जोड़ने का सुझाव दिया जो पिन द्वारा ट्रिगर किया जाएगा, जिससे कीबोर्ड को बाधित करने की अनुमति मिलेगी। उन्होंने एक्युमुलेटर (कंप्यूटिंग) को रिक्त करने के लिए ब्रांच बैक (सबरूटीन से परिवर्तित) निर्देश को भी संशोधित किया हैं।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=14}} | ||

मूल्य लक्ष्यों तक पहुंचने के लिए, यह महत्वपूर्ण था कि चिप जितना संभव हो उतना छोटा हो और कम से कम संख्या में लीड का उपयोग करे। चूंकि डेटा 4-बिट्स का था और [[पता स्थान|एड्रेस स्पेस]] 12-बिट्स (4096 बाइट्स) था, लगभग 24-पिनों से कम किसी भी चीज़ के साथ सीधी पहुंच की व्यवस्था नहीं की जा सकती थी। यह | मूल्य लक्ष्यों तक पहुंचने के लिए, यह महत्वपूर्ण था कि चिप जितना संभव हो उतना छोटा हो और कम से कम संख्या में लीड का उपयोग करे। चूंकि डेटा 4-बिट्स का था और [[पता स्थान|एड्रेस स्पेस]] 12-बिट्स (4096 बाइट्स) था, लगभग 24-पिनों से कम किसी भी चीज़ के साथ सीधी पहुंच की व्यवस्था नहीं की जा सकती थी। यह अधिक छोटा नहीं था, इसलिए डिजाइन 16-पिन दोहरे [[दोहरी इन-लाइन पैकेज|डुअल इन-लाइन पैकेज]] डीआईपी) लेआउट का उपयोग करेगा और 4 लाइनों के सेट के [[बहुसंकेतन|मल्टीप्लेक्सिंग]] का उपयोग करेगा। इसका अर्थ यह निर्दिष्ट करना था कि रोम में किस पते को आवश्यक तीन घड़ी चक्रों तक पहुंचना है, और अन्य दो इसे स्मृति से पढ़ने के लिए। 1 मेगाहर्ट्ज पर चलने से यह लगभग 80 माइक्रोसेकंड प्रति अंक पर बीसीडी मानों पर गणित करने की अनुमति देता हैं।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=15}} | ||

इंटेल और बिजनेसकॉम के मध्य विचार-विमर्श का परिणाम आर्किटेक्चर था जिसने 7-चिप बिजनेसकॉम डिज़ाइन को सीपीयू, रोम, रैम और आई (इनपुट-आउटपुट) उपकरणों से बना 4-चिप Intel प्रस्ताव में घटा दिया। इस प्रकार का प्रस्ताव अक्टूबर 1969 में बुसिकॉम के अधिकारियों की विजिटिंग टीम के सामने प्रस्तुत किया गया था। वह सहमत थे कि नवीन अवधारणा उत्तम थी, और इंटेल को विकास प्रारंभ करने की अनुमति दी गई। हॉफ यह जानने के लिए चिंतित था कि अनुबंध ने डिजाइन के सभी अधिकार बुसिकॉम को सौंपे, इसके अतिरिक्त कि यह पूरी प्रकार से इंटेल के अंदर डिजाइन किया गया था। इसके पश्चात् टीम जापान के लिए रवाना हो गई, किन्तु शिमा दिसंबर तक कैलिफ़ोर्निया में रहीं,और इन्होने अनेक सबरूटीन्स का विकास किया था।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=15}} | इंटेल और बिजनेसकॉम के मध्य विचार-विमर्श का परिणाम आर्किटेक्चर था जिसने 7-चिप बिजनेसकॉम डिज़ाइन को सीपीयू, रोम, रैम और आई (इनपुट-आउटपुट) उपकरणों से बना 4-चिप Intel प्रस्ताव में घटा दिया। इस प्रकार का प्रस्ताव अक्टूबर 1969 में बुसिकॉम के अधिकारियों की विजिटिंग टीम के सामने प्रस्तुत किया गया था। वह सहमत थे कि नवीन अवधारणा उत्तम थी, और इंटेल को विकास प्रारंभ करने की अनुमति दी गई। हॉफ यह जानने के लिए चिंतित था कि अनुबंध ने डिजाइन के सभी अधिकार बुसिकॉम को सौंपे, इसके अतिरिक्त कि यह पूरी प्रकार से इंटेल के अंदर डिजाइन किया गया था। इसके पश्चात् टीम जापान के लिए रवाना हो गई, किन्तु शिमा दिसंबर तक कैलिफ़ोर्निया में रहीं,और इन्होने अनेक सबरूटीन्स का विकास किया था।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=15}} | ||

| Line 78: | Line 78: | ||

इंटीग्रेटेड सर्किट में ट्रांजिस्टर और रेसिस्टर्स जैसे अनेक भिन्न-भिन्न घटक होते हैं जो अंतर्निहित सिलिकॉन को डोपेंट के साथ मिलाकर उत्पादित किए जाते हैं। यह सामान्यतः चिप को रासायनिक गैस की उपस्थिति में गर्म करके पूरा किया जाता है, जो सतह में फैल जाती है। पहले, सतह पर जमा [[अल्युमीनियम]] तारों का उपयोग करके सर्किट बनाने के लिए भिन्न-भिन्न घटकों को साथ जोड़ा गया था। चूंकि एल्युमीनियम 600 डिग्री पर और सिलिकॉन 1000 डिग्री पर पिघलता है, निशानों को सामान्यतः अंतिम चरण के रूप में जमा करना पड़ता है, जो अधिकांशतः उत्पादन चक्र को सम्मिश्र बनाता है। | इंटीग्रेटेड सर्किट में ट्रांजिस्टर और रेसिस्टर्स जैसे अनेक भिन्न-भिन्न घटक होते हैं जो अंतर्निहित सिलिकॉन को डोपेंट के साथ मिलाकर उत्पादित किए जाते हैं। यह सामान्यतः चिप को रासायनिक गैस की उपस्थिति में गर्म करके पूरा किया जाता है, जो सतह में फैल जाती है। पहले, सतह पर जमा [[अल्युमीनियम]] तारों का उपयोग करके सर्किट बनाने के लिए भिन्न-भिन्न घटकों को साथ जोड़ा गया था। चूंकि एल्युमीनियम 600 डिग्री पर और सिलिकॉन 1000 डिग्री पर पिघलता है, निशानों को सामान्यतः अंतिम चरण के रूप में जमा करना पड़ता है, जो अधिकांशतः उत्पादन चक्र को सम्मिश्र बनाता है। | ||

1967 में, [[बेल लैब्स]] ने एमओएस ट्रांजिस्टर बनाने के बारे में पेपरप्रयुक्त किया जिसमें धातु के अतिरिक्त सिलिकॉन से बने स्व-संरेखित द्वार थे। चूँकि, यह डिवाइस प्रूफ-ऑफ-कॉन्सेप्ट थे और इनका उपयोग आई सी बनाने के लिए नहीं किया जा सकता था। फागिन और [[टॉम क्लेन]] ने जिज्ञासा को लिया और विश्वसनीय आईसी बनाने के लिए आवश्यक पूरी प्रक्रिया प्रौद्योगिकी विकसित की थी। फागिन ने फेडरिको फागिन या फेयरचाइल्ड 3708 का डिज़ाइन और निर्माण भी किया था,<ref>{{cite web |url=http://www.intel4004.com/images/elect_cov_pg1.jpg |title=A faster generation of MOS devices with low thresholds is riding the crest of the new wave, silicon-gate IC's |last=Faggin |first=Federico |access-date=3 June 2017}}</ref> एसजीटी के साथ बनाया गया प्रथम आईसी, पहली बार 1968 के अंत में बेचा गया, और इलेक्ट्रॉनिक्स के कवर पर चित्रित किया गया (29 सितंबर 1969) है।<ref>{{cite web |url=http://www.intel4004.com/papers.htm |title=''Earliest Published Papers'' |last=Faggin |first=Federico |access-date=3 June 2017}}</ref> {{sfn|Faggin|Hoff|Mazor|Shima|1996|p=16}} सिलिकॉन गेट तकनीक ने लीकेज करंट को 100 गुना से अधिक कम कर दिया, जिससे डीरैम्स (डायनेमिक रैंडम एक्सेस मेमोरी) जैसे परिष्कृत डायनेमिक सर्किट संभव हो गए थे। इसने फाटकों के लिए उपयोग किए जाने वाले अत्यधिक डोप्ड सिलिकॉन को इंटरकनेक्शन बनाने की अनुमति दी हैं, जिससे माइक्रोप्रोसेसरों जैसे यादृच्छिक-लॉजिक आईसी के सर्किट घनत्व में | 1967 में, [[बेल लैब्स]] ने एमओएस ट्रांजिस्टर बनाने के बारे में पेपरप्रयुक्त किया जिसमें धातु के अतिरिक्त सिलिकॉन से बने स्व-संरेखित द्वार थे। चूँकि, यह डिवाइस प्रूफ-ऑफ-कॉन्सेप्ट थे और इनका उपयोग आई सी बनाने के लिए नहीं किया जा सकता था। फागिन और [[टॉम क्लेन]] ने जिज्ञासा को लिया और विश्वसनीय आईसी बनाने के लिए आवश्यक पूरी प्रक्रिया प्रौद्योगिकी विकसित की थी। फागिन ने फेडरिको फागिन या फेयरचाइल्ड 3708 का डिज़ाइन और निर्माण भी किया था,<ref>{{cite web |url=http://www.intel4004.com/images/elect_cov_pg1.jpg |title=A faster generation of MOS devices with low thresholds is riding the crest of the new wave, silicon-gate IC's |last=Faggin |first=Federico |access-date=3 June 2017}}</ref> एसजीटी के साथ बनाया गया प्रथम आईसी, पहली बार 1968 के अंत में बेचा गया, और इलेक्ट्रॉनिक्स के कवर पर चित्रित किया गया (29 सितंबर 1969) है।<ref>{{cite web |url=http://www.intel4004.com/papers.htm |title=''Earliest Published Papers'' |last=Faggin |first=Federico |access-date=3 June 2017}}</ref> {{sfn|Faggin|Hoff|Mazor|Shima|1996|p=16}} सिलिकॉन गेट तकनीक ने लीकेज करंट को 100 गुना से अधिक कम कर दिया, जिससे डीरैम्स (डायनेमिक रैंडम एक्सेस मेमोरी) जैसे परिष्कृत डायनेमिक सर्किट संभव हो गए थे। इसने फाटकों के लिए उपयोग किए जाने वाले अत्यधिक डोप्ड सिलिकॉन को इंटरकनेक्शन बनाने की अनुमति दी हैं, जिससे माइक्रोप्रोसेसरों जैसे यादृच्छिक-लॉजिक आईसी के सर्किट घनत्व में अधिक सुधार हुआ हैं। | ||

इस तकनीक का अर्थ था कि प्रक्रिया में किसी भी समय इंटरकनेक्शन किए जा सकते हैं। इससे भी महत्वपूर्ण बात यह है कि तारों को उसी उपकरण का उपयोग करके जमा किया गया था जिससे बाकी घटकों को बनाया गया था। इसका अर्थ यह था कि विभिन्न मशीन प्रकारों के मध्य लेआउट में सामान्य अंतर समाप्त हो गया था। पहले इंटरकनेक्ट को आवश्यकता से अधिक बड़ा होना पड़ता था जिससे कि यह सुनिश्चित किया जा सके कि एल्यूमीनियम सिलिकॉन घटकों को छूता है जो मशीनरी में अशुद्धियों के कारण ऑफसेट हो जाएगा। इस उद्देश्य को समाप्त करने के साथ, सर्किट को साथ बहुत समीप रखा जा सकता है, यह घटकों के घनत्व को तुरंत दोगुना कर सकता है, और इस प्रकार उनकी निवेश को उसी राशि से कम कर सकता है। इसके अतिरिक्त, एल्यूमीनियम तारों ने [[संधारित्र|कैपेसिटर]] के रूप में कार्य किया जो सिग्नल की गति को सीमित करता था; इन्हें हटाने से चिप्स तीव्र गति से चलने लगे।<ref>{{cite web | url = http://www.intel4004.com/mrld.htm |title = The New Methodology for Random Logic Design |last = Faggin| first=Federico | access-date=3 June 2017}}</ref><ref>Federico Faggin, T. Klein (1970). "Silicon-Gate Technology". ''Solid State Electronics''. Vol. 13. pp. 1125–1144</ref> | इस तकनीक का अर्थ था कि प्रक्रिया में किसी भी समय इंटरकनेक्शन किए जा सकते हैं। इससे भी महत्वपूर्ण बात यह है कि तारों को उसी उपकरण का उपयोग करके जमा किया गया था जिससे बाकी घटकों को बनाया गया था। इसका अर्थ यह था कि विभिन्न मशीन प्रकारों के मध्य लेआउट में सामान्य अंतर समाप्त हो गया था। पहले इंटरकनेक्ट को आवश्यकता से अधिक बड़ा होना पड़ता था जिससे कि यह सुनिश्चित किया जा सके कि एल्यूमीनियम सिलिकॉन घटकों को छूता है जो मशीनरी में अशुद्धियों के कारण ऑफसेट हो जाएगा। इस उद्देश्य को समाप्त करने के साथ, सर्किट को साथ बहुत समीप रखा जा सकता है, यह घटकों के घनत्व को तुरंत दोगुना कर सकता है, और इस प्रकार उनकी निवेश को उसी राशि से कम कर सकता है। इसके अतिरिक्त, एल्यूमीनियम तारों ने [[संधारित्र|कैपेसिटर]] के रूप में कार्य किया जो सिग्नल की गति को सीमित करता था; इन्हें हटाने से चिप्स तीव्र गति से चलने लगे।<ref>{{cite web | url = http://www.intel4004.com/mrld.htm |title = The New Methodology for Random Logic Design |last = Faggin| first=Federico | access-date=3 June 2017}}</ref><ref>Federico Faggin, T. Klein (1970). "Silicon-Gate Technology". ''Solid State Electronics''. Vol. 13. pp. 1125–1144</ref> | ||

| Line 88: | Line 88: | ||

डिजाइन पूरा होने के साथ, शिमा कैलकुलेटर के प्रोटोटाइप का निर्माण प्रारंभ करने के लिए जापान लौट आई थी। 4001 के पहले वेफर्स को अक्टूबर 1970 में संसाधित किया गया था,{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=16}} इसके पश्चात् नवंबर में 4003 और 4002 आए। 4002 सामान्य समस्या प्रमाणित हुई जिसे सरलता से ठीक कर लिया गया। पहले 4004 दिसंबर के अंत में पहुंचे, और यह पूर्णता से गैर-कार्यात्मक थे। चिप की जांच करते हुए फागिन ने पाया कि उतर-संपर्क निर्माण चरण को छोड़ दिया गया था। दूसरा रन जनवरी 1971 में गढ़ा गया और 4004 ने दो छोटी समस्याओं को छोड़कर पूरी प्रकार से कार्य किया हैं। | डिजाइन पूरा होने के साथ, शिमा कैलकुलेटर के प्रोटोटाइप का निर्माण प्रारंभ करने के लिए जापान लौट आई थी। 4001 के पहले वेफर्स को अक्टूबर 1970 में संसाधित किया गया था,{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=16}} इसके पश्चात् नवंबर में 4003 और 4002 आए। 4002 सामान्य समस्या प्रमाणित हुई जिसे सरलता से ठीक कर लिया गया। पहले 4004 दिसंबर के अंत में पहुंचे, और यह पूर्णता से गैर-कार्यात्मक थे। चिप की जांच करते हुए फागिन ने पाया कि उतर-संपर्क निर्माण चरण को छोड़ दिया गया था। दूसरा रन जनवरी 1971 में गढ़ा गया और 4004 ने दो छोटी समस्याओं को छोड़कर पूरी प्रकार से कार्य किया हैं। | ||

शिमा के आते ही फागिन इन चिप्स के प्रतिरूप भेज रहे थे। अप्रैल में, उन्हें पता चला कि कैलकुलेटर प्रोटोटाइप | शिमा के आते ही फागिन इन चिप्स के प्रतिरूप भेज रहे थे। अप्रैल में, उन्हें पता चला कि कैलकुलेटर प्रोटोटाइप प्रारंभ था। उस महीने के पश्चात् में, शिमा ने इंटेल को 4001 रोम के लिए अंतिम मास्क भेजा, डिजाइन अब पूरा हो गया था। इसमें 4004, दो 4002, तीन 4003 और चार 4001 चिप्स सम्मिलित थे। अतिरिक्त 4001 ने वैकल्पिक वर्गमूल फलन प्रदान किया। फागिन को 4001 में निराशाजनक समस्या मिलने के पश्चात् अंतिम परिवर्तन जोड़ा गया, जो केवल तब हुआ जब चिप्स गर्म थे। नया रजिस्टर डिकोविचार सर्किट जोड़ना फागिन का समाधान था। 4002 में भी यही समस्या देखी गई थी और उसी समाधान का उपयोग किया गया था। अगस्त 1971 में मात्रा में उत्पादन प्रारंभ हुआ था।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=17}} | ||

'''4004 मार्केटिंग''' | '''4004 मार्केटिंग''' | ||

| Line 94: | Line 94: | ||

4004 का मार्केटिंग शिमा को कॉल के समय, फागिन को पता चला कि बुसिकॉम वित्तीय कठिनाई में था और यदि चिप की कीमत कम नहीं की गई तब वह विफल हो जाएगा। फागिन ने नोयस को विशिष्टता समझौते से इंटेल को मुक्त करने के बदले में कीमत कम करने के लिए राजी किया। मई 1971 में बिजनेसकॉम ने इस शर्त पर सहमति व्यक्त की कि इसका उपयोग किसी अन्य कैलकुलेटर परियोजना के लिए नहीं किया जाएगा और इंटेल उनकी $60,000 की विकास निवेश चुकाएगा।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=17}} मार्केटिंग फोकस के इस परिवर्तन के साथ चिप वर्ग का नाम बदलकर एमसीएस-4 कर दिया गया, माइक्रो कंप्यूटर सिस्टम, 4-बिट के लिए छोटा होता हैं।<ref name="FFsign"/> | 4004 का मार्केटिंग शिमा को कॉल के समय, फागिन को पता चला कि बुसिकॉम वित्तीय कठिनाई में था और यदि चिप की कीमत कम नहीं की गई तब वह विफल हो जाएगा। फागिन ने नोयस को विशिष्टता समझौते से इंटेल को मुक्त करने के बदले में कीमत कम करने के लिए राजी किया। मई 1971 में बिजनेसकॉम ने इस शर्त पर सहमति व्यक्त की कि इसका उपयोग किसी अन्य कैलकुलेटर परियोजना के लिए नहीं किया जाएगा और इंटेल उनकी $60,000 की विकास निवेश चुकाएगा।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=17}} मार्केटिंग फोकस के इस परिवर्तन के साथ चिप वर्ग का नाम बदलकर एमसीएस-4 कर दिया गया, माइक्रो कंप्यूटर सिस्टम, 4-बिट के लिए छोटा होता हैं।<ref name="FFsign"/> | ||

इंटेल प्रबंधन को संदेह था कि उनकी सेल टीम अपने ग्राहकों को उत्पाद के बारे में बता सकती है। जैसा कि इंटेल अब मेमोरी मार्केट में सफल था, वह चिंतित थे कि 4004 मार्केट को भ्रमित कर सकता है और इसे विज्ञापित करने में संकोच कर रहा था।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=17}} उन्हें | इंटेल प्रबंधन को संदेह था कि उनकी सेल टीम अपने ग्राहकों को उत्पाद के बारे में बता सकती है। जैसा कि इंटेल अब मेमोरी मार्केट में सफल था, वह चिंतित थे कि 4004 मार्केट को भ्रमित कर सकता है और इसे विज्ञापित करने में संकोच कर रहा था।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=17}} उन्हें विचार था कि वर्तमान इंटेल ग्राहक नए उत्पाद को प्रतियोगिता के रूप में देख सकते हैं, इसके अतिरिक्त प्रतिस्पर्धियों से मेमोरी खरीद सकते हैं।<ref>{{Cite web |date= |title=Intel 4004 Microprocessor 35th Anniversary |website=[[YouTube]] |url=https://www.youtube.com/watch?v=j00AULJLCNo |url-status=live}}</ref> हॉफ और मेजर भी चिंतित हैं कि डिजाइन की सीमाएं उन उपयोगकर्ताओं के लिए कम अनुभव होंगा जो उस समय मार्केट में प्रवेश करने वाले नए 16-बिट [[मिनी कंप्यूटर]] के प्रवृत्त थे।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=18}} | ||

1971 की गर्मियों में यह सब परिवर्तन गया, जब [[टेक्सस उपकरण|टेक्सास इंस्ट्रूमेंट्स,]] के पूर्व एड गेलबैक ने मार्केटिंग विभाग संभाला और तुरंत सार्वजनिक रूप से उत्पाद की घोषणा करने की योजना प्रारंभ की हैं।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=18}} यह नवंबर 1971 में हुआ जब इंटेल ने एकीकृत इलेक्ट्रॉनिक्स के नए युग की घोषणा करते हुए विज्ञापन चलाए,<ref>{{cite web | url = https://spectrum.ieee.org/tech-history/silicon-revolution/chip-hall-of-fame-intel-4004-microprocessor |title = Chip Hall of Fame: Intel 4004 Microprocessor |last = Cass| first=Stephen |date = 2 July 2018 | access-date=5 February 2019}}</ref> तब यह पहली बार [[इलेक्ट्रॉनिक समाचार|इलेक्ट्रॉनिक न्यूज़]] के 15 नवंबर संस्करण में दिखाई दे रहा है।<ref name="Gilder 1990">{{Cite book |last=Gilder |first= George |title=Microcosm: the quantum revolution in economics and technology |publisher=Simon and Schuster |year=1990 |page=[https://archive.org/details/microcosm00geor/page/107 107] |url=https://archive.org/details/microcosm00geor |url-access=registration |isbn= 978-0-671-70592-3 |quote= Intel's first advertisement for the 4004 appeared in the November 15, 1971 issue of ''Electronic News''}}</ref> | 1971 की गर्मियों में यह सब परिवर्तन गया, जब [[टेक्सस उपकरण|टेक्सास इंस्ट्रूमेंट्स,]] के पूर्व एड गेलबैक ने मार्केटिंग विभाग संभाला और तुरंत सार्वजनिक रूप से उत्पाद की घोषणा करने की योजना प्रारंभ की हैं।{{sfn|Faggin|Hoff|Mazor|Shima|1996|p=18}} यह नवंबर 1971 में हुआ जब इंटेल ने एकीकृत इलेक्ट्रॉनिक्स के नए युग की घोषणा करते हुए विज्ञापन चलाए,<ref>{{cite web | url = https://spectrum.ieee.org/tech-history/silicon-revolution/chip-hall-of-fame-intel-4004-microprocessor |title = Chip Hall of Fame: Intel 4004 Microprocessor |last = Cass| first=Stephen |date = 2 July 2018 | access-date=5 February 2019}}</ref> तब यह पहली बार [[इलेक्ट्रॉनिक समाचार|इलेक्ट्रॉनिक न्यूज़]] के 15 नवंबर संस्करण में दिखाई दे रहा है।<ref name="Gilder 1990">{{Cite book |last=Gilder |first= George |title=Microcosm: the quantum revolution in economics and technology |publisher=Simon and Schuster |year=1990 |page=[https://archive.org/details/microcosm00geor/page/107 107] |url=https://archive.org/details/microcosm00geor |url-access=registration |isbn= 978-0-671-70592-3 |quote= Intel's first advertisement for the 4004 appeared in the November 15, 1971 issue of ''Electronic News''}}</ref> | ||

| Line 113: | Line 113: | ||

== विवरण == | == विवरण == | ||

[[File:KL National INS4004.jpg|thumb|left|नेशनल सेमीकंडक्टर उनके भाग संख्या | [[File:KL National INS4004.jpg|thumb|left|नेशनल सेमीकंडक्टर उनके भाग संख्या आईएनएस4004 के अनुसार 4004 का [[दूसरा स्रोत]] निर्माता था।<ref>[http://www.cpu-world.com/CPUs/4004/index.html Intel 4004 microprocessor family], retrieved 14 Dec 2011.</ref>]] | ||

| Line 144: | Line 144: | ||

{| class="infobox" style="font-size:88%;width:23em;" | {| class="infobox" style="font-size:88%;width:23em;" | ||

|- | |- | ||

|+ | |+ इंटेल 4004 रजिस्टर | ||

|- | |- | ||

| | | | ||

| Line 161: | Line 161: | ||

| style="width:10px; text-align:center;"| <sup>0</sup><sub>1</sub> | | style="width:10px; text-align:center;"| <sup>0</sup><sub>1</sub> | ||

| style="width:10px; text-align:center;"| <sup>0</sup><sub>0</sub> | | style="width:10px; text-align:center;"| <sup>0</sup><sub>0</sub> | ||

| style="width:auto;" | ''( | | style="width:auto;" | ''(बिट स्थिति)'' | ||

|- | |- | ||

|colspan="13" | ''' | |colspan="13" | '''संचायक''' | ||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center; background:white" colspan="4"| | | style="text-align:center; background:white" colspan="4"| | ||

| style="text-align:center; background:white" colspan="4"| | | style="text-align:center; background:white" colspan="4"| | ||

| style="text-align:center;" colspan="4"| A | | style="text-align:center;" colspan="4"| A | ||

| style="width:auto; background:white; color:black;"| | | style="width:auto; background:white; color:black;"| संचायक | ||

|- | |- | ||

|colspan="13" | ''' | |colspan="13" | '''स्थिति कोड''' | ||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center; background:white" colspan="11" | | | style="text-align:center; background:white" colspan="11" | | ||

| style="text-align:center;"| C | | style="text-align:center;"| C | ||

| style="background:white; color:black" | [[Carry flag| | | style="background:white; color:black" | [[Carry flag|केरी फ्लैग flag]] | ||

|- | |- | ||

|colspan="13" | ''' | |colspan="13" | '''सूचकांक रजिस्टर''' | ||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center; background:white" colspan="4"| | | style="text-align:center; background:white" colspan="4"| | ||

| Line 218: | Line 218: | ||

| style="width:auto; background:white; color:black;"| | | style="width:auto; background:white; color:black;"| | ||

|- | |- | ||

|colspan="13" | ''' | |colspan="13" | '''प्रोग्राम काउंटर''' | ||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center;" colspan="12"| PC | | style="text-align:center;" colspan="12"| PC | ||

| style="background:white; color:black;"| | | style="background:white; color:black;"| प्रोग्राम काउंटर | ||

|- | |- | ||

|colspan="13" | | |colspan="13" | पुश-डाउन एड्रेस कॉल स्टैक<br/> | ||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center;" colspan="12"| PC1 | | style="text-align:center;" colspan="12"| PC1 | ||

| style="background:white; color:black;"| | | style="background:white; color:black;"| कॉल स्तर 1 | ||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center;" colspan="12"| PC2 | | style="text-align:center;" colspan="12"| PC2 | ||

| style="background:white; color:black;"| | | style="background:white; color:black;"| {| class="wikitable" | ||

|कॉल स्तर 2 | |||

|} | |||

|- style="background:silver;color:black" | |- style="background:silver;color:black" | ||

| style="text-align:center;" colspan="12"| PC3 | | style="text-align:center;" colspan="12"| PC3 | ||

| style="background:white; color:black;"| | | style="background:white; color:black;"| कॉल स्तर 3 | ||

|} | |} | ||

|} | |} | ||

| Line 254: | Line 256: | ||

! सिंबल !! एमआईएन. !! मैक्स | ! सिंबल !! एमआईएन. !! मैक्स | ||

|- | |- | ||

| | | वी<sub>एसएस–डीडी</sub>|| +15 वी − 5% || +15 वी + 5% | ||

|- | |- | ||

| | | वी<sub>आईएल</sub>|| वी<sub>डीडी</sub>|| वी<sub>एसएस</sub> − 5.5 वी | ||

|- | |- | ||

| | | आईएच || वी<sub>एसएस</sub> − 1.5 वी || वी<sub>एसएस</sub> + 0.3 वी | ||

|- | |- | ||

| | | वी<sub>ओएल</sub>|| वी<sub>एसएस</sub> − 12 वी || वी<sub>एसएस</sub> − 6.5 वी | ||

|- | |- | ||

| | | वी<sub>ओएच</sub>|| वी<sub>एसएस</sub> − 0.5 वी || वी<sub>एसएस</sub> | ||

|} | |} | ||

| Line 287: | Line 289: | ||

</gallery> | </gallery> | ||

== प्रयोग | == प्रयोग == | ||

माइक्रोप्रोसेसर का उपयोग करने वाला प्रथम व्यावसायिक उत्पाद बिजनेसकॉम कैलकुलेटर 141-पीएफ था। 4004 का उपयोग पहले माइक्रोप्रोसेसर-नियंत्रित [[पिनबॉल]] गेम में भी किया गया था, जो 1974 में [[बाली निर्माण]] के लिए [[डेव नटिंग एसोसिएट्स]] द्वारा निर्मित प्रोटोटाइप था। | माइक्रोप्रोसेसर का उपयोग करने वाला प्रथम व्यावसायिक उत्पाद बिजनेसकॉम कैलकुलेटर 141-पीएफ था। 4004 का उपयोग पहले माइक्रोप्रोसेसर-नियंत्रित [[पिनबॉल]] गेम में भी किया गया था, जो 1974 में [[बाली निर्माण]] के लिए [[डेव नटिंग एसोसिएट्स]] द्वारा निर्मित प्रोटोटाइप था। | ||

| Line 293: | Line 295: | ||

{{blockquote | {{blockquote | ||

| यहां मेरा अनुमान हैं कि [वह] अध्ययन [मैंने पेटेंट स्थितियों का संचालन किया]. किसी व्यावसायिक उत्पाद में | | यहां मेरा अनुमान हैं कि [वह] अध्ययन [मैंने पेटेंट स्थितियों का संचालन किया]. किसी व्यावसायिक उत्पाद में प्रथम माइक्रोप्रोसेसर था [[चार चरण प्रणालियाँ या प्रणाली|चार चरण सिस्टम AL1]]. पहला व्यावसायिक रूप से उपलब्ध ( घटक के रूप में बेचा गया) माइक्रोप्रोसेसर इंटेल का 4004 था.<ref>{{cite web |url=http://corphist.computerhistory.org/corphist/documents/doc-487ecec0af0da.pdf |title=Dissertation 2004 |access-date=2017-11-14 }}</ref> | ||

}} | }} | ||

| Line 304: | Line 306: | ||

15 अक्टूबर 2010 को, राष्ट्रपति [[बराक ओबामा]] द्वारा 4004 पर उनके अग्रणी कार्य के लिए फागिन, हॉफ और माजर को प्रौद्योगिकी और नवाचार के राष्ट्रीय पदक से सम्मानित किया गया था।<ref>{{Cite press release|url=https://obamawhitehouse.archives.gov/the-press-office/2010/10/15/president-obama-honors-nations-top-scientists-and-innovators|work=[[whitehouse.gov]]|title=President Obama Honors Nation's Top Scientists and Innovators|via=[[NARA|National Archives]]|date=15 October 2010}}</ref> | 15 अक्टूबर 2010 को, राष्ट्रपति [[बराक ओबामा]] द्वारा 4004 पर उनके अग्रणी कार्य के लिए फागिन, हॉफ और माजर को प्रौद्योगिकी और नवाचार के राष्ट्रीय पदक से सम्मानित किया गया था।<ref>{{Cite press release|url=https://obamawhitehouse.archives.gov/the-press-office/2010/10/15/president-obama-honors-nations-top-scientists-and-innovators|work=[[whitehouse.gov]]|title=President Obama Honors Nation's Top Scientists and Innovators|via=[[NARA|National Archives]]|date=15 October 2010}}</ref> | ||

== यह भी देखें == | == यह भी देखें == | ||

* [[सेंट्रल एयर डेटा कंप्यूटर]] - प्रथम 20-बिट मिलिट्री माइक्रोप्रोसेसर जून 1970 में [[अमेरिकी नौसेना]] F-14 टॉमकैट फाइटर जेट के लिए प्रयुक्त किया गया था, इंटेल 4004 प्रयुक्त होने से लगभग 1.5 वर्ष | * [[सेंट्रल एयर डेटा कंप्यूटर]] - प्रथम 20-बिट मिलिट्री माइक्रोप्रोसेसर जून 1970 में [[अमेरिकी नौसेना]] F-14 टॉमकैट फाइटर जेट के लिए प्रयुक्त किया गया था, इंटेल 4004 प्रयुक्त होने से लगभग 1.5 वर्ष पूर्व था | ||

==टिप्पणियाँ== | ==टिप्पणियाँ== | ||

| Line 331: | Line 333: | ||

*एफ। फागिन, एम. शिमा, एम.ई. हॉफ जूनियर, एच. फेनी, एस. मजोर: द एमसीएस-4—एन एलएसआई माइक्रो कंप्यूटर सिस्टम। आईईईई '72 क्षेत्र छह सम्मेलन था। [https://web.archive.org/web/20110323004736/http://www.bitsavers.org/pdf/intel/_dataBooks/MemoryDesignHandbook_Aug73.pdf इंटेल मेमोरी डिज़ाइन के पीपी. 6–32 से 6–37 पर पुनर्मुद्रित हैंडबुक: अगस्त 1973]। | *एफ। फागिन, एम. शिमा, एम.ई. हॉफ जूनियर, एच. फेनी, एस. मजोर: द एमसीएस-4—एन एलएसआई माइक्रो कंप्यूटर सिस्टम। आईईईई '72 क्षेत्र छह सम्मेलन था। [https://web.archive.org/web/20110323004736/http://www.bitsavers.org/pdf/intel/_dataBooks/MemoryDesignHandbook_Aug73.pdf इंटेल मेमोरी डिज़ाइन के पीपी. 6–32 से 6–37 पर पुनर्मुद्रित हैंडबुक: अगस्त 1973]। | ||

*[http://www.computerhistory.org/revolution/digital-logic/12/285/1534 बिजनेसकॉम 141-पी एफ प्रिंटिंग कैलकुलेटर इंजीनियरिंग प्रोटोटाइप (1971)] हैं। (कंप्यूटर इतिहास संग्रहालय, माउंटेन व्यू, सीए के लिए फेडेरिको फागिन का उपहार) हैं। सीएचएम संग्रह सूची में बिजनेसकॉम 141-पी एफ डेस्कटॉप कैलकुलेटर के इंजीनियरिंग प्रोटोटाइप की तस्वीरें दिखाई गई हैं। इंजीनियरिंग प्रोटोटाइप ने कभी भी उत्पादित होने वाले विश्व के पहले माइक्रोप्रोसेसर का प्रयोग किया। यह अपनी इस प्रकार का अनूठा प्रोटोटाइप बुसिकॉम के अध्यक्ष श्री योशियो कोजिमा द्वारा फेडेरिको फागिन को 4004 और तीन अन्य मेमोरी और आई/ओ चिप्स (एमसीएस-4 चिपसेट) के डिजाइन और विकास के उनके सफल नेतृत्व के लिए व्यक्तिगत उपहार था। ). 25 वर्ष तक इसे अपने घर में रखने के पश्चात् फागिन ने 1996 में सीएचएम को दान कर दिया। | *[http://www.computerhistory.org/revolution/digital-logic/12/285/1534 बिजनेसकॉम 141-पी एफ प्रिंटिंग कैलकुलेटर इंजीनियरिंग प्रोटोटाइप (1971)] हैं। (कंप्यूटर इतिहास संग्रहालय, माउंटेन व्यू, सीए के लिए फेडेरिको फागिन का उपहार) हैं। सीएचएम संग्रह सूची में बिजनेसकॉम 141-पी एफ डेस्कटॉप कैलकुलेटर के इंजीनियरिंग प्रोटोटाइप की तस्वीरें दिखाई गई हैं। इंजीनियरिंग प्रोटोटाइप ने कभी भी उत्पादित होने वाले विश्व के पहले माइक्रोप्रोसेसर का प्रयोग किया। यह अपनी इस प्रकार का अनूठा प्रोटोटाइप बुसिकॉम के अध्यक्ष श्री योशियो कोजिमा द्वारा फेडेरिको फागिन को 4004 और तीन अन्य मेमोरी और आई/ओ चिप्स (एमसीएस-4 चिपसेट) के डिजाइन और विकास के उनके सफल नेतृत्व के लिए व्यक्तिगत उपहार था। ). 25 वर्ष तक इसे अपने घर में रखने के पश्चात् फागिन ने 1996 में सीएचएम को दान कर दिया। | ||

*फागिन, एफ.; कैपोकैसिया, एफ. नया एकीकृत एमओएस शिफ्ट रजिस्टर, कार्यवाही एक्सवी अंतर्राष्ट्रीय इलेक्ट्रॉनिक्स वैज्ञानिक कांग्रेस, रोम, अप्रैल 1968, पीपी। 143-152। यह पेपर फरवरी 1968 में फेडरिको फागिन के पालो आल्टो (सीए) में फेयरचाइल्ड के आर एंड डी में सम्मिलित होने से | *फागिन, एफ.; कैपोकैसिया, एफ. नया एकीकृत एमओएस शिफ्ट रजिस्टर, कार्यवाही एक्सवी अंतर्राष्ट्रीय इलेक्ट्रॉनिक्स वैज्ञानिक कांग्रेस, रोम, अप्रैल 1968, पीपी। 143-152। यह पेपर फरवरी 1968 में फेडरिको फागिन के पालो आल्टो (सीए) में फेयरचाइल्ड के आर एंड डी में सम्मिलित होने से पूर्व, 1967 के अंत में एसजीएस-फेयरचाइल्ड (अब एसटी माइक्रो) में विकसित उपन्यास स्थिर एमओएस शिफ्ट रजिस्टर का वर्णन करता है। फागिन ने इसके पश्चात् में इस नए शिफ्ट रजिस्टर एमसीएस-4 चिप्स, 4004(1970) सहित का प्रयोग किया। | ||

==अग्रिम पठन== | ==अग्रिम पठन== | ||

*Faggin, फेडरिको; Hoff, Marcian Jr.; Mazor, Stanley; Shima, Masatoshi (December 1996). "The history of the 4004". आईईईई Micro. | *Faggin, फेडरिको; Hoff, Marcian Jr.; Mazor, Stanley; Shima, Masatoshi (December 1996). "The history of the 4004". आईईईई Micro. वीओएल. 16, no. 6. pp. 10–20. | ||

*[https://www.youtube.com/watch?v=j00AULJLCNo Intel 4004 | *[https://www.youtube.com/watch?v=j00AULJLCNo Intel 4004 Microproceएसएसor 35th Anniवीersary] - Liवीe recording of presentations by Ted Hoff and फेडरिको फागिन at the Coएमपीuter History Museum for the 35th anniवीersary of the first microproceएसएसor. ([[YouTube|youtube.com]]) | ||

*आईईईई | *आईईईई Sओएलid State Circuits Magazine, Winter 2009 वीओएल.1 No.1. [http://ieeexplore.ieee.org/xpl/tocresult.jsp?isYear=2009&isnumber=4776521&Submit32=View+Contents "The 4004 microproceएसएसor of Faggin, Hoff, Mazor, and Shima".] | ||

*[http://www.intel4004.com/The_MOS_Silicon_Gate_Technology_and_the_First_Microprocessors.pdf The एमओएस | *[http://www.intel4004.com/The_MOS_Silicon_Gate_Technology_and_the_First_Microprocessors.pdf The एमओएस Sआईएलicon Gate Technओएलogy and the First Microproceएसएसors], by फेडरिको फागिन published in La Riवीista del Nuoवीo Cimento, Italian Physical Society, वीओएल. 38, No. 12, 2015. | ||

* "How we made the | * "How we made the microproceएसएसor" by फेडरिको Faggin. Nature Electronics, वीओएल. 1, January 2018. Published online: 2018-01-08 | ||

==बाहरी संबंध== | ==बाहरी संबंध== | ||

*[http://www.intel.com/museum/archives/4004.htm Intel's First | *[http://www.intel.com/museum/archives/4004.htm Intel's First Microproceएसएसor—the Intel 4004: Intel Museum (Intel कार्पोरेशनorate Archiवीes) entry] | ||

*[http://www.intel4004.com/ The Intel 4004: A testimonial fरोमफेडरिको Faggin, designer of the 4004 and | *[http://www.intel4004.com/ The Intel 4004: A testimonial fरोमफेडरिको Faggin, designer of the 4004 and deवीeloper of its enabling technओएलogy] | ||

*[http://www.intel4004.com/mrld.htm The New | *[http://www.intel4004.com/mrld.htm The New Methodओएलogy for Random Logic Design Used in the 4004 and in All the Early Intel Microproceएसएसors] | ||

*[http://www.ieeeghn.org/wiki/index.php/Oral-History:Masatoshi_Shima#LSI_for_Desktop_Calculators | *[http://www.ieeeghn.org/wiki/index.php/Oral-History:Masatoshi_Shima#LSI_for_Desktop_Calculators Interवीiew with Masatoshi Shima] | ||

*[http://smithsonianchips.si.edu/ice/4004thb.htm एमसीएस-4 Micro Coएमपीuter Set Data Sheet (12 pp)] | *[http://smithsonianchips.si.edu/ice/4004thb.htm एमसीएस-4 Micro Coएमपीuter Set Data Sheet (12 pp)] | ||

*[http://www.4004.com Intel 4004 -- 45th | *[http://www.4004.com Intel 4004 -- 45th Anniवीersary Project], Schematics at the unofficial 4004 website, and a simulator in Jaवीa. Fully functional 130x scale replicas of the 4004 buआईएलt using discrete transistors. | ||

*[http://www.intel4004.com/hyatt.htm The Crucial | *[http://www.intel4004.com/hyatt.htm The Crucial Rओएलe of Sआईएलicon Design in the Inवीention of the Microproceएसएसor] | ||

*[https://web.archive.org/web/20110723120701/http://www.flylogic.net/blog/?p=63 High | *[https://web.archive.org/web/20110723120701/http://www.flylogic.net/blog/?p=63 High resओएलution light microscope pictures of an Intel 4004 die together with a basic explanation of Cएमओएस logic] | ||

*[http://www.e4004.szyc.org/ Intel 4004 Emulator, | *[http://www.e4004.szyc.org/ Intel 4004 Emulator, Aएसएसembler, and Disaएसएसembler: Siएमपीle programming toओएलs for Intel 4004 in Jaवीascript] | ||

*[http://datasheets.chipdb.org/Intel/MCS-4/datashts/intel-4004.pdf Datasheet Intel 4004] | *[http://datasheets.chipdb.org/Intel/MCS-4/datashts/intel-4004.pdf Datasheet Intel 4004] | ||

*[http://datasheets.chipdb.org/Intel/MCS-4/datashts/MCS4_Data_Sheet_Nov71.pdf Datasheet Intel एमसीएस-4] | *[http://datasheets.chipdb.org/Intel/MCS-4/datashts/MCS4_Data_Sheet_Nov71.pdf Datasheet Intel एमसीएस-4] | ||

*[http://www.4004.com/assets/BuscomV2p1.jpg | *[http://www.4004.com/assets/BuscomV2p1.jpg Buscomवी2p1 schematic] | ||

*[https://codeabbey.github.io/heavy-data-1/msc-4-asm-manual-1973.pdf MSC-4 | *[https://codeabbey.github.io/heavy-data-1/msc-4-asm-manual-1973.pdf MSC-4 Aएसएसembly Language Programming Manual] | ||

*[https://spectrum.ieee.org/tech-history/silicon-revolution/chip-hall-of-fame-intel-4004-microprocessor Chip Hall of Fame: Intel 4004 | *[https://spectrum.ieee.org/tech-history/silicon-revolution/chip-hall-of-fame-intel-4004-microprocessor Chip Hall of Fame: Intel 4004 Microproceएसएसor] ([[IEEE Spectrum|आईईईई Spectrum]] website) | ||

*[https://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html Story of the Intel 4004] | *[https://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html Story of the Intel 4004] | ||

[[Category: इंटेल माइक्रोप्रोसेसर | 4004]] [[Category: 4-बिट माइक्रोप्रोसेसर]] | [[Category: इंटेल माइक्रोप्रोसेसर | 4004]] [[Category: 4-बिट माइक्रोप्रोसेसर]] | ||

| Line 361: | Line 363: | ||

[[Category: Machine Translated Page]] | [[Category: Machine Translated Page]] | ||

[[Category:Created On 17/02/2023]] | [[Category:Created On 17/02/2023]] | ||

[[Category:Vigyan Ready]] | |||

Latest revision as of 14:14, 14 December 2023

| File:Intel C4004.jpg ग्रे निशान के साथ सफेद सिरेमिक इंटेल C4004 माइक्रोप्रोसेसर | |

| General information | |

|---|---|

| Launched | November 15, 1971 |

| Discontinued | 1981[1] |

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | 740-750 kHz |

| Data width | 4 बिट्स |

| Address width | 12 बिट्स (बहुसंकेतन) |

| Architecture and classification | |

| Application | बिज़िकॉम कैलकुलेटर, अंकगणितीय जोड़-तोड़ |

| Technology node | 10 μm |

| Instruction set | 4-bit BCD oriented |

| Physical specifications | |

| Transistors |

|

| Package(s) |

|

| Socket(s) | |

| History | |

| Successor | इंटेल 4040 |

| Support status | |

| असमर्थित | |

इंटेल 4004 4-बिट कंप्यूटिंग सेंट्रल प्रोसेसिंग यूनिट (सीपीयू) है। जिसे इंटेल कॉर्पोरेशन द्वारा 1971 में प्रमाणित किया गया था।और US$60 में बेचा गया। और (2022 में $430 के सामान्य ,2023 में $449.43) रखा गया था,[2] यह प्रथम व्यावसायिक रूप से निर्मित माइक्रोप्रोसेसर था,[3] और इंटेल माइक्रोप्रोसेसरों लिस्ट में यह प्रथम माइक्रोप्रोसेसर था ।

4004 एमओएस सिलिकॉन गेट टेक्नोलॉजी (एसजीटी) की श्रेष्ठता का प्रदर्शन करते हुए बड़े मानदंड पर एकीकरण का प्रथम महत्वपूर्ण उदाहरण था। वर्तमान तकनीक की तुलना में, एसजीटी ही चिप क्षेत्र में ट्रांजिस्टर की संख्या से दोगुनी ऑपरेटिंग गति के साथ एकीकृत होती है। प्रदर्शन में इस स्टेप-फंक्शन वृद्धि ने उपिस्थित मल्टी-चिप सीपीयू की स्थान सिंगल-चिप सीपीयू को संभव बनाया था। अभिनव 4004 चिप डिजाइन सम्मिश्र लॉजिक और मेमोरी सर्किट के लिए एसजीटी का उपयोग करने के विधियों पर मॉडल के रूप में कार्य करता है, इस प्रकार विश्व के सेमीकंडक्टर उद्योग द्वारा एसजीटी को अपनाने में शीघ्रता लाता है। फेयरचाइल्ड में मूल एसजीटी के विकासकर्ता फेडेरिको फागिन थे जिन्होंने प्रथम वाणिज्यिक एकीकृत सर्किट (आईसी) डिजाइन किया था जिसने नवीन तकनीक का प्रयोग किया था, जो एनालॉग/डिजिटल अनुप्रयोगों (1968 में फेयरचाइल्ड 3708) के लिए अपनी श्रेष्ठता प्रमाणित करता है। इसके पश्चात् उन्होंने पहले सिंगल चिप माइक्रोप्रोसेसर बनाने के लिए आवश्यक अभूतपूर्व एकीकरण प्राप्त करने के लिए इंटेल में एसजीटी का उपयोग किया था।

यह परियोजना 1969 में अपने इतिहास का पता लगाती है, जब बिजनेसकॉम को बिजनेसकॉम कार्पोरेशन. ने इलेक्ट्रॉनिक कैलकुलेटर के लिए सात चिप्स के वर्ग को डिजाइन करने के लिए इंटेल से संपर्क किया, जिनमें से तीन ने भिन्न-भिन्न गणना मशीनों को बनाने के लिए विशेष रूप से सीपीयू का गठन किया। सीपीयू शिफ्ट-रजिस्टरों पर संग्रहीत डेटा और रोम (रीड ओनली मेमोरी) पर संग्रहीत निर्देशों पर आधारित था। तीन-चिप सीपीयू लॉजिक डिज़ाइन की सम्मिश्रता ने मार्सियन हॉफ को रैम (रैंडम एक्सेस मेमोरी) पर संग्रहीत डेटा के आधार पर अधिक पारंपरिक सीपीयू आर्किटेक्चर का प्रस्ताव दिया। यह आर्किटेक्चर बहुत सरल और अधिक सामान्य-उद्देश्य वाला था और यह संभावित रूप से चिप में एकीकृत किया जा सकता था, इस प्रकार निवेश कम करने और इसकी गति में सुधार हुआ था। डिजाइन की प्रारंभ अप्रैल 1970 में फेडेरिको फागिन के निर्देशन में मासाटोशी शीमा द्वारा की गई थी, जिन्होंने आर्किटेक्चर और पश्चात् में लॉजिक डिजाइन में योगदान दिया। पूरी प्रकार से परिचालित 4004 की पहली डिलीवरी मार्च 1971 में बुसीकॉम को इसके 141-पीएफ प्रिंटिंग कैलकुलेटर इंजीनियरिंग प्रोटोटाइप (अब माउंटेन व्यू, कैलिफोर्निया में कंप्यूटर इतिहास संग्रहालय में प्रदर्शित) के लिए की गई थी।[4] इसकी सामान्य सेल जुलाई 1971 से प्रारंभ हुई।

फेयरचाइल्ड सेमीकंडक्टर में कार्य करते हुए फागिन द्वारा विकसित किए गए अनेक नवाचारों ने 4004 को चिप पर उत्पादित करने की अनुमति दी थी। मुख्य अवधारणा धातु के अतिरिक्त पॉलीसिलिकॉन से बने सेल्फ-अलिग्नेड गेट का उपयोग था, जिसने घटकों को साथ बहुत समीप होने और उच्च गति से कार्य करने की अनुमति दी। 4004 को संभव बनाने के लिए, फागिन ने बूटस्ट्रैप लोड भी विकसित किया था, जिसे सिलिकॉन गेट के साथ अव्यवहार्य माना जाता है, और दबे हुए संपर्क ने सिलिकॉन गेट्स को धातु के उपयोग के बिना सीधे ट्रांजिस्टर के स्रोत और नाली से जोड़ा जा सकता है। इसके साथ में, इन नवाचारों ने सर्किट घनत्व को दोगुना कर दिया, और इस प्रकार निवेश को आधा कर दिया था, जिससे चिप में 2,300 ट्रांजिस्टर सम्मिलित हो गए और एल्यूमीनियम गेट्स के साथ पिछली एमओएस तकनीक का उपयोग करने वाले डिजाइनों की तुलना में पांच गुना तीव्र हो गए।

4004 डिज़ाइन को पश्चात् में 1974 में फागिन द्वारा इंटेल 4040 के रूप में सुधारा गया। और समान नामकरण के अतिरिक्त इंटेल 8008 और इंटेल 8080 असंबंधित डिज़ाइन थे।

इतिहास

मूल अवधारणा

अप्रैल 1969 में, बिजनेसकॉम ने इलेक्ट्रॉनिक कैलकुलेटर के लिए नया डिज़ाइन तैयार करने के लिए इंटेल से संपर्क किया। उन्होंने अपना डिज़ाइन 1965 के ओलिवेटी प्रोग्राम 101 की आर्किटेक्चर पर आधारित किया था, जो विश्व के पहले टेबलटॉप प्रोग्राम करने योग्य कैलकुलेटर में से है।[5][6] इसका मुख्य अंतर यह था कि बुसीकॉम डिजाइन 101 में महंगे विलंब-लाइन मेमोरी या मैग्नेटोस्ट्रिक्टिव देरी लाइनों के अतिरिक्त भिन्न-भिन्न घटकों से भरे मुद्रित सर्किट बोर्डों और स्मृति के लिए ठोस-स्थान शिफ्ट का रजिस्टरों को परिवर्तित करने के लिए एकीकृत सर्किट का उपयोग करता हैं।

प्रथम के कैलकुलेटर डिजाइनों के विपरीत, बुसिकॉम ने सामान्य-उद्देश्य प्रोसेसर अवधारणा विकसित की थी, जिसका लक्ष्य इसे कम-अंत वाले डेस्कटॉप प्रिंटिंग कैलकुलेटर में प्रस्तुत करना था, और फिर कैश - रजिस्टर और स्वचालित टेलर मशीन जैसी अन्य भूमिकाओं के लिए उसी डिज़ाइन का उपयोग करना था। कंपनी ने पहले ही ट्रांजिस्टर-ट्रांजिस्टर लॉजिक लघु मानदंड पर एकीकरण लॉजिकआई सीका उपयोग करके कैलकुलेटर का उत्पादन किया था और इंटेल की मध्यम स्तर का एकीकरण (एमएसआई) तकनीकों का उपयोग करके इंटेल को चिप की संख्या कम करने में रुचि थी।[7]

इंटेल ने दो कंपनियों के मध्य संपर्क के रूप में कार्य करने के लिए वर्तमान में नियुक्त मार्सियन हॉफ, कर्मचारी संख्या 12 को नियुक्त किया। जून के अंत में, बिजनेसकॉम के तीन इंजीनियरों, मासाटोशी शिमा और उनके सहयोगियों मसुदा और ताकायामा ने डिजाइन प्रस्तुत करने के लिए इंटेल की यात्रा की थी। चूँकि उन्हें केवल इंजीनियरों के साथ संपर्क करने के लिए नियुक्त किया गया था, हॉफ ने अवधारणा का अध्ययन करना प्रारंभ किया। उनके प्रारंभिक प्रस्ताव में सात आईसी, कार्यक्रम नियंत्रण, अंकगणित इकाई (आईएनएस), समय, कार्यक्रम रोम, अस्थायी मेमोरी, प्रिंटर नियंत्रक और इनपुट/आउटपुट नियंत्रण के लिए शिफ्ट रजिस्टर थे।[8]

हॉफ चिंतित हो गए कि चिप्स की संख्या और उनके मध्य आवश्यक अंतर्संबंधों के कारण बुसिकॉम के मूल्य लक्ष्यों को पूरा करना असंभव हो जाएगा। चिप्स को मिलाने से सम्मिश्रता और निवेश कम होगी। उन्हें इस बात की भी चिंता थी कि अभी भी लघु इंटेल के समीप ही समय में सात भिन्न-भिन्न चिप्स बनाने के लिए पर्याप्त डिज़ाइन कर्मचारी नहीं होंगे। उन्होंने ऊपरी प्रबंधन के साथ इन चिंताओं को उठाया, और बॉब नोयस, सीईओ, ने हॉफ से कहा कि यदि यह व्यवहार्य प्रतीत होता है तब वह भिन्न दृष्टिकोण का समर्थन करेंगे।[8]

सरलीकृत डिजाइन

बिजनेसकॉम डिज़ाइन में प्रमुख अवधारणा यह थी कि प्रोग्राम नियंत्रण और आईएनएस विशेष रूप से कैलकुलेटर बाज़ार पर लक्षित नहीं थे, यह रोममें प्रोग्राम था जिसने इसे कैलकुलेटर में परिवर्तन कर दिया। मूल विचार यह था कि कंपनी ही चिप्स का उपयोग भिन्न-भिन्न मात्रा में शिफ्ट रजिस्टर रैम और प्रोग्राम रोम के साथ गणना मशीनों की श्रृंखला के उत्पादन के लिए कर सकती है। हॉफ इस बात से चकित थे कि बुसिकॉम के निर्देश सेट आर्किटेक्चर का सामान्य-उद्देश्य वाले कंप्यूटरों से कितना मेल खाता है। उन्होंने इस बात पर विचार करना प्रारंभ किया कि क्या वास्तव में सामान्य-उद्देश्य वाले प्रोसेसर को इतना सस्ता बनाया जा सकता है कि उसे कैलकुलेटर में प्रयोग किया जा सकता है।[9] जब इसके पश्चात् उनसे पूछा गया कि उन्हें पहले माइक्रोप्रोसेसर की आर्किटेक्चर के लिए विचार कहां से मिले, तब हॉफ ने बताया कि ब्रिटिश ट्रैक्टर कंपनी, प्लेसी,[10] स्टैनफोर्ड को मिनीकंप्यूटर दान किया था, और जब वह वहां थे तब उन्होंने इसके साथ खेला था। तदाशी सासाकी (इंजीनियर) ने कैलकुलेटर को चार भागों में विभाजित करने के विचार का श्रेय नारा महिला कॉलेज की अज्ञात महिला को दिया था, जो इंटेल के साथ अपनी पहली बैठक से पहले जापान में आयोजित विचार-मंथन बैठक में उपस्थित थी।[11]

एक और विकास जिसने इस डिज़ाइन को व्यावहारिक बनाने की अनुमति दी, वह इंटेल का सबसे प्रारंभिक गतिशील रैम (डी रैम) चिप्स पर कार्य था। उस समय शिफ्ट रजिस्टर केवल कम निवेश वाले पढ़ने और लिखने वाले मेमोरी उपकरणों में से थे। वह रैंडम एक्सेस की अनुमति नहीं देते हैं, इसके अतिरिक्त, प्रत्येक घड़ी पल्स के साथ वह संग्रहीत डेटा को कोशिकाओं की श्रृंखला के साथ सेल में ले जाते हैं। किसी दिए गए डेटा को पुनर्प्राप्त करने का समय, उदाहरण के लिए बाइट, घड़ी की गति और श्रृंखला में कोशिकाओं की संख्या का कार्य है। यदि प्रोसेसर को रजिस्टर के माध्यम से प्रत्येक बिट के चक्र के लिए प्रतीक्षा करना पड़ता है तब परिणाम प्रभावी गति व्यावहारिक होने के लिए बहुत कम होगी। दूसरी ओर, डी रैम ने अपने द्वारा संग्रहीत किसी भी डेटा को रैंडम एक्सेस की अनुमति दी थी, जबकि इसकी क्षमता लगभग दोगुनी थी और इस प्रकार यह कम मूल्यवान था।[9]

अंत में, हॉफ ने देखा कि प्रोग्राम कंट्रोल चिप की अधिकांश सम्मिश्रता प्रत्येक निर्देश के भिन्न-भिन्न प्रयुक्त होने के कारण थी। उन्होंने सुझाव दिया कि चिप इसके अतिरिक्त उपनेमका कॉल का समर्थन करता है और निर्देश जहां संभव हो उपनेमका के रूप में प्रयुक्त किया जाना चाहिए। एप्लिकेशन ने स्वाभाविक रूप से 4-बिट डिज़ाइन का सुझाव दिया, क्योंकि यह कैलकुलेटर द्वारा उपयोग किए जाने वाले बाइनरी कोडेड दशमलव (बीसीडी) मानों के सीधे हेरफेर की अनुमति देता है। हॉफ ने जुलाई और अगस्त 1969 तक समग्र डिजाइन अवधारणा पर कार्य किया था, किन्तु पाया कि बुसिकॉम के अधिकारी उनके प्रस्ताव में रुचि नहीं ले रहे थे।[9]

मेजर जॉइन

हॉफ के लिए अज्ञात, बुसिकॉम टीम उनके प्रस्ताव में अत्यधिकरूचि ले रही थी। चूँकि, अनेक विशिष्ट उद्देश्य थे जिनके बारे में वह चिंतित थे। प्रमुख उद्देश्य यह था कि दशमलव एडजस्टमेंट और कीबोर्ड हैंडलिंग जैसे कुछ रूटीन सबरूटीन्स के रूप में प्रयुक्त होने पर बड़ी मात्रा में रोम स्पेस का उपयोग करेंगे। दूसरा यह था कि डिज़ाइन में किसी प्रकार की अवरोध नहीं था इसलिए वास्तविक समय की घटनाओं से निपटना कठिन होगा। अंत में, 4-बिट बीसीडी के रूप में संख्याओं को संग्रहीत करने के लिए साइन और दशमलव स्थान को स्टोर करने के लिए अतिरिक्त मेमोरी की आवश्यकता होती हैं।[12]

सितंबर 1969 में, स्टेनली मेजर फेयरचाइल्ड से इंटेल में सम्मिलित हुए। हॉफ और मजोर शीघ्र ही बुसिकॉम चिंताओं के समाधान के साथ सामने आए। उपनेमकाओं की सम्मिश्रता को संबोधित करने के लिए, मूल रूप से बाइट मैकबुक और सम्मिश्र डिको विचार सर्किटरी का उपयोग करके बुसिकॉम के डिजाइन का समाधान किया गया, मजोर ने 20-बाइट लंबा इंटरप्रेटर (कंप्यूटिंग) विकसित किया जो समान मैक्रोइन्स्ट्रक्शन को निष्पादित करता था। शिमा ने नया व्यवधान जोड़ने का सुझाव दिया जो पिन द्वारा ट्रिगर किया जाएगा, जिससे कीबोर्ड को बाधित करने की अनुमति मिलेगी। उन्होंने एक्युमुलेटर (कंप्यूटिंग) को रिक्त करने के लिए ब्रांच बैक (सबरूटीन से परिवर्तित) निर्देश को भी संशोधित किया हैं।[13]

मूल्य लक्ष्यों तक पहुंचने के लिए, यह महत्वपूर्ण था कि चिप जितना संभव हो उतना छोटा हो और कम से कम संख्या में लीड का उपयोग करे। चूंकि डेटा 4-बिट्स का था और एड्रेस स्पेस 12-बिट्स (4096 बाइट्स) था, लगभग 24-पिनों से कम किसी भी चीज़ के साथ सीधी पहुंच की व्यवस्था नहीं की जा सकती थी। यह अधिक छोटा नहीं था, इसलिए डिजाइन 16-पिन दोहरे डुअल इन-लाइन पैकेज डीआईपी) लेआउट का उपयोग करेगा और 4 लाइनों के सेट के मल्टीप्लेक्सिंग का उपयोग करेगा। इसका अर्थ यह निर्दिष्ट करना था कि रोम में किस पते को आवश्यक तीन घड़ी चक्रों तक पहुंचना है, और अन्य दो इसे स्मृति से पढ़ने के लिए। 1 मेगाहर्ट्ज पर चलने से यह लगभग 80 माइक्रोसेकंड प्रति अंक पर बीसीडी मानों पर गणित करने की अनुमति देता हैं।[14]

इंटेल और बिजनेसकॉम के मध्य विचार-विमर्श का परिणाम आर्किटेक्चर था जिसने 7-चिप बिजनेसकॉम डिज़ाइन को सीपीयू, रोम, रैम और आई (इनपुट-आउटपुट) उपकरणों से बना 4-चिप Intel प्रस्ताव में घटा दिया। इस प्रकार का प्रस्ताव अक्टूबर 1969 में बुसिकॉम के अधिकारियों की विजिटिंग टीम के सामने प्रस्तुत किया गया था। वह सहमत थे कि नवीन अवधारणा उत्तम थी, और इंटेल को विकास प्रारंभ करने की अनुमति दी गई। हॉफ यह जानने के लिए चिंतित था कि अनुबंध ने डिजाइन के सभी अधिकार बुसिकॉम को सौंपे, इसके अतिरिक्त कि यह पूरी प्रकार से इंटेल के अंदर डिजाइन किया गया था। इसके पश्चात् टीम जापान के लिए रवाना हो गई, किन्तु शिमा दिसंबर तक कैलिफ़ोर्निया में रहीं,और इन्होने अनेक सबरूटीन्स का विकास किया था।[14]

फागिन ज्वाइन

एप्लिकेशन रिसर्च ग्रुप में कार्य करने वाले न तब हॉफ और न ही मजोर को वास्तविक सिलिकॉन डिजाइन करने का अनुभव था, और डिजाइन समूह पहले से ही मेमोरी उपकरणों के विकास के साथ कार्य कर रहा था। अप्रैल 1970 में, एमओएस डिजाइन समूह चलाने वाले लेस्ली एल. वदास्ज़ लेस्ली वदास्ज़ ने परियोजना को संभालने के लिए फेयरचाइल्ड सेमीकंडक्टर से फेडेरिको फागिन को कार्य पर रखा था।[15] फागिन ने पहले से ही एमओएस सिलिकॉन गेट प्रौद्योगिकी के संपूर्ण विकास और इसके साथ बने पहले वाणिज्यिक एकीकृत सर्किट (आई सी) के डिजाइन का नेतृत्व करके अपना नाम बना लिया था। नवीन तकनीक पूरे सेमीकंडक्टर मार्कोकेट को परिवर्तित वाली थी।

इंटीग्रेटेड सर्किट में ट्रांजिस्टर और रेसिस्टर्स जैसे अनेक भिन्न-भिन्न घटक होते हैं जो अंतर्निहित सिलिकॉन को डोपेंट के साथ मिलाकर उत्पादित किए जाते हैं। यह सामान्यतः चिप को रासायनिक गैस की उपस्थिति में गर्म करके पूरा किया जाता है, जो सतह में फैल जाती है। पहले, सतह पर जमा अल्युमीनियम तारों का उपयोग करके सर्किट बनाने के लिए भिन्न-भिन्न घटकों को साथ जोड़ा गया था। चूंकि एल्युमीनियम 600 डिग्री पर और सिलिकॉन 1000 डिग्री पर पिघलता है, निशानों को सामान्यतः अंतिम चरण के रूप में जमा करना पड़ता है, जो अधिकांशतः उत्पादन चक्र को सम्मिश्र बनाता है।

1967 में, बेल लैब्स ने एमओएस ट्रांजिस्टर बनाने के बारे में पेपरप्रयुक्त किया जिसमें धातु के अतिरिक्त सिलिकॉन से बने स्व-संरेखित द्वार थे। चूँकि, यह डिवाइस प्रूफ-ऑफ-कॉन्सेप्ट थे और इनका उपयोग आई सी बनाने के लिए नहीं किया जा सकता था। फागिन और टॉम क्लेन ने जिज्ञासा को लिया और विश्वसनीय आईसी बनाने के लिए आवश्यक पूरी प्रक्रिया प्रौद्योगिकी विकसित की थी। फागिन ने फेडरिको फागिन या फेयरचाइल्ड 3708 का डिज़ाइन और निर्माण भी किया था,[16] एसजीटी के साथ बनाया गया प्रथम आईसी, पहली बार 1968 के अंत में बेचा गया, और इलेक्ट्रॉनिक्स के कवर पर चित्रित किया गया (29 सितंबर 1969) है।[17] [15] सिलिकॉन गेट तकनीक ने लीकेज करंट को 100 गुना से अधिक कम कर दिया, जिससे डीरैम्स (डायनेमिक रैंडम एक्सेस मेमोरी) जैसे परिष्कृत डायनेमिक सर्किट संभव हो गए थे। इसने फाटकों के लिए उपयोग किए जाने वाले अत्यधिक डोप्ड सिलिकॉन को इंटरकनेक्शन बनाने की अनुमति दी हैं, जिससे माइक्रोप्रोसेसरों जैसे यादृच्छिक-लॉजिक आईसी के सर्किट घनत्व में अधिक सुधार हुआ हैं।

इस तकनीक का अर्थ था कि प्रक्रिया में किसी भी समय इंटरकनेक्शन किए जा सकते हैं। इससे भी महत्वपूर्ण बात यह है कि तारों को उसी उपकरण का उपयोग करके जमा किया गया था जिससे बाकी घटकों को बनाया गया था। इसका अर्थ यह था कि विभिन्न मशीन प्रकारों के मध्य लेआउट में सामान्य अंतर समाप्त हो गया था। पहले इंटरकनेक्ट को आवश्यकता से अधिक बड़ा होना पड़ता था जिससे कि यह सुनिश्चित किया जा सके कि एल्यूमीनियम सिलिकॉन घटकों को छूता है जो मशीनरी में अशुद्धियों के कारण ऑफसेट हो जाएगा। इस उद्देश्य को समाप्त करने के साथ, सर्किट को साथ बहुत समीप रखा जा सकता है, यह घटकों के घनत्व को तुरंत दोगुना कर सकता है, और इस प्रकार उनकी निवेश को उसी राशि से कम कर सकता है। इसके अतिरिक्त, एल्यूमीनियम तारों ने कैपेसिटर के रूप में कार्य किया जो सिग्नल की गति को सीमित करता था; इन्हें हटाने से चिप्स तीव्र गति से चलने लगे।[18][19]

इंटेल में, फागिन ने इस सेल्फ-अलिग्नेड गेट प्रक्रिया का उपयोग करके नए प्रोसेसर का डिज़ाइन प्रारंभ किया हैं। फागिन के इंटेल कंपनी में सम्मिलित होने के कुछ दिनों पश्चात् ही शिमा जापान से आ गईं। उन्हें यह जानकर निराशा हुई कि दिसंबर में उनके जाने के पश्चात् से परियोजना पर कोई कार्य नहीं हुआ है, और अपनी चिंता व्यक्त की कि मूल कार्यक्रम अब असंभव था। फागिन ने हर दिन रात में अच्छी प्रकार से कार्य करने का जवाब दिया, और शिमा सहायता करने के लिए और छह महीने तक रुकी रही। आवश्यक सर्किट घनत्व तक पहुंचने के लिए अतिरिक्त अग्रिमों की आवश्यकता थी। इन अग्रिमों में से दबे हुए संपर्कों का उपयोग था [20][21] इसने सिलिकॉन कनेक्टिंग तारों को सीधे घटकों से जोड़ने की अनुमति दी थी। और यह पता लगा रहा था कि मास्किंग चरणों में से के हिस्से के रूप में सिलिकॉन गेट के साथ बूटस्ट्रैप लोड कैसे जोड़ा जाए,[22] प्रसंस्करण से चरण को समाप्त करना।[15] फागिन द्वारा इन दो नवाचारों के बिना, हॉफ की आर्किटेक्चर को ही चिप में साकार नहीं किया जा सकता था।

उत्पादन में

उस समय इंटेल की चिप-नामकरण योजना प्रत्येक घटक के लिए चार अंकों की संख्या का उपयोग करती थी। प्रथम अंक उपयोग की गई प्रक्रिया प्रौद्योगिकी को इंगित करता है, दूसरा अंक सामान्य कार्य को इंगित करता है, और अंतिम दो अंक उस घटक प्रकार के विकास में अनुक्रमिक संख्या निर्दिष्ट करते हैं। इस परिपाटी का उपयोग करते हुए, चिप्स को 1302, 1105, 1507, और 1202 के रूप में जाना जाता था। फागिन ने अनुभव किया कि यह इस तथ्य को अस्पष्ट कर देगा कि उन्होंने सुसंगत सेट का गठन किया, और उन्हें 4000 वर्ग के रूप में नाम देने का निर्णय किया हैं।[23] चार चिप्स निम्नलिखित थे: 4001, 256-बाइट 4-बिट रोम; 4002, डीआरएएम चार 20-निबल रजिस्टरों के साथ; 4003, I/O सीरियल और समानांतर आउटपुट के साथ 10-बिट स्टैटिक शिफ्ट रजिस्टर के साथ; और 4004 सीपीयू थे । पूर्णता से विस्तारित सिस्टम कुल 4 kB रोम के लिए 16 4001, रैम के कुल 1,280 निबल्स (640) बाइट्स के लिए 16 4002 और 4003 की असीमित संख्या का समर्थन कर सकती है। यह 4003 4001 पर प्रोग्राम करने योग्य इनपुट और आउटपुट पिन से जुड़े थे और 4002 पर आउटपुट पिन से सीधे सीपीयू से नहीं जुड़े थे। [8]

डिजाइन पूरा होने के साथ, शिमा कैलकुलेटर के प्रोटोटाइप का निर्माण प्रारंभ करने के लिए जापान लौट आई थी। 4001 के पहले वेफर्स को अक्टूबर 1970 में संसाधित किया गया था,[15] इसके पश्चात् नवंबर में 4003 और 4002 आए। 4002 सामान्य समस्या प्रमाणित हुई जिसे सरलता से ठीक कर लिया गया। पहले 4004 दिसंबर के अंत में पहुंचे, और यह पूर्णता से गैर-कार्यात्मक थे। चिप की जांच करते हुए फागिन ने पाया कि उतर-संपर्क निर्माण चरण को छोड़ दिया गया था। दूसरा रन जनवरी 1971 में गढ़ा गया और 4004 ने दो छोटी समस्याओं को छोड़कर पूरी प्रकार से कार्य किया हैं।

शिमा के आते ही फागिन इन चिप्स के प्रतिरूप भेज रहे थे। अप्रैल में, उन्हें पता चला कि कैलकुलेटर प्रोटोटाइप प्रारंभ था। उस महीने के पश्चात् में, शिमा ने इंटेल को 4001 रोम के लिए अंतिम मास्क भेजा, डिजाइन अब पूरा हो गया था। इसमें 4004, दो 4002, तीन 4003 और चार 4001 चिप्स सम्मिलित थे। अतिरिक्त 4001 ने वैकल्पिक वर्गमूल फलन प्रदान किया। फागिन को 4001 में निराशाजनक समस्या मिलने के पश्चात् अंतिम परिवर्तन जोड़ा गया, जो केवल तब हुआ जब चिप्स गर्म थे। नया रजिस्टर डिकोविचार सर्किट जोड़ना फागिन का समाधान था। 4002 में भी यही समस्या देखी गई थी और उसी समाधान का उपयोग किया गया था। अगस्त 1971 में मात्रा में उत्पादन प्रारंभ हुआ था।[24]

4004 मार्केटिंग

4004 का मार्केटिंग शिमा को कॉल के समय, फागिन को पता चला कि बुसिकॉम वित्तीय कठिनाई में था और यदि चिप की कीमत कम नहीं की गई तब वह विफल हो जाएगा। फागिन ने नोयस को विशिष्टता समझौते से इंटेल को मुक्त करने के बदले में कीमत कम करने के लिए राजी किया। मई 1971 में बिजनेसकॉम ने इस शर्त पर सहमति व्यक्त की कि इसका उपयोग किसी अन्य कैलकुलेटर परियोजना के लिए नहीं किया जाएगा और इंटेल उनकी $60,000 की विकास निवेश चुकाएगा।[24] मार्केटिंग फोकस के इस परिवर्तन के साथ चिप वर्ग का नाम बदलकर एमसीएस-4 कर दिया गया, माइक्रो कंप्यूटर सिस्टम, 4-बिट के लिए छोटा होता हैं।[23]

इंटेल प्रबंधन को संदेह था कि उनकी सेल टीम अपने ग्राहकों को उत्पाद के बारे में बता सकती है। जैसा कि इंटेल अब मेमोरी मार्केट में सफल था, वह चिंतित थे कि 4004 मार्केट को भ्रमित कर सकता है और इसे विज्ञापित करने में संकोच कर रहा था।[24] उन्हें विचार था कि वर्तमान इंटेल ग्राहक नए उत्पाद को प्रतियोगिता के रूप में देख सकते हैं, इसके अतिरिक्त प्रतिस्पर्धियों से मेमोरी खरीद सकते हैं।[25] हॉफ और मेजर भी चिंतित हैं कि डिजाइन की सीमाएं उन उपयोगकर्ताओं के लिए कम अनुभव होंगा जो उस समय मार्केट में प्रवेश करने वाले नए 16-बिट मिनी कंप्यूटर के प्रवृत्त थे।[26]

1971 की गर्मियों में यह सब परिवर्तन गया, जब टेक्सास इंस्ट्रूमेंट्स, के पूर्व एड गेलबैक ने मार्केटिंग विभाग संभाला और तुरंत सार्वजनिक रूप से उत्पाद की घोषणा करने की योजना प्रारंभ की हैं।[26] यह नवंबर 1971 में हुआ जब इंटेल ने एकीकृत इलेक्ट्रॉनिक्स के नए युग की घोषणा करते हुए विज्ञापन चलाए,[27] तब यह पहली बार इलेक्ट्रॉनिक न्यूज़ के 15 नवंबर संस्करण में दिखाई दे रहा है।[28]

दि 8008

4004 सामान्य उपयोग के लिए उपलब्ध प्रथम कमर्शियल माइक्रोप्रोसेसर बन गया[lower-alpha 1] इसमें प्रायः स्थिति नहीं थी।[26]

दिसंबर 1969 में, कंप्यूटर टर्मिनल कॉरपोरेशन (सीटीसी) द्वारा इंटेल से संपर्क किया गया था जिससे कि वह जिस कंप्यूटर टर्मिनल को डिजाइन कर रहे थे, उसके लिए कस्टम बाइपोलर मेमोरी चिप, डेटाप्वाइंट 2200 का उत्पादन करें। मेज़र और हॉफ ने अपने सीपीयू डिजाइन पर विचार किया और निष्कर्ष निकाला कि यह इससे अधिक सम्मिश्र नहीं है। 4004, और इसे सिंगल-चिप 8-बिट सीपीयू के रूप में कार्यान्वित किया जा सकता है। [14] फ़ागिन को नियुक्त करने से कुछ सप्ताह पूर्व, मार्च 1970 में इंटेल ने 8008 को डिज़ाइन करने के लिए हैल फ़ीनी को नियुक्त किया था, जिसे उस समय इंटेल के नामकरण परंपरा के अनुसार 1201 कहा जाता था। चूँकि, सीटीसी ने प्रारंभ में अपने सीपीयू के पारंपरिक टीटीएल कार्यान्वयन के साथ आगे बढ़ने का निर्णय किया और परियोजना को प्राथमिकता में कम कर दिया गया। फ़ीनी को अन्य परियोजनाओं का काम सौंपा गया और अंततः उन्होंने 4000 फ़ैमिली चिप्स के परीक्षण में फ़ैगिन की सहायता की थी।[29]

जनवरी 1971 में, फ़ेनी को फ़ेगिन की देखरेख में 1201 में वापस सौंप दिया गया और मार्च 1972 में उत्पादन चिप्स उपलब्ध हो गए। मई में, हॉफ़ और मेज़र संयुक्त स्थानअमेरिका के आस पास दो सीपीयू डिज़ाइन प्रस्तुत करने के लिए स्पीकिंग टूर पर गए। दो डिज़ाइनों के मध्य ट्रेडऑफ़ यह था कि 4004 और इसकी मेमोरी और I/O चिप्स के साथ पूर्ण कंप्यूटर सिस्टम बनाना बहुत सरल था जबकि 8008 अधिक स्मूथ था, इसमें 16 kB का बड़ा एड्रेस स्पेस था, और इसमें अधिक निर्देश दिए गए थे। इसमें महत्वपूर्ण अंतर यह है कि जहां न्यूनतम 4004 सिस्टम केवल दो चिप्स, 4004 और 4001 (256-बाइट रोम) का उपयोग करके बनाया जा सकता है, वहीं 8008 को मेमोरी और आई/ओ कार्यों के साथ इंटरफेस करने के लिए कम से कम 20 अतिरिक्त टीटीएल घटकों की आवश्यकता होती हैं।[30]

दो डिजाइनों ने स्वयं को भिन्न-भिन्न भूमिकाओं में प्रयोग किया था। 4004 का उपयोग वहां किया गया था जहां कार्यान्वयन की निवेश की प्रमुख चिंता थी, और [[माइक्रोवेव ओवन]] या ट्रैफिक लाइट और इसी प्रकार की भूमिकाओं जैसे अनुप्रयोगों के लिए एम्बेडेड नियंत्रकों में व्यापक रूप से उपयोग किया जाने लगा था। इसके अतिरिक्त 8008 ने स्वयं को अधिकतर उपयोगकर्ता-प्रोग्राम करने योग्य अनुप्रयोगों में प्रयोग किया हैं, जैसे कि कंप्यूटर टर्मिनल, माइक्रो कंप्यूटर और इसी प्रकार की भूमिकाएं हैं। कार्यक्षमता में यह विभाजन आज तक बना हुआ है, जिसमें पूर्व को माइक्रोकंट्रोलर के रूप में जाना जाता है।[30]

समकालीन सीपीयू चिप्स

सामान्यता उसी समय तीन अन्य सीपीयू चिप डिजाइनों का उत्पादन किया गया: चार-चरण सिस्टम AL1, 1969 में किया गया; एमपी944, 1970 में पूरा हुआ और F-14 टॉमकैट फाइटर जेट में प्रयोग किया गया; और टेक्सास इंस्ट्रूमेंट्स टीएमएस-0100 चिप, 17 सितंबर 1971 को घोषित की गई। एमपी944 एकल प्रोसेसर इकाई बनाने वाली छह चिप्स का संग्रह था। टीएमएस0100 चिप को मूल पदनाम टीएमएस1802NC के साथ "चिप पर कैलकुलेटर" के रूप में प्रस्तुत किया गया था।[31] इस चिप में बहुत ही प्राचीन सीपीयू होता है और इसका उपयोग केवल विभिन्न सरल चार-फ़ंक्शन कैलकुलेटर को प्रयुक्त करने के लिए किया जा सकता है। यह 1974 में प्रस्तुत किए गए टीएमएस1000 का अग्रदूत है, जिसे प्रथम माइक्रोकंट्रोलर माना जाता है- अर्थात, चिप पर कंप्यूटर जिसमें न केवल सीपीयू होता है, किंतु रोम, रैम और आई / ओ फ़ंक्शन भी होते हैं।[32] इंटेल द्वारा विकसित चार चिप्स का एमसीएस-4 वर्ग, जिनमें से 4004 सीपीयू या माइक्रोप्रोसेसर है, सिंगल-चिप टीएमएस1000 की तुलना में कहीं अधिक बहुमुखी और शक्तिशाली था, जिससे विभिन्न अनुप्रयोगों के लिए विभिन्न प्रकार के लघु कंप्यूटरों का निर्माण किया जा सकता था।

ज़िलॉग, पहली कंपनी जो पूरी तरह से माइक्रोप्रोसेसरों और माइक्रोकंट्रोलर्स को समर्पित थी, 1974 के अंत में फेडेरिको फागिन और यह राल्फ अनगरमैन द्वारा प्रारंभ किया गया था।[33][34]

टिप्पणी: यदि "माइक्रोप्रोसेसर" शब्द का उपयोग एकल चिप में एकीकृत सामान्य-उद्देश्य वाले सीपीयू को निर्दिष्ट करने के लिए किया जाता है, तब 4004 से पहले उपस्थित तथाकथित माइक्रोप्रोसेसर चिप्स में से कोई भी उस नाम के योग्य नहीं है।

विवरण

4004 12 mm2 die[36] पर 10 माइक्रोन प्रक्रिया सिलिकॉन-गेट एन्हांसमेंट-लोड पीएमओएस लॉजिक तकनीक का उपयोग करता है और प्रति सेकंड लगभग 92000 निर्देश प्रति सेकंड; निष्पादित कर सकता है; एकल निर्देश चक्र 10.8 माइक्रोसेकंड.[37] का होता है। मूल क्लॉक रेट डिज़ाइन लक्ष्य 1 मेगाहर्ट्ज था, जो आईबीएम 1620 मॉडल I के समान था। इंटेल 4004 को रूबीलिथ फोटो की बड़ी शीट पर 500x आवर्धन पर भौतिक रूप से प्रत्येक पैटर्न को काटकर उत्पादित मास्क का उपयोग करके बनाया गया था, और इसकी पुनरावृत्ति करते हुए, वर्तमान कंप्यूटर ग्राफिक डिज़ाइन क्षमताओं द्वारा अप्रचलित प्रक्रिया की पुनरावृत्ति की गई था।[38]

उत्पादित चिप्स के परीक्षण के उद्देश्य से, फागिन ने एमसीएस-4 वर्ग के सिलिकॉन वेफर (इलेक्ट्रॉनिक्स) के लिए परीक्षक विकसित किया जो स्वयं 4004 चिप द्वारा संचालित था। परीक्षक ने प्रबंधन के लिए प्रमाण के रूप में भी कार्य किया कि इंटेल 4004 माइक्रोप्रोसेसर का उपयोग न केवल कैलकुलेटर जैसे उत्पादों में किया जा सकता है, किंतु नियंत्रण अनुप्रयोगों के लिए भी इसका उपयोग किया जा सकता है।[39]

4004 में मेमोरी-चिप चयन और I/O के प्रत्यक्ष निम्न-स्तरीय नियंत्रण के लिए कार्य सम्मिलित हैं, जिन्हें सामान्यतः माइक्रोप्रोसेसर द्वारा नियंत्रित नहीं किया जाता है; चूँकि, इसकी कार्यक्षमता इस सीमा में सीमित है कि यह रैम से कोड निष्पादित नहीं कर सकता है और रोम में जो भी निर्देश दिए गए हैं, या स्वतंत्र रूप से लोड की गई रैम रोम के रूप में काम करती है) तक सीमित है - किसी भी स्थिति में, प्रोसेसर स्वयं डेटा लिखने या स्थानांतरित करने में असमर्थ है। निष्पादन योग्य मेमोरी स्पेस)। रैम और रोम भागों के चिप्स भी उनके प्राथमिक मेमोरी फ़ंक्शन के साथ I/O फ़ंक्शंस के एकीकरण में असामान्य हैं। इस विभाजन ने एमसीएस-4 सिस्टम में न्यूनतम भाग संख्या को महत्वपूर्ण रूप से कम कर दिया, किन्तु अपेक्षाकृत उच्च-स्तरीय डेटा-स्थानांतरण निर्देशों को स्वीकार करने, डीकोड करने और निष्पादित करने के लिए मेमोरी चिप्स पर निश्चित मात्रा में प्रोसेसर जैसे लॉजिक को सम्मिलित करने की आवश्यकता थी।

4004 सिस्टम के लिए मानक व्यवस्था 16 × 4001 रोमचिप्स (एकल बैंक में) और 16 × 4002 रैम चिप्स (चार के चार बैंकों में) तक कुछ भी है, जो इसके साथ 4 KB प्रोग्राम स्टोरेज, 1024 + 256 निबल्स प्रदान करते हैं। यह डेटा/स्थिति संग्रहण, प्लस 64 आउटपुट और 64 इनपुट/आउटपुट बाह्य डेटा/नियंत्रण रेखाएं (जो स्वयं को संचालित करने के लिए उपयोग की जा सकती हैं, उदाहरण के लिए 4003)। चूँकि इंटेल का एमसीएस-4 प्रलेखन, प्रमाणित करता है कि 48 रोम और रैम चिप्स (192 बाहरी नियंत्रण रेखा तक प्रदान करना) को"किसी भी संयोजन में" 4004 साधारण गेटिंग हार्डवेयर के साथ से जोड़ा जा सकता है, किन्तु इसके बारे में कोई और विवरण या उदाहरण देने से अस्वीकार करता है। यह वास्तव में कैसे प्राप्त किया जाएगा। इसका विवरण या उदाहरण नही दिया गया हैं।

तकनीकी विनिर्देश

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PC3 | कॉल स्तर 3 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|}

- अधिकतम क्लॉक रेट 740 किलोहर्ट्ज है। 971 की आरंभिक रिलीज़ पर 4004 की यह अधिकतम क्लॉक रेटिंग थी।[lower-alpha 2]

- निर्देश चक्र समय: न्यूनतम 10.8 μs[37](प्रति मशीन चक्र 8 घड़ी चक्र) हैं।

- निर्देश निष्पादन समय 1 या 2 मशीन चक्र (10.8 या 21.6 μs), 46250 को 92500 निर्देश प्रति सेकंड होता हैं।

- दो 8-अंकीय दशमलव संख्याएँ (32 बिट प्रत्येक, 4-बिट बीसीडी अंक मानकर) जोड़ने पर प्रमाणित किया गया 850 μs, या लगभग 79 मशीन चक्र (632 क्लॉक टिक), औसतन 10 चक्र (80 टिक) से कम का होता है। प्रति अंक जोड़ी और 1176 × 8-अंकीय जोड़ प्रति सेकंड की परिचालन गति [lower-alpha 3] करती हैं।

- भिन्न कार्यक्रम और डेटा संग्रहण हैं।चूँकि हार्वर्ड आर्किटेक्चर डिज़ाइन के विपरीत, हालांकि, जो भिन्न-भिन्न कंप्यूटर बसों का उपयोग करते हैं, 4004, पिन काउंट डाउन रखने की आवश्यकता के साथ, स्थानांतरित करने के लिए मल्टिप्लेक्स 4-बिट बस का उपयोग करता है:

- 12-बिट एड्रेसिंग,

- 8-बिट निर्देश,

- 4-बिट डेटा शब्द (डेटा प्रकार)।

- 5120 बिट्स (640 बाइट्स के बराबर) रैम को सीधे संबोधित करने में सक्षम, 1280 4-बिट वर्णों के रूप में संग्रहीत और 1024 डेटा और 256 स्थिति वर्णों (512 और 128 बाइट्स) का प्रतिनिधित्व करने वाले समूहों में व्यवस्थित रखते हैं।[lower-alpha 4]

- सीधे संबोधित करने में सक्षम 32768 रोम के बिट्स, 4096 8-बिट शब्दों (अथार्त बाइट्स) के बराबर और व्यवस्थित होते थे।[lower-alpha 5]

- निर्देश सेट में 46 निर्देश होते हैं (जिनमें से 41 8 बिट चौड़े और 5 16 बिट चौड़े थे)।

- रजिस्टर सेट में 4 बिट्स के 16 रजिस्टर होते हैं।

- आंतरिक सबरूटीन आंतरिक स्टैक, 3 स्तर गहरा होता था।

लॉजिक लेवल्स

| सिंबल | एमआईएन. | मैक्स |

|---|---|---|

| वीएसएस–डीडी | +15 वी − 5% | +15 वी + 5% |

| वीआईएल | वीडीडी | वीएसएस − 5.5 वी |

| आईएच | वीएसएस − 1.5 वी | वीएसएस + 0.3 वी |

| वीओएल | वीएसएस − 12 वी | वीएसएस − 6.5 वी |

| वीओएच | वीएसएस − 0.5 वी | वीएसएस |

सपोर्ट चिप्स

- 4001: 256-बाइट रोम(256 8-बिट प्रोग्राम निर्देश) और बिल्ट-इन 4-बिट इनपुट/आउटपुट|I/O पोर्ट हैं। 4001 ROM+I/O चिप का उपयोग किसी सिस्टम में 4008/4009 जोड़ी के साथ नहीं किया जा सकता है।[40]

- 4002: 40-बाइट रैंडम एक्सेस मेमोरी (80 4-बिट डेटा शब्द) और बिल्ट-इन 4-बिट आउटपुट पोर्ट; चिप के रैम भाग को 20 4-बिट शब्दों के 4 रजिस्टरों में व्यवस्थित किया गया है:

- 4003: कीबोर्ड, डिस्प्ले, प्रिंटर आदि को स्कैन करने के लिए 10-बिट समानांतर आउटपुट शिफ्ट रजिस्टर होते थे।

- 4008: मानक मेमोरी चिप्स तक पहुंच के लिए 8-बिट एड्रेस लैच और बिल्ट-इन 4-बिट चिप-सिलेक्ट और आई/ओ पोर्ट हैं।

- 4009: प्रोग्राम और I/O एक्सेस कनवर्टर मानक मेमोरी और I/O चिप्स तक होते थे।

- 4269: कीबोर्ड/डिस्प्ले इंटरफेस हैं।

- 4289: मेमोरी इंटरफ़ेस (4008 और 4009 के संयुक्त कार्य) हैं।

इंटेल द्वारा वर्णित न्यूनतम सिस्टम विनिर्देश में 256-बाइट 4001 प्रोग्राम रोमके साथ 4004 सम्मिलित है; न्यूनतम-सम्मिश्रता अनुप्रयोगों में भिन्न रैम की कोई स्पष्ट आवश्यकता नहीं है, 4004 के ऑनबोर्ड इंडेक्स रजिस्टरों की बड़ी संख्या के लिए धन्यवाद, जो 16 × 4-बिट या 8 × 8-बिट वर्णों (या मिश्रण) के कार्य करने वाले रैम के बराबर का प्रतिनिधित्व करते हैं, न ही सरल इंटरफ़ेस चिप्स के लिए रोमके अंतर्निर्मित I/O लाइनों के लिए धन्यवाद। चूँकि, जैसे-जैसे परियोजना की सम्मिश्रता बढ़ती है, विभिन्न अन्य सपोर्ट चिप्स उपयोगी होने लगते हैं।

पैकेजिंग

इंटेल एमसीएस-4 लाइन के प्रोसेसर के अनेक संस्करण तैयार किए गए थे। प्रारंभिक संस्करण, सी चिह्नित (जैसे सी 4004), सिरेमिक थे और चिप्स के पीछे सफेद और भूरे रंग के ज़ेबरा पैटर्न का प्रयोग करते थे, जिन्हें अधिकांशतः ग्रे निशान कहा जाता था। चिप्स की अगली पीढ़ी सादे सफेद सिरेमिक (C भी चिह्नित) और फिर गहरे भूरे रंग के सिरेमिक (D) थे। एमसीएस-4 वर्ग के अनेक नवीनतम संस्करण भी प्लास्टिक (P) से निर्मित किए गए थे।

- Intel C4004 b.jpg

The ceramic C4004 variant without grey traces

- Intel P4004.jpg

The plastic P4004 variant

प्रयोग

माइक्रोप्रोसेसर का उपयोग करने वाला प्रथम व्यावसायिक उत्पाद बिजनेसकॉम कैलकुलेटर 141-पीएफ था। 4004 का उपयोग पहले माइक्रोप्रोसेसर-नियंत्रित पिनबॉल गेम में भी किया गया था, जो 1974 में बाली निर्माण के लिए डेव नटिंग एसोसिएट्स द्वारा निर्मित प्रोटोटाइप था।

1996 में, इसको अमेरिकी पेटेंट कार्यालय ने आधिकारिक तौर पर श्री गैरी डब्ल्यू. बून और उनके नियोक्ता, टेक्सास इंस्ट्रूमेंट्स को सिंगल-चिप माइक्रोकंट्रोलर के आविष्कारक के रूप में मान्यता दी थी, 1990 में गिल्बर्ट पी. हयात को पेटेंट अनुदान को परिवर्तित कर दिया गया था। चूँकि पेटेंट की अवधि समाप्त हो गई थी। , गिल्बर्ट हयात के साथ पिछले अनुबंधों के विवरण के आधार पर संभावित वित्तीय प्रभाव के बारे में सोचा गया था।[41] बूने/हयात पेटेंट स्थितियों के माइक्रोप्रोसेसर डिजाइनर और विशेषज्ञ गवाह निक ट्रेडेनिक के अनुसार:

यहां मेरा अनुमान हैं कि [वह] अध्ययन [मैंने पेटेंट स्थितियों का संचालन किया]. किसी व्यावसायिक उत्पाद में प्रथम माइक्रोप्रोसेसर था चार चरण सिस्टम AL1. पहला व्यावसायिक रूप से उपलब्ध ( घटक के रूप में बेचा गया) माइक्रोप्रोसेसर इंटेल का 4004 था.[42]

इसमें लोकप्रिय मिथक यह है कि पायनियर 10, सौर मंडल छोड़ने वाला प्रथम अंतरिक्ष यान, इंटेल 4004 माइक्रोप्रोसेसर का उपयोग करता है। एम्स रिसर्च सेंटर के डॉ. लैरी लैशर के अनुसार, पायनियर टीम ने 4004 का मूल्यांकन किया था, किन्तु यह निश्चित किया कि पायनियर की किसी भी परियोजना में सम्मिलित करना उस समय बहुत नया था। 2006 में कंप्यूटर इतिहास संग्रहालय के लिए व्याख्यान में फेडेरिको फागिन ने स्वयं इस काल्पनिकता को अपनाया था।[43]

लिगेसी और मान

फेडरिको फागिन ने अपने आद्याक्षरों के साथ 4004 पर हस्ताक्षर किए क्योंकि वह जानता था कि उसके सिलिकॉन गेट डिजाइन ने माइक्रोप्रोसेसर के सार को मूर्त रूप दिया हैं। पासे का कोना एफ.एफ पढ़ता है।[23]

15 नवंबर 2006 को, 4004 की 35वीं वर्षगांठ, इंटेल ने चिप की योजना, मास्क वर्क और यूजर मैनुअल प्रयुक्त करके मनाया था।[44] सही प्रकार कार्यात्मक 41 × 58 सेमी,[45] इंटेल 4004 की 130× स्केल प्रतिकृति असतत ट्रांजिस्टर का उपयोग करके बनाई गई थी और 2006 में सांता क्लारा, कैलिफ़ोर्निया, कैलिफ़ोर्निया में इंटेल संग्रहालय में प्रदर्शित की गई थी।[46]

15 अक्टूबर 2010 को, राष्ट्रपति बराक ओबामा द्वारा 4004 पर उनके अग्रणी कार्य के लिए फागिन, हॉफ और माजर को प्रौद्योगिकी और नवाचार के राष्ट्रीय पदक से सम्मानित किया गया था।[47]

यह भी देखें

- सेंट्रल एयर डेटा कंप्यूटर - प्रथम 20-बिट मिलिट्री माइक्रोप्रोसेसर जून 1970 में अमेरिकी नौसेना F-14 टॉमकैट फाइटर जेट के लिए प्रयुक्त किया गया था, इंटेल 4004 प्रयुक्त होने से लगभग 1.5 वर्ष पूर्व था

टिप्पणियाँ

- ↑ Several microprocessors had been designed or built by this point, but were not available for purchase outside the products they were part of.

- ↑ Although the early documentation states "0.75 MHz", this is at odds with the timing diagrams, which specify a minimum overall cycle time of 1350 ns (=741 kHz) and a maximum of 2010 ns (=498 kHz).

- ↑ This statistic comes from the same document as the "0.75 MHz" claim and which appears to inaccurately round off the true figures for the purposes of summary. 850 μs with a minimum 10.8 μs cycle time would in truth be 78.7 machine cycles, or roughly 629 clock ticks. As the processor is locked into an 8-tick cycle, it is more likely that this operation would take 79 or even 80 full cycles, thus 632 to 640 ticks and 853 to 864 μs (or 854 to 865 μs at a true 740 kHz), and reducing the actual execution speed to 1157–1172 (or 1156–1171) 8-digit additions per second.

- ↑ However, this could only be used as working / data memory, and was non-executable: program code could not be stored in or run from RAM, as the processor kept the two memory areas strictly segregated at the microcode level. Instruction fetching forced assertion of the ROM chip-select line (and deassertion of the RAM select lines), and the chip had no way to "write" data to anything other than an IO port whilst the ROM area was selected.

- ↑ The only part of the 4004 memory space capable of storing executable code, though also usable for general-purpose storage.

संदर्भ

- ↑ "The Life Cycle of a CPU". www.cpushack.com.

- ↑ "The 40th birthday of—maybe—the first microprocessor, the Intel 4004". 15 November 2011.

- ↑ "The Story of the Intel 4004". Intel.

- ↑ "The Intel 4004 Microprocessor and the Silicon Gate Technology: The Busicom Engineering Prototype". Intel4004.com.

- ↑ "Olivetti Programma 101 Electronic Calculator". The Old Calculator Web Museum.

technically, the machine was a programmable calculator, not a computer.

- ↑ "2008/107/1 Computer, Programma 101, and documents (3), plastic / metal / paper / electronic components, hardware architect Pier Giorgio Perotto, designed by Mario Bellini, made by Olivetti, Italy, 1965–1971". www.powerhousemuseum.com (in English). Retrieved 2016-03-20.

- ↑ Faggin et al. 1996, p. 10.

- ↑ 8.0 8.1 8.2 Faggin et al. 1996, p. 11.

- ↑ 9.0 9.1 9.2 Faggin et al. 1996, p. 12.

- ↑ Possibly he had confused the Plessey name with that of Massey Ferguson, makers of agricultural machinery.

- ↑ Aspray, William (1994-05-25). "Oral-History: Tadashi Sasaki". Interview #211 for the Center for the History of Electrical Engineering. The Institute of Electrical and Electronics Engineers, Inc. Retrieved 2013-01-02.

- ↑ Faggin et al. 1996, p. 13.

- ↑ Faggin et al. 1996, p. 14.

- ↑ 14.0 14.1 14.2 Faggin et al. 1996, p. 15.

- ↑ 15.0 15.1 15.2 15.3 Faggin et al. 1996, p. 16.

- ↑ Faggin, Federico. "A faster generation of MOS devices with low thresholds is riding the crest of the new wave, silicon-gate IC's". Retrieved 3 June 2017.