क्षेत्र प्रभाव ट्रांजिस्टर: Difference between revisions

(→लाभ) |

No edit summary |

||

| (46 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

FETs को एकध्रुवीय ट्रांजिस्टर के रूप में भी जाना जाता है, क्योंकि वे एकल-वाहक-प्रकार के | [[File:FET cross section.png|thumb|एक फील्ड-इफेक्ट ट्रांजिस्टर का क्रॉस-सेक्शनल दृश्य, स्रोत, गेट और ड्रेन टर्मिनलों को दिखाते हुए]] | ||

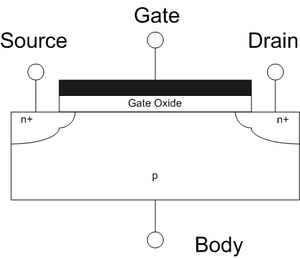

क्षेत्र प्रभाव ट्रांजिस्टर (फील्ड-इफेक्ट ट्रांजिस्टर) (FET), एक प्रकार का ट्रांजिस्टर है, जो अर्धचालक में करंट के प्रवाह को नियंत्रित करने के लिए एक विद्युत क्षेत्र का उपयोग करता है।FETS (JFETs या MOSFETs) तीन टर्मिनलों वाले उपकरण हैं: ''स्रोत, गेट और ड्रेन FETs गेट पर एक वोल्टेज को लगाकर विद्युत के प्रवाह को नियंत्रित करते हैं, जो बदले में ड्रेन और स्रोत के बीच चालकता को बदल देता है।'' | |||

FETs को एकध्रुवीय ट्रांजिस्टर के रूप में भी जाना जाता है, क्योंकि वे एकल-वाहक-प्रकार के संचालन को शामिल करते हैं। अर्थात्, FETs अपने संचालन में आवेश वाहक के रूप में इलेक्ट्रॉनों (N-चैनल) या छेद (P-चैनल) का उपयोग करते हैं। फील्ड इफेक्ट ट्रांजिस्टर कम आवृत्तियों पर बहुत उच्च इनपुट प्रतिबाधा प्रदर्शित करते हैं। सबसे व्यापक रूप से इस्तेमाल किया जाने वाला फील्ड-इफेक्ट ट्रांजिस्टर MOSFET (मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड -इफेक्ट ट्रांजिस्टर) है। | |||

== इतिहास == | == इतिहास == | ||

{{Further|अधिक जानकारी: ट्रांजिस्टर का इतिहास}} | {{Further|अधिक जानकारी: ट्रांजिस्टर का इतिहास}} | ||

[[File:Julius Edgar Lilienfeld (1881-1963).jpg|thumb|144px|जूलियस एडगर लिलिएनफेल्ड ने 1925 में एक फील्ड-इफेक्ट ट्रांजिस्टर की अवधारणा का प्रस्ताव रखा।]] | [[File:Julius Edgar Lilienfeld (1881-1963).jpg|thumb|144px|जूलियस एडगर लिलिएनफेल्ड ने 1925 में एक फील्ड-इफेक्ट ट्रांजिस्टर की अवधारणा का प्रस्ताव रखा।]] | ||

एक फील्ड-इफेक्ट ट्रांजिस्टर (FET) की अवधारणा को पहली बार 1925 में ऑस्ट्रो-हंगेरियन भौतिक विज्ञानी जूलियस एडगर लिलिएनफेल्ड द्वारा<ref>Lilienfeld, J.E. [https://pdfpiw.uspto.gov/.piw?Docid=01745175 "Method and apparatus for controlling electric current"] US Patent no. 1,745,175 (filed: 8 October 1926 ; issued: 28 January 1930).</ref> और 1934 में ऑस्कर हील द्वारा, पेटेंट कराया गया था। लेकिन वे अवधारणा के आधार पर एक व्यावहारिक अर्धचालक उपकरण बनाने में असमर्थ थे।17 साल के पेटेंट की समय सीमा समाप्त होने के | एक फील्ड-इफेक्ट ट्रांजिस्टर (FET) की अवधारणा को पहली बार 1925 में ऑस्ट्रो-हंगेरियन भौतिक विज्ञानी जूलियस एडगर लिलिएनफेल्ड द्वारा<ref>Lilienfeld, J.E. [https://pdfpiw.uspto.gov/.piw?Docid=01745175 "Method and apparatus for controlling electric current"] US Patent no. 1,745,175 (filed: 8 October 1926 ; issued: 28 January 1930).</ref> और 1934 में ऑस्कर हील द्वारा, पेटेंट कराया गया था। लेकिन वे अवधारणा के आधार पर एक व्यावहारिक अर्धचालक उपकरण बनाने में असमर्थ थे।17 साल के पेटेंट की समय सीमा समाप्त होने के बाद 1947 में बेल लैब्स में विलियम शॉक्ले के तहत काम करते हुए जॉन बार्डीन और वाल्टर हाउसर ब्रैटन द्वारा ट्रांजिस्टर प्रभाव को बाद में देखा गया और समझाया गया। शॉकली ने शुरू में एक अर्धचालक की चालकता को संशोधित करने की कोशिश करके एक कार्यशील एफईटी(FET) बनाने का प्रयास किया, लेकिन असफल रहा मुख्य रूप से सतह की अवस्थाओं, लटकने वाले बंधन, और जर्मेनियम और तांबे मिश्रित सामग्री की समस्याओं के कारण। काम करने वाले FET के निर्माण में उनकी विफलता के पीछे के रहस्यमय कारणों को समझने की कोशिश में, इसने 1947 में पॉइंट-कॉन्टैक्ट ट्रांजिस्टर का आविष्कार करने के बजाय बार्डीन और ब्रेटन को जन्म दिया, जिसके बाद 1948 में शॉक्ले के बाइपोलर जंक्शन ट्रांजिस्टर का आविष्कार किया गया।<ref name="Lee">{{cite book |last1=Lee |first1=Thomas H. |title=The Design of CMOS Radio-Frequency Integrated Circuits |date=2003 |publisher=[[Cambridge University Press]] |isbn=9781139643771 |url=https://web.stanford.edu/class/archive/ee/ee214/ee214.1032/Handouts/HO2.pdf |access-date=2019-07-20 |archive-date=2019-12-09 |archive-url=https://web.archive.org/web/20191209032130/https://web.stanford.edu/class/archive/ee/ee214/ee214.1032/Handouts/HO2.pdf |url-status=dead }}</ref><ref name="Puers">{{cite book |last1=Puers |first1=Robert |last2=Baldi |first2=Livio |last3=Voorde |first3=Marcel Van de |last4=Nooten |first4=Sebastiaan E. van |title=Nanoelectronics: Materials, Devices, Applications, 2 Volumes |date=2017 |publisher=[[John Wiley & Sons]] |isbn=9783527340538 |page=14 |url=https://books.google.com/books?id=JOqVDgAAQBAJ&pg=PA14}}</ref> | ||

सफलतापूर्वक निर्मित होने वाला पहला एफईटी (FET) उपकरण, जंक्शन फील्ड-इफेक्ट ट्रांजिस्टर (JFET) था।<ref name="Lee" />एक JFET को पहली बार 1945 में हेनरिक वेलकर द्वारा पेटेंट कराया गया था।<ref>{{cite book |title=The Physics of Semiconductors|author=Grundmann, Marius|isbn=978-3-642-13884-3 |publisher=Springer-Verlag|year=2010}}</ref> स्टेटिक इंडक्शन ट्रांजिस्टर (SIT), एक छोटे चैनल के साथ जेएफईटी का एक प्रकार जिसे जापानी इंजीनियरों जून-इची निशिज़ावा और वाई वतनबे द्वारा 1950 में आविष्कार किया गया था। 1952 में जेएफईटी पर शॉक्ले के सैद्धांतिक उपचार के बाद, एक काम करने वाले जेएफईटी का निर्माण 1953 में जॉर्ज एफ.डेसी और इयान एम. रॉस द्वारा किया गया।<ref name="sit">{{cite book|first=Jun-Ichi |last=Nishizawa|editor-first1=Roland|editor-last1=Sittig|editor-first2=P.|editor-last2=Roggwiller|publisher=Springer|chapter=Junction Field-Effect Devices|title=Semiconductor Devices for Power Conditioning|year=1982|pages=241–272|doi=10.1007/978-1-4684-7263-9_11|isbn=978-1-4684-7265-3}}</ref> | |||

<ref name="Moskowitz">{{cite book |last1=Moskowitz |first1=Sanford L. |title=Advanced Materials Innovation: Managing Global Technology in the 21st century |date=2016 |publisher=[[John Wiley & Sons]] |isbn=9780470508923 |page=168 |url=https://books.google.com/books?id=2STRDAAAQBAJ&pg=PA168}}</ref>जंक्शन ट्रांजिस्टर अपेक्षाकृत भारी उपकरण थे, जिनका एक द्रव्यमान-उत्पादन के आधार पर निर्माण करना मुश्किल था, इंसुलेटेड-गेट फील्ड-इफेक्ट ट्रांजिस्टर (IGFET) को जंक्शन ट्रांजिस्टर के संभावित विकल्प के रूप में सिद्धांतित किया गया था, लेकिन शोधकर्ता काम करने वाले IGFET का निर्माण करने में असमर्थ थे,जो बाहरी विद्युत क्षेत्र को सामग्री में प्रवेश करने से रोकते थे।<ref name="Moskowitz" />1950 के दशक के मध्य तक, शोधकर्ताओं ने बड़े पैमाने पर एफईटी अवधारणा को छोड़ दिया था और इसके बजाय बाइपोलर जंक्शन ट्रांजिस्टर (BJT) तकनीक पर ध्यान केंद्रित किया था।<ref name="triumph">{{cite web |title=The Foundation of Today's Digital World: The Triumph of the MOS Transistor |url=https://www.youtube.com/watch?v=q6fBEjf9WPw |publisher=[[Computer History Museum]] |access-date=21 July 2019 |date=13 July 2010}}</ref>MOSFET तकनीक की नींव विलियम शॉक्ले, जॉन बार्डीन और वाल्टर ब्रेटन के क्वारा रखी गई थी। शॉक्ले ने 1945 में एफईटी अवधारणा की कल्पना की, लेकिन वह एक कार्यशील उपकरण बनाने में असमर्थ थे। अगले साल बार्डेन ने सतही अवस्थाओं के संदर्भ में अपनी विफलता के बारे में बताया। बार्डेन ने अर्धचालक पर सतह अवस्थाओं के सिद्धांत को लागू किया (सतह अवस्थाओं पर पिछला काम 1939 में शॉक्ले द्वारा और 1932 में इगोर टैम द्वारा किया गया था) और देखा कि अर्धचालक सतह पर खींचे गए अतिरिक्त इलेक्ट्रॉनों के कारण बाहरी क्षेत्र सतह पर अवरुद्ध हो गया था। इलेक्ट्रॉन उन स्थानीयकृत अवस्थाओं में फंस जाते हैं जो एक व्युत्क्रम परत बनाते हैं। बार्डेन की परिकल्पना ने सतह भौतिकी के जन्म को चिह्नित किया। बार्डीन ने तब अर्धचालक की बहुत पतली परत के बजाय एक व्युत्क्रम परत का उपयोग करने का फैसला किया, जिसकी शॉक्ले ने अपने एफईटी डिजाइनों में कल्पना की थी। उनके सिद्धांत के आधार पर, 1948 में बार्डीन ने MOSFET के पूर्वज इंसुलेटेड-गेट एफईटी (IGFET)को एक व्युत्क्रम परत के साथ पेटेंट कराया। व्युत्क्रम परत अल्पसंख्यक वाहकों के प्रवाह को सीमित करती है, मॉड्यूलेशन और चालकता को बढा़ता है, हालांकि इसका इलेक्ट्रॉन परिवहन गेट के इन्सुलेटर या ऑक्साइड की गुणवत्ता पर निर्भर करता है। बार्डीन के पेटेंट के साथ -साथ एक व्युत्क्रम परत की अवधारणा आज सीएमओएस तकनीक का आधार बनती है। 1976 में शॉक्ले ने बार्डेन की सतह अवस्था परिकल्पना को अर्धचालक कार्यक्रम में सबसे महत्वपूर्ण अनुसंधान विचारों में से एक के रूप में वर्णित किया।<ref name="b1">{{cite book | author=Howard R. Duff | title=AIP Conference Proceedings | chapter=John Bardeen and transistor physics | date=2001 | volume=550 | pages=3–32 | doi=10.1063/1.1354371 | doi-access=free }}</ref>बार्डीन की सतह अवस्था के सिद्धांत के बाद 1947 के अंत में, रॉबर्ट गिबनी और ब्रेटन ने सतह की अवस्थाओं के प्रभावों को दूर करने के लिए धातु और अर्धचालक के बीच रखे गए इलेक्ट्रोलाइट के उपयोग का सुझाव दिया। बार्डीन ने आगे बढ़कर सुझाव दिया कि वह व्युत्क्रम परत की चालकता पर ध्यान केंद्रित करे।आगे के प्रयोगों ने उन्हें बेहतर परिणाम प्राप्त करने की उम्मीद में इलेक्ट्रोलाइट को एक ठोस ऑक्साइड परत से बदलने के लिए प्रेरित किया, उनका लक्ष्य ऑक्साइड की परत में प्रवेश करना और व्युत्क्रम परत तक पहुंचना था।हालांकि, बार्डेन ने सुझाव दिया कि वे सिलिकॉन से जर्मेनियम में आगे बढ़ते हुए इस प्रक्रिया से उनका ऑक्साइड अनजाने में धुल जाएगा। वेूलियन होडेसन का तर्क है कि ब्रेटेन और बार्डेन जर्मेनियम के बजाय सिलिकॉन के साथ काम कर रहे होते तो, फील्ड इफेक्ट ट्रांजिस्टर को बनाने में सफल नहीं होते।<ref name="b1" /><ref name="Camezind">{{cite book | author=Hans Camenzind | author-link=Hans Camenzind | title=Designing Analog Chips | date=2005 | url=http://www.designinganalogchips.com/}}</ref><ref>{{cite book | title=ULSI Science and Technology/1997 | url= https://books.google.com/books?id=I8_O1anzKpsC | date=1997 | | |||

page=43|isbn = 9781566771306}}</ref><ref>{{cite journal | author=Lillian Hoddeson | author-link=Lillian Hoddeson | title=Research on crystal rectifiers during World War II and the invention of the transistor | journal=History and Technology | date=1994 | volume=11 | issue=2 | pages=121–130 | doi=10.1080/07341519408581858}}</ref><ref>{{cite book | authors=Michael Riordan, Lillian Hoddeson | title=Crystal Fire: The Birth of the Information Age | year=1997 | isbn=9780393041248}}</ref>1950 के दशक की पहली छमाही के अंत तक बार्डीन, ब्रेटन, किंग्स्टन, मॉरिसन और अन्य के सैद्धांतिक और प्रयोगात्मक कार्य के बाद, यह पूरी तरह से स्पष्ट हो गया कि सतह अवस्था दो प्रकार की थी। सतह अवस्थाओं को समूहों और अर्धचालक/ऑक्साइड इंटरफ़ेस के साथ जुड़ा हुआ पाया गया। परिवेश से ऑक्साइड द्वारा परमाणुओं, अणुओं और आयनों के सोखने के कारण धीमी सतह की स्थिति ऑक्साइड परत के साथ जुड़ी हुई पाई गई। उत्तरार्द्ध बहुत अधिक संख्या में पाए गए थे और उनके पास बहुत अधिक विश्राम समय था। उस समय फिलो फ़ार्न्सवर्थ और अन्य परमाणु स्वच्छ अर्धचालक सतहों के उत्पादन के विभिन्न तरीकों के साथ आए थे। | |||

1955 में, कार्ल फ्रॉश और लिंकन डेरिक ने गलती से सिलिकॉन वेफर की सतह को सिलिकॉन डाइऑक्साइड की एक परत के साथ ढ़क दिया। उन्होंने दिखाया कि ऑक्साइड की परत ने कुछ डोपेंट को सिलिकॉन वेफर में रोका, जबकि दूसरों को जाने की अनुमति दी, इस प्रकार अर्धचालक सतह पर ऑक्सीकरण के निष्क्रिय प्रभाव की खोज की।1957 में, उन्होंने एक शोध पत्र प्रकाशित किया और अपने काम को सारांशित करते हुए अपनी तकनीक का पेटेंट कराया। उनके द्वारा विकसित की गई तकनीक को ऑक्साइड डिफ्यूजन मास्किंग के रूप में जाना जाता है, जिसका उपयोग बाद में MOSFET उपकरणों के निर्माण में किया जाएगा। बेल लैब्स में, फ्रॉश की तकनीक के महत्व को तुरंत महसूस किया गया था। उनके काम के परिणाम 1957 में प्रकाशित होने से पहले बीटीएल मेमो के रूप में बेल लैब्स के आसपास प्रसारित किए गए थे। शॉक्ले अर्धचालक में, शॉक्ले ने दिसंबर 1956 में जीन होर्नी सहित अपने सभी वरिष्ठ कर्मचारियों को अपने लेख के प्रीप्रिंट को प्रसारित किया था।<ref name="Moskowitz" /><ref>{{cite book | authors=Christophe Lécuyer; David C. Brook; Jay Last | title=Makers of the Microchip: A Documentary History of Fairchild Semiconductor | date=2010 | pages=62–63 | isbn=978-0262014243 | url=https://books.google.com/books?id=LaZpUpkG70QC&pg=PA62}}</ref><ref>{{cite book |last1=Claeys |first1=Cor L. |title=ULSI Process Integration III: Proceedings of the International Symposium |date=2003 |publisher=[[The Electrochemical Society]] |isbn=978-1566773768 |pages=27–30 | url=https://books.google.com/books?id=bu22JNYbE5MC&pg=PA27}}</ref>1955 में, इयान मुनरो रॉस ने एक FeFET या MFSFET के लिए पेटेंट दायर किया।इसकी संरचना एक आधुनिक दूसरे चैनल MOSFET की तरह थी, लेकिन फेरोइलेक्ट्रिक सामग्री का उपयोग ऑक्साइड के बजाय एक ढ़के हुए/इन्सुलेटर के रूप में किया गया था। सालों पहले उन्होंने इसे फ्लोटिंग गेट मोसफेट से स्मृति के रूप में कल्पना की थी। फरवरी 1957 में, जॉन वॉलमार्क ने फील्ड-इफेक्ट ट्रांजिस्टर(FET) के लिए एक पेटेंट दायर किया, जिसमें जर्मेनियम मोनोऑक्साइड का उपयोग गेट डाइइलेक्ट्रिक के रूप में किया गया था। उसी वर्ष अपने अन्य पेटेंट में, उन्होंने एक डबल गेट (FET) का वर्णन किया। मार्च 1957 में, बेल लैब्स के एक शोध वैज्ञानिक, अर्नेस्टो लैबेट ने बाद में अपनी प्रयोगशाला नोटबुक में प्रस्तावित MOSFET के समान एक उपकरण की कल्पना की, हालांकि लैबेट के उपकरण में स्पष्ट रूप से सिलिकॉन डाइऑक्साइड का उपयोग एक इन्सुलेटर के रूप में नहीं किया था।<ref>{{cite book |last1=Lojek |first1=Bo |title=History of Semiconductor Engineering |date=2007 |publisher=Springer Science & Business Media |isbn=978-3540342588 |pages=324}}</ref><ref>{{cite book | author=Stefan Ferdinand Müller | title=Development of HfO2-Based Ferroelectric Memories for Future CMOS Technology Nodes | year=2016 | isbn=9783739248943}}</ref><ref>{{cite book | authors=B.G Lowe; R.A. Sareen | title=Semiconductor X-Ray Detectors | date=2013 | isbn=9781466554016 }}</ref><ref name="Bassett22">{{cite book |last1=Bassett |first1=Ross Knox |title=To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology |date=2007 |publisher=Johns Hopkins University Press |isbn=978-0801886393 |page=22 |url=https://books.google.com/books?id=UUbB3d2UnaAC&pg=PA22}}</ref> | |||

=== मेटल-ऑक्साइड-सेमिकंडक्टर एफईटी (MOSFET) === | === मेटल-ऑक्साइड-सेमिकंडक्टर एफईटी (MOSFET) === | ||

| Line 28: | Line 27: | ||

| footer = [[Mohamed Atalla]] (left) and [[Dawon Kahng]] (right) invented the [[MOSFET]] (MOS field-effect transistor) in 1959. | | footer = [[Mohamed Atalla]] (left) and [[Dawon Kahng]] (right) invented the [[MOSFET]] (MOS field-effect transistor) in 1959. | ||

}} | }} | ||

1950 के दशक के अंत में मिस्र के इंजीनियर मोहम्मद अटला के काम से FET अनुसंधान में | 1950 के दशक के अंत में मिस्र के इंजीनियर मोहम्मद अटला के काम से FET अनुसंधान में सफलता मिली।<ref name="Puers"/>1958 में उन्होंने प्रायोगिक कार्य प्रस्तुत किया, जिसमें दिखाया गया कि स्वच्छ सिलिकॉन सतह पर पतली सिलिकॉन ऑक्साइड बढ़ने से सतह की अवस्थाएँ बेअसर हो जाती है।इसे सतही निष्क्रियता के रूप में जाना जाता है, एक ऐसी विधि जो अर्धचालक उद्योग के लिए महत्वपूर्ण हो गई क्योंकि इसने सिलिकॉन एकीकृत परिपथों के बड़े पैमाने पर उत्पादन को संभव बना दिया।<ref name="atalla">{{cite web|title=Martin Atalla in Inventors Hall of Fame, 2009|url=https://www.invent.org/inductees/martin-john-m-atalla|access-date=21 June 2013}}</ref><ref name="kahng">{{cite web |title=Dawon Kahng |url=https://www.invent.org/inductees/dawon-kahng |website=[[National Inventors Hall of Fame]] |access-date=27 June 2019}}</ref>मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर (MOSFET) का आविष्कार तब मोहम्मद अटला और दाऊन काहंग ने 1959 में किया था।<ref name="computerhistory">{{cite journal|url=https://www.computerhistory.org/siliconengine/metal-oxide-semiconductor-mos-transistor-demonstrated/|title=1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated|journal=The Silicon Engine|publisher=[[Computer History Museum]]}}</ref><ref name="Lojek">{{cite book |last1=Lojek |first1=Bo |title=History of Semiconductor Engineering |url=https://archive.org/details/historysemicondu00loje_697 |url-access=limited |date=2007 |publisher=[[Springer Science & Business Media]] |isbn=9783540342588 |pages=[https://archive.org/details/historysemicondu00loje_697/page/n327 321]–3}}</ref> MOSFET ने बड़े पैमाने पर बाइपोलर ट्रांजिस्टर और JFET दोनों का स्थान लिया<ref name="Lee"/>और डिजिटल इलेक्ट्रॉनिक विकास पर इसका गहरा प्रभाव पड़ा।<ref>{{cite journal|url=https://www.computerhistory.org/siliconengine/metal-oxide-semiconductor-mos-transistor-demonstrated/|title=960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated|journal=The Silicon Engine|publisher=[[Computer History Museum]]}}</ref><ref name="Lojek"/>इसकी उच्च मापनीयता और <ref>{{cite journal |last1=Motoyoshi |first1=M. |s2cid=29105721 |title=Through-Silicon Via (TSV) |journal=Proceedings of the IEEE |date=2009 |volume=97 |issue=1 |pages=43–48 |doi=10.1109/JPROC.2008.2007462 |issn=0018-9219}}</ref>बाइपोलर जंक्शन ट्रांजिस्टर की तुलना में बहुत कम बिजली की खपत और उच्च घनत्व के साथ<ref>{{cite news |title=Transistors Keep Moore's Law Alive |url=https://www.eetimes.com/author.asp?section_id=36&doc_id=1334068 |access-date=18 July 2019 |work=[[EETimes]] |date=12 December 2018}}</ref> MOSFET ने उच्च घनत्व वाले एकीकृत परिपथों का निर्माण करना संभव बना दिया।<ref>{{cite web |title=Who Invented the Transistor? |url=https://www.computerhistory.org/atchm/who-invented-the-transistor/ |website=[[Computer History Museum]] |date=4 December 2013 |access-date=20 July 2019}}</ref> MOSFET भी JFET की तुलना में उच्च शक्ति को संभालने में सक्षम है।<ref>{{cite book |last1=Duncan |first1=Ben |title=High Performance Audio Power Amplifiers |date=1996 |publisher=[[Elsevier]] |isbn=9780080508047 |url=https://books.google.com/books?id=-5UPyE6dcWgC&pg=PA177 |page=177}}</ref> MOSFET पहला सही मायने में कॉम्पैक्ट ट्रांजिस्टर था और व्यापक उपयोग के लिए बड़े पैमाने पर उत्पादित किया जा सकता था।<ref name="Moskowitz"/>MOSFET कंप्यूटर, इलेक्ट्रॉनिक्स<ref name="kahng"/>और संचार प्रौद्योगिकी में सामान्य प्रकार का ट्रांजिस्टर बन गया।<ref name="uspto">{{cite web |title=Remarks by Director Iancu at the 2019 International Intellectual Property Conference |url=https://www.uspto.gov/about-us/news-updates/remarks-director-iancu-2019-international-intellectual-property-conference |website=[[United States Patent and Trademark Office]] |date=June 10, 2019 |access-date=20 July 2019}}</ref> यूएस पेटेंट और ट्रेडमार्क कार्यालय ने इसे एक अभूतपूर्व आविष्कार कहा जिसने दुनिया भर में जीवन और संस्कृति को बदल दिया।<ref name="uspto"/> | ||

कॉम्प्लिमेंटरी एमओएस (CMOS), MOSFETS के लिए एक अर्धचालक उपकरण निर्माण प्रक्रिया, 1963 में फेयरचाइल्ड अर्धचालक में चिह-तांग साह और फ्रैंक वानलास द्वारा विकसित किया गया था।<ref name="computerhistory1963">{{cite web |title=1963: Complementary MOS Circuit Configuration is Invented |url=https://www.computerhistory.org/siliconengine/complementary-mos-circuit-configuration-is-invented/ |website=[[Computer History Museum]] |access-date=6 July 2019}}</ref><ref>{{US patent|3102230}}, filed in 1960, issued in 1963</ref> फ्लोटिंग-गेट MOSFET की पहली रिपोर्ट 1967 में डॉन कांग और साइमन सेज़ द्वारा बनाई गई थी।<ref>D. Kahng and S. M. Sze, "A floating gate and its application to memory devices", ''The Bell System Technical Journal'', vol. 46, no. 4, 1967, pp. 1288–1295</ref> डबल-गेट MOSFET को पहली बार 1984 में इलेक्ट्रोटेक्निकल प्रयोगशाला शोधकर्ताओं तोशीहिरो सेकिगावा और युताका हयाशी द्वारा प्रदर्शित किया गया था।<ref>{{cite book |last1=Colinge |first1=J.P. |title=FinFETs and Other Multi-Gate Transistors |date=2008 |publisher=Springer Science & Business Media |isbn=9780387717517 |page=11 |url=https://books.google.com/books?id=t1ojkCdTGEEC&pg=PA11}}</ref><ref>{{cite journal |last1=Sekigawa |first1=Toshihiro |last2=Hayashi |first2=Yutaka |title=Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate |journal=Solid-State Electronics |date=1 August 1984 |volume=27 |issue=8 |pages=827–828 |doi=10.1016/0038-1101(84)90036-4 |bibcode=1984SSEle..27..827S |issn=0038-1101}}</ref> FinFET (फिन फील्ड-इफेक्ट ट्रांजिस्टर), एक प्रकार का 3 डी नॉन-प्लानर मल्टी-गेट मोसफेट, जिसकी उत्पत्ति 1989 में हिताची सेंट्रल रिसर्च लेबोरेटरी में दीघ हिसामोटो और उनकी टीम के शोध से हुई थी।<ref>{{cite web |title=IEEE Andrew S. Grove Award Recipients |url=https://www.ieee.org/about/awards/bios/grove-recipients.html |website=[[IEEE Andrew S. Grove Award]] |publisher=[[Institute of Electrical and Electronics Engineers]] |access-date=4 July 2019}}</ref><ref>{{cite web |title=The Breakthrough Advantage for FPGAs with Tri-Gate Technology |url=https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01201-fpga-tri-gate-technology.pdf |publisher=[[Intel]] |year=2014 |access-date=4 July 2019}}</ref> | |||

== मूल जानकारी == | == मूल जानकारी == | ||

{{See also|यह भी देखें: चार्ज कैरियर § बहुसंख्यक और अल्पसंख्यक वाहक | {{See also|यह भी देखें: चार्ज कैरियर § बहुसंख्यक और अल्पसंख्यक वाहक | ||

| Line 44: | Line 41: | ||

#गेट (G), वह टर्मिनल जो चैनल चालकता को नियंत्रित करता है।वोल्टेज को जी(G) पर लागू करके, कोई भी आईडी(ID) को नियंत्रित कर सकता है। | #गेट (G), वह टर्मिनल जो चैनल चालकता को नियंत्रित करता है।वोल्टेज को जी(G) पर लागू करके, कोई भी आईडी(ID) को नियंत्रित कर सकता है। | ||

== टर्मिनलों के बारे में अधिक == | == टर्मिनलों के बारे में अधिक जानकारी == | ||

[[File:Lateral mosfet.svg|thumbnail|एन-टाइप MOSFET का क्रॉस सेक्शन]] | [[File:Lateral mosfet.svg|thumbnail|एन-टाइप MOSFET का क्रॉस सेक्शन]] | ||

सभी एफईटी(FETs) में स्रोत, ड्रेन और गेट टर्मिनल होते हैं जो BJTS के एमिटर, कलेक्टर और बेस के अनुरूप होते हैं। अधिकांश एफईटी में एक चौथा टर्मिनल होता है जिसे बॉडी, बेस, बल्क या सब्सट्रेट कहा जाता है। यह चौथा टर्मिनल ट्रांजिस्टर को संचालन में पूर्वाग्रह करने का कार्य करता है सर्किट डिजाइनों में बॉडी टर्मिनल का गैर-तुच्छ उपयोग करना दुर्लभ है, लेकिन एक एकीकृत परिपथ के भौतिक लेआउट को स्थापित करते समय इसकी उपस्थिति महत्वपूर्ण है। गेट का आकार, आरेख में लंबाई L, स्रोत और ड्रेन के बीच की दूरी | सभी एफईटी(FETs) में स्रोत, ड्रेन और गेट टर्मिनल होते हैं जो BJTS के एमिटर, कलेक्टर और बेस के अनुरूप होते हैं। अधिकांश एफईटी में एक चौथा टर्मिनल होता है जिसे बॉडी, बेस, बल्क या सब्सट्रेट कहा जाता है। यह चौथा टर्मिनल ट्रांजिस्टर को संचालन में पूर्वाग्रह करने का कार्य करता है सर्किट डिजाइनों में बॉडी टर्मिनल का गैर-तुच्छ उपयोग करना दुर्लभ है, लेकिन एक एकीकृत परिपथ के भौतिक लेआउट को स्थापित करते समय इसकी उपस्थिति महत्वपूर्ण है। गेट का आकार, आरेख में लंबाई L, स्रोत और ड्रेन के बीच की दूरी है, चौड़ाई आरेख में क्रॉस सेक्शन के लिए लंबवत दिशा में ट्रांजिस्टर का विस्तार है। 1माइक्रोन की एक गेट लंबाई, ऊपरी आवृत्ति को लगभग 5 गीगाहर्ट्ज, 0.2माइक्रोन को लगभग 30 गीगाहर्ट्ज तक सीमित करता है। | ||

टर्मिनलों के नाम उनके कार्यों को संदर्भित करते हैं। गेट टर्मिनल को एक भौतिक गेट के उद्घाटन और समापन को नियंत्रित करने के रूप में माना जा सकता है। यह गेट इलेक्ट्रॉनों को स्रोत और ड्रेन के बीच एक चैनल बनाने या समाप्त करके उनके मार्ग को प्रवाहित करने या अवरुद्ध करने की अनुमति देता है। स्रोत टर्मिनल से ड्रेन टर्मिनल की ओर इलेक्ट्रॉन-प्रवाह एक लागू वोल्टेज से प्रभावित होता है। बॉडी केवल अर्धचालक के | टर्मिनलों के नाम उनके कार्यों को संदर्भित करते हैं। गेट टर्मिनल को एक भौतिक गेट के उद्घाटन और समापन को नियंत्रित करने के रूप में माना जा सकता है। यह गेट इलेक्ट्रॉनों को स्रोत और ड्रेन के बीच एक चैनल बनाने या समाप्त करके उनके मार्ग को प्रवाहित करने या अवरुद्ध करने की अनुमति देता है। स्रोत टर्मिनल से ड्रेन टर्मिनल की ओर इलेक्ट्रॉन-प्रवाह एक लागू वोल्टेज से प्रभावित होता है। बॉडी केवल अर्धचालक के समूह को संदर्भित करता है जिसमें गेट, स्रोत और ड्रेन स्थित है। आमतौर पर बॉडी टर्मिनल FET के आधार पर, सर्किट के भीतर उच्चतम या निम्नतम वोल्टेज से जुड़ा होता है। बॉडी टर्मिनल और सोर्स टर्मिनल कभी-कभी एक साथ जुड़े होते हैं क्योंकि स्रोत अक्सर परिपथ(circuit) के भीतर उच्चतम या निम्नतम वोल्टेज से जुड़ा होता है, हालांकि एफईटी के कई उपयोग होते हैं जिनमें ऐसा विन्यास नहीं होता है, जैसे कि ट्रांसमिशन गेट और कैस्कोड सर्किट। | ||

BJTS के विपरीत, FET के विशाल बहुमत विद्युत रूप से सममित हैं। इस प्रकार स्रोत और ड्रेन टर्मिनलों को व्यावहारिक सर्किट में आपस में बदला जा सकता है जिसमें परिचालन विशेषताओं या कार्य में कोई बदलाव नहीं होता है। यह भ्रामक हो सकता है जब एफईटी योजनाबद्ध आरेखों और सर्किटों में पीछे की ओर जुड़ा हुआ प्रतीत होता है, क्योंकि एफईटी के भौतिक अभिविन्यास को अन्य कारणों से तय किया गया था, जैसे कि मुद्रित सर्किट लेआउट। | BJTS के विपरीत, FET के विशाल बहुमत विद्युत रूप से सममित हैं। इस प्रकार स्रोत और ड्रेन टर्मिनलों को व्यावहारिक सर्किट में आपस में बदला जा सकता है जिसमें परिचालन विशेषताओं या कार्य में कोई बदलाव नहीं होता है। यह भ्रामक हो सकता है जब एफईटी योजनाबद्ध आरेखों और सर्किटों में पीछे की ओर जुड़ा हुआ प्रतीत होता है, क्योंकि एफईटी के भौतिक अभिविन्यास को अन्य कारणों से तय किया गया था, जैसे कि मुद्रित सर्किट लेआउट। | ||

=== | === करंट पर गेट वोल्टेज का प्रभाव === | ||

[[File:JFET n-channel en.svg|thumb|upright=1.3|I-V विशेषताएं और एक | [[File:JFET n-channel en.svg|thumb|upright=1.3|I-V विशेषताएं और एक जेएफईटी एन-चैनल ट्रांजिस्टर का आउटपुट प्लॉट।]] | ||

[[File:Threshold formation nowatermark.gif|thumb|right|400px|दाईं ओर के लिए सिमुलेशन परिणाम: उलटा चैनल (इलेक्ट्रॉन घनत्व) और बाईं ओर का गठन: एक एन-चैनल नैनोवायर MOSFET में | [[File:Threshold formation nowatermark.gif|thumb|right|400px|दाईं ओर के लिए सिमुलेशन परिणाम: उलटा चैनल (इलेक्ट्रॉन घनत्व) और बाईं ओर का गठन: एक एन-चैनल नैनोवायर MOSFET में करंट-गेट वोल्टेज वक्र (स्थानांतरण विशेषताएँ)।ध्यान दें कि इस उपकरण के लिए थ्रेशोल्ड वोल्टेज 0.45v है।]] | ||

[[File:FET Symbols.svg|thumb|upright=1.3| | [[File:FET Symbols.svg|thumb|upright=1.3|एफईटी पारंपरिक प्रतीक प्रकार]] | ||

एफईटी गेट और सोर्स टर्मिनलों में लागू वोल्टेज | एफईटी गेट और सोर्स टर्मिनलों में लागू वोल्टेज से निर्मित और प्रभावित "प्रवाहकीय चैनल" के आकार को प्रभावित करके स्रोत से ड्रेन में इलेक्ट्रॉनों (या इलेक्ट्रॉन छेद) के प्रवाह को नियंत्रित करता है। प्रवाहकीय चैनल वह धारा है जिसके माध्यम से इलेक्ट्रॉन स्रोत से ड्रेन में प्रवाहित होते हैं। | ||

==== एन-चैनल एफईटी ==== | ==== एन-चैनल एफईटी ==== | ||

एन-चैनल "रिक्तीकरण मोड" उपकरण में, एक नकारात्मक गेट-टू-सोर्स वोल्टेज | एन-चैनल "रिक्तीकरण मोड" उपकरण में, एक नकारात्मक गेट-टू-सोर्स वोल्टेज छोटे क्षेत्र को चौड़ाई में विस्तार करने और चैनल को संकीर्ण करने, पक्षों से चैनल पर अतिक्रमण करने का कारण बनता है। यदि सक्रिय क्षेत्र चैनल को पूरी तरह से बंद करने के लिए फैलता है, तो स्रोत से नाली तक चैनल का प्रतिरोध बड़ा हो जाता है और FET प्रभावी रूप से एक स्विच की तरह बंद हो जाता है। इसे "पिंच-ऑफ" कहा जाता है और जिस वोल्टेज पर यह होता है उसे "पिंच-ऑफ वोल्टेज"कहते है। इसके विपरीत, एक सकारात्मक गेट-टू-सोर्स वोल्टेज चैनल के आकार को बढ़ाता है और इलेक्ट्रॉनों को आसानी से प्रवाहित करने की अनुमति देता है (सही आंकड़ा देखें, जब एक चालन चैनल होता है और करंट ज्यादा होता है)। | ||

एन-चैनल "वृद्धि मोड" उपकरण में एक प्रवाहकीय चैनल ट्रांजिस्टर के भीतर स्वाभाविक रूप से मौजूद नहीं होता है और जुड़ने के लिए एक सकारात्मक गेट-टू-सोर्स वोल्टेज आवश्यक है। सकारात्मक वोल्टेज बॉडी के भीतर मुक्त-अस्थायी इलेक्ट्रॉनों को गेट की ओर आकर्षित करता है, जिससे एक प्रवाहकीय चैनल बनता है। लेकिन पहले, FET के बॉडी में जोड़े गए डोपेंट आयनों का मुकाबला करने के लिए गेट के पास पर्याप्त इलेक्ट्रॉनों को आकर्षित किया जाना चाहिए यह एक ऐसा क्षेत्र बनाता है जिसमें कोई मोबाइल वाहक नहीं होता है जिसे कमी क्षेत्र कहा जाता है और जिस वोल्टेज पर ऐसा होता है, उसे FET के थ्रेशोल्ड वोल्टेज के रूप में संदर्भित किया जाता है। आगे गेट-टू-सोर्स वोल्टेज वृद्धि गेट की ओर और भी अधिक इलेक्ट्रॉनों को आकर्षित करेगी जो स्रोत से ड्रेन तक सक्रिय चैनल में सक्षम हैं, इस प्रक्रिया को इन्वर्स कहा जाता है। | |||

==== पी-चैनल एफईटी ==== | ==== पी-चैनल एफईटी ==== | ||

| Line 71: | Line 66: | ||

इसके विपरीत, एक पी-चैनल वृद्धि मोड उपकरणों में, एक प्रवाहकीय क्षेत्र मौजूद नहीं है और एक चालन चैनल उत्पन्न करने के लिए नकारात्मक वोल्टेज का उपयोग किया जाना चाहिए। | इसके विपरीत, एक पी-चैनल वृद्धि मोड उपकरणों में, एक प्रवाहकीय क्षेत्र मौजूद नहीं है और एक चालन चैनल उत्पन्न करने के लिए नकारात्मक वोल्टेज का उपयोग किया जाना चाहिए। | ||

=== चैनल पर | === चैनल पर ड्रेन-टू-सोर्स वोल्टेज का प्रभाव === | ||

गेट-टू-सोर्स वोल्टेज की तुलना में | गेट-टू-सोर्स वोल्टेज की तुलना में ड्रेन-टू-सोर्स वोल्टेज पर या तो वृद्धि- या रिक्तीकरण-मोड उपकरणों के लिए, गेट वोल्टेज को बदलने से चैनल प्रतिरोध में बदलाव आएगा और ड्रेन करंट ड्रेन वोल्टेज के लिए आनुपातिक होगा। इस मोड में FET एक चर अवरोधक की तरह काम करता है और FET को एक रैखिक मोड या ओमिक मोड में काम करने के लिए कहा जाता है।<ref> | ||

{{cite book|author=Galup-Montoro, C.|author2=Schneider, M.C.|title=MOSFET modeling for circuit analysis and design|url=https://archive.org/details/mosfetmodelingfo00schn|url-access=limited|year=2007|page=[https://archive.org/details/mosfetmodelingfo00schn/page/n107 83]|publisher=[[World Scientific]]|location=London/Singapore|isbn=978-981-256-810-6}}</ref><ref>{{cite book|author=Norbert R Malik|title=Electronic circuits: analysis, simulation, and design|year=1995|pages=315–316|publisher=Prentice Hall|location=Englewood Cliffs, NJ|isbn=978-0-02-374910-0}}</ref> | {{cite book|author=Galup-Montoro, C.|author2=Schneider, M.C.|title=MOSFET modeling for circuit analysis and design|url=https://archive.org/details/mosfetmodelingfo00schn|url-access=limited|year=2007|page=[https://archive.org/details/mosfetmodelingfo00schn/page/n107 83]|publisher=[[World Scientific]]|location=London/Singapore|isbn=978-981-256-810-6}}</ref><ref>{{cite book|author=Norbert R Malik|title=Electronic circuits: analysis, simulation, and design|year=1995|pages=315–316|publisher=Prentice Hall|location=Englewood Cliffs, NJ|isbn=978-0-02-374910-0}}</ref>यदि ड्रेन-टू-सोर्स वोल्टेज बढ़ाया जाता है, तो यह स्रोत से ड्रेन तक वोल्टेज क्षमता के एक ढाल के कारण चैनल के आकार में एक महत्वपूर्ण विषम परिवर्तन पैदा करता है। इन्वर्स क्षेत्र का आकार चैनल के ड्रेन के अंत के पास "पिंच-ऑफ" हो जाता है।यदि ड्रेन-टू-सोर्स वोल्टेज को और बढ़ाया जाता है, तो चैनल का पिंच-ऑफ पॉइंट ड्रन से स्रोत की ओर बढ़ना शुरू कर देता है।एफईटी (FET) को संतृप्ति मोड कहा जाता है,<ref> | ||

यदि ड्रेन-टू-सोर्स वोल्टेज बढ़ाया जाता है, तो यह स्रोत से | {{cite book|author1=Spencer, R.R.|author2=Ghausi, M.S.|title=Microelectronic circuits|year=2001|page=102|publisher=Pearson Education/Prentice-Hall|location=Upper Saddle River NJ|isbn=978-0-201-36183-4}}</ref> हालांकि कुछ लेखक इसे बाइपोलर ट्रांजिस्टर ऑपरेटिंग क्षेत्रों के साथ बेहतर सादृश्य के लिए इसे सक्रिय मोड के रूप में संदर्भित करते हैं।<ref> | ||

{{cite book|author1=Spencer, R.R.|author2=Ghausi, M.S.|title=Microelectronic circuits|year=2001|page=102|publisher=Pearson Education/Prentice-Hall|location=Upper Saddle River NJ|isbn=978-0-201-36183-4}}</ref> हालांकि कुछ लेखक इसे | |||

{{cite book|author1=Sedra, A. S.|author2=Smith, K.C.|title=Microelectronic circuits|url=https://archive.org/details/microelectronicc00sedr_571|url-access=limited|year=2004|edition=Fifth|page=[https://archive.org/details/microelectronicc00sedr_571/page/n581 552]|publisher=Oxford University Press|location=New York|isbn=978-0-19-514251-8}}</ref><ref name=Gray-Mayer> | {{cite book|author1=Sedra, A. S.|author2=Smith, K.C.|title=Microelectronic circuits|url=https://archive.org/details/microelectronicc00sedr_571|url-access=limited|year=2004|edition=Fifth|page=[https://archive.org/details/microelectronicc00sedr_571/page/n581 552]|publisher=Oxford University Press|location=New York|isbn=978-0-19-514251-8}}</ref><ref name=Gray-Mayer> | ||

{{cite book|author1=PR Gray|author2=PJ Hurst|author3=SH Lewis|author4=RG Meyer|title=Analysis and design of analog integrated circuits|year=2001|pages=§1.5.2 p. 45|edition=Fourth|publisher=Wiley|location=New York|isbn=978-0-471-32168-2}}</ref>{{anchor|Saturation}} संतृप्ति मोड | {{cite book|author1=PR Gray|author2=PJ Hurst|author3=SH Lewis|author4=RG Meyer|title=Analysis and design of analog integrated circuits|year=2001|pages=§1.5.2 p. 45|edition=Fourth|publisher=Wiley|location=New York|isbn=978-0-471-32168-2}}</ref>{{anchor|Saturation}} संतृप्ति मोड या ओमिक और संतृप्ति के बीच के क्षेत्र का उपयोग तब किया जाता है जब प्रवर्धन की आवश्यकता होती है। बीच के क्षेत्र को कभी-कभी ओमिक या रैखिक क्षेत्र का हिस्सा माना जाता है, जहां ड्रेन की धारा ड्रेन वोल्टेज के साथ लगभग रैखिक नहीं होती है। | ||

भले ही गेट-टू-सोर्स वोल्टेज द्वारा गठित प्रवाहकीय चैनल अब संतृप्ति मोड के दौरान स्रोत को | भले ही गेट-टू-सोर्स वोल्टेज द्वारा गठित प्रवाहकीय चैनल अब संतृप्ति मोड के दौरान स्रोत को ड्रेन से नहीं जोड़ता है, वाहक बहने से अवरुद्ध नहीं होते हैं। फिर से एक एन-चैनल वृद्धि-मोड उपकरणों को ध्यान में रखते हुए, पी-टाइप बॉडी क्षेत्र में एक कमी मौजूद करता है, जो प्रवाहकीय चैनल , ड्रेन और स्रोत क्षेत्रों के आसपास है। चैनल को शामिल करने वाले इलेक्ट्रॉन रिक्त क्षेत्र के माध्यम से चैनल से बाहर जाने के लिए स्वतंत्र है यदि ड्रेन-से-स्रोत वोल्टेज द्वारा ड्रेन की ओर आकर्षित किया जाता है। अवक्षय क्षेत्र वाहकों से मुक्त होता है और इसमें सिलिकॉन के समान प्रतिरोध होता है ड्रेन-टू-सोर्स वोल्टेज की कोई भी वृद्धि ड्रेन से पिंच-ऑफ पॉइंट तक की दूरी को बढ़ाएगी, जिससे ड्रेन-टू-सोर्स वोल्टेज के अनुपात में अवक्षय क्षेत्र के प्रतिरोध में वृद्धि होगी। यह आनुपातिक परिवर्तन ड्रेन-से-स्रोत करंट को अपेक्षाकृत निश्चित रूप से स्थिर रहने का कारण बनता है, ड्रेन-टू-सोर्स वोल्टेज में परिवर्तन से स्वतंत्र, संचालन के रैखिक मोड में इसके ओमिक व्यवहार के विपरीत इस प्रकार संतृप्ति मोड में एफईटी एक अवरोधक के बजाय एक निरंतर-वर्तमान स्रोत के रूप में व्यवहार करता है और प्रभावी रूप से वोल्टेज एम्पलीफायर के रूप में उपयोग किया जा सकता है। इस मामले में, गेट-टू-सोर्स वोल्टेज चैनल के माध्यम से निरंतर करंट के स्तर को निर्धारित करता है। | ||

== | == संयोजन == | ||

एफईटी का निर्माण विभिन्न अर्धचालकों से किया जा सकता है, जिनमें से सिलिकॉन अब तक का सबसे आम तरीका है।अधिकांश एफईटी पारंपरिक थोक अर्धचालक प्रसंस्करण तकनीकों का उपयोग करके, सक्रिय क्षेत्र या चैनल के रूप में एकल क्रिस्टल अर्धचालक वेफर का उपयोग करके बनाए जाते हैं। | |||

अधिक असामान्य | अधिक असामान्य बॉडी सामग्री में ऐमौरफस सिलिकॉन, पॉलीक्रिस्टलाइन सिलिकॉन या थिन-फिल्म ट्रांजिस्टर या औरगैनिक फिल्ड-एफेकट ट्रांजिस्टर (OFETs) में अन्य ऐमौरफस अर्धचालक हैं जो कार्बनिक अर्धचालकों पर आधारित हैं,अक्सर ओएफईटी गेट इंसुलेटर और इलेक्ट्रोड कार्बनिक पदार्थों से बने होते हैं इस तरह के FETs को सिलिकॉन कार्बाइड (SiC), गैलियम आर्सेनाइड (GaAs), गैलियम नाइट्राइड (GaN) और इंडियम गैलियम आर्सेनाइड (InGaAs) जैसी विभिन्न सामग्रियों का उपयोग करके निर्मित किया जाता है। | ||

जून 2011 में, आईबीएम ने घोषणा की कि उसने एक एकीकृत | जून 2011 में, आईबीएम (IBM)ने घोषणा की कि,उसने एक एकीकृत परिपथ में ग्राफीन-आधारित एफईटीएस का सफलतापूर्वक उपयोग किया था।<ref>{{cite news|author=Bob Yirka|url=https://phys.org/news/2011-06-ibm-graphene-based-circuit.html|title=IBM creates first graphene based integrated circuit|website=[[Phys.org]]|date=10 January 2011|access-date=14 January 2019}}</ref><ref>{{cite journal|author1=Lin, Y.-M.|author2=Valdes-Garcia, A.|author3=Han, S.-J.|author4=Farmer, D. B.|author5=Sun, Y.|author6=Wu, Y.|author7=Dimitrakopoulos, C.|author8=Grill, A |author9=Avouris, P|author10=Jenkins, K. A.|title=Wafer-Scale Graphene Integrated Circuit|doi=10.1126/science.1204428|journal=Science|volume=332|issue=6035|pages=1294–1297|year=2011|pmid=21659599|bibcode=2011Sci...332.1294L|s2cid=3020496}}</ref> ये ट्रांजिस्टर लगभग 2.23 (GHz)गीगाहर्ट्ज़ कटऑफ आवृत्ति के लिए सक्षम हैं, जो मानक सिलिकॉन एफईटी(FETs) से बहुत अधिक है।<ref>{{cite magazine|url=http://physicsworld.com/cws/article/news/2012/dec/10/flexible-graphene-transistor-sets-new-records|title=Flexible graphene transistor sets new records|author=Belle Dumé|magazine=Physics World|date=10 December 2012|access-date=14 January 2019}}</ref> | ||

== प्रकार == | == प्रकार == | ||

[[File:FET comparison.png|right|300px|thumb| | [[File:FET comparison.png|right|300px|thumb|विशिष्ट वोल्टेज के तहत रिक्तीकरण-प्रकार के FETs: JFET, पॉली-सिलिकॉन MOSFET, डबल-गेट MOSFET, मेटल-गेट MOSFET, MESFET | ||

{{legend|#808080|Depletion}} | {{legend|#808080|Depletion}}रिक्तिकरण{{legend|#0000FF|Electrons}}इलेक्ट्रॉनों{{legend|white|Insulator}} | ||

{{legend|#0000FF|Electrons}} | {{legend|#FF0000|Holes}}छेद{{legend|#000000|Metal}}धातु ऊपर: स्रोत, नीचे: नाली, बाएं: गेट, दाएं: बल्क। वोल्टेज जो चैनल गठन की ओर ले जाने वाले वोल्टेज नहीं दिखाए जाते हैं।]] | ||

{{legend| | एक एफईटी के चैनल को एन-टाइप अर्धचालकों या पी-टाइप अर्धचालकों का उत्पादन करने के लिए डोप किया जाता है। वृद्धि मोड एफईटी के मामले में, ड्रेन और स्रोत को चैनल के विपरीत प्रकार से डोप किया जा सकता है, या चैनल के समान प्रकार से डोप किया जा सकता है, जैसे कि मोड फेट्स के रूप में। फील्ड-इफेक्ट ट्रांजिस्टर भी चैनल और गेट के बीच इन्सुलेशन की विधि द्वारा प्रतिष्ठित हैं। FETs के प्रकारों में शामिल हैं: | ||

{{legend|# | |||

{{legend| | |||

एक एफईटी के चैनल को एन-टाइप | |||

*MOSFET (मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) एक इन्सुलेटर का उपयोग करता है (आमतौर पर | *MOSFET (मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) गेट और बॉडी के बीच एक इन्सुलेटर का उपयोग करता है (आमतौर पर SiO2)। यह अब तक का सबसे आम प्रकार है। | ||

** DGMOSFET ( | ** DGMOSFET (डुअल-गेट मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) या DGMOS, एक MOSFET जिसमें दो इंसुलेटेड गेट होते हैं। | ||

** IGBT (इंसुलेटेड-गेट | ** IGBT (इंसुलेटेड-गेट बाइपोलर ट्रांजिस्टर) बिजली नियंत्रण के लिए एक उपकरण है।इसकी संरचना एक MOSFET जैसी है जो एक बाइपोलर जैसे मुख्य चालन चैनल के साथ युग्मित है।आमतौर पर संचालन के 200-3000 V ड्रेन-टू-सोर्स वोल्टेज रेंज के लिए उपयोग किए जाते है।पावर MOSFETS अभी भी 1से200 V के ड्रेन-से-स्रोत वोल्टेज के लिए पसंदीदा उपकरण है। | ||

** JLNT (जंक्शनलेस नैनोवायर ट्रांजिस्टर) एक प्रकार का फील्ड-इफेक्ट ट्रांजिस्टर (FET) है | ** JLNT (जंक्शनलेस नैनोवायर ट्रांजिस्टर) एक प्रकार का फील्ड-इफेक्ट ट्रांजिस्टर (FET) है जिस चैनल में अनेक नैनोवायर है और किसी भी जंक्शन को प्रस्तुत नहीं करता है। | ||

** MNOS ( | ** MNOS (मेटल-नाइट्राइड-ऑक्साइड-सेमीकंडक्टर ट्रांजिस्टर) गेट और बॉडी के बीच एक नाइट्राइड-ऑक्साइड परत इन्सुलेटर का उपयोग करता है। | ||

** ISFET (आयन- | ** ISFET (आयन सेंनसिटीव फिल्ड-एफेकट ट्रांजिस्टर) का उपयोग समाधान में आयन सांद्रता को मापने के लिए किया जा सकता है जब आयन सांद्रता (H+, pH इलेक्ट्रोड देखें) में परिवर्तन होता है, तो ट्रांजिस्टर के माध्यम से प्रवाहित धारा तदनुसार बदल जाएगी। | ||

** | ** BioFET (बायोलाजिकल सेंनसिटीव फिल्ड-एफेकट ट्रांजिस्टर) ISFET तकनीक पर आधारित सेंसर/बायोसेंसर का एक वर्ग है, जिसका उपयोग आवेशित अणुओं का पता लगाने के लिए किया जाता है,जब एक आवेशित अणु मौजूद हो तो बायोफेट(BioFET) सतह पर इलेक्ट्रोस्टैटिक क्षेत्र में परिवर्तन ट्रांजिस्टर के माध्यम से करंट में एक औसत दर्जे का परिवर्तन होता है।इनमें एंजाइम संशोधित FETs (ENFETs), इम्यूनोलॉजिकल रूप से संशोधित FETs(ImmunoFETs), जीन-संशोधित FETS (GenFETs), DNAFETs, सेल-आधारित बायोफेट (CPFETs), बीटल/चिप FETs (BeetleFETs) और आयन-चैनलों पर आधारित एफईटी (FETs) शामिल हैं।<ref>{{cite journal|author=Schöning, Michael J.|author2=Poghossian, Arshak|title=Recent advances in biologically sensitive field-effect transistors (BioFETs)|journal=Analyst|year=2002|volume=127|issue=9|pages=1137–1151|doi=10.1039/B204444G|pmid=12375833|bibcode=2002Ana...127.1137S|url=http://juser.fz-juelich.de/record/16078/files/12968.pdf}}</ref> | ||

** DNAFET (डीएनए फील्ड-इफेक्ट ट्रांजिस्टर) एक विशेष FET है जो | ** DNAFET (डीएनए फील्ड-इफेक्ट ट्रांजिस्टर) एक विशेष FET है जो कि डीएनए स्ट्रैंड्स का पता लगाने के लिए सिंगल-स्ट्रैंड डीएनए अणुओं से बने गेट का उपयोग करके बायोसेंसर के रूप में कार्य करता है। | ||

** | ** GAAFET या गेट-ऑल-अराउंड FET सहित finFET शामिल है, जिसका उपयोग उच्च घनत्व प्रोसेसर चिप्स पर किया जाता हैं। | ||

*JFET (जंक्शन फील्ड-इफेक्ट ट्रांजिस्टर) | *JFET (जंक्शन फील्ड-इफेक्ट ट्रांजिस्टर) बॉडी से गेट को अलग करने के लिए एक रिवर्स बायस्ड पी-एन जंक्शन का उपयोग करता है। | ||

** स्टेटिक इंडक्शन ट्रांजिस्टर | ** SIT (स्टेटिक इंडक्शन ट्रांजिस्टर) एक छोटे चैनल वाले JFET का एक प्रकार है। | ||

*DEPFET एक FET है जो पूरी तरह से | *DEPFET एक FET है जो पूरी तरह से समाप्त सब्सट्रेट में बनता है और एक ही समय में सेंसर, एम्पलीफायर और मेमोरी नोड के रूप में कार्य करता है। इसका उपयोग इमेज (फोटॉन) सेंसर के रूप में किया जा सकता है। | ||

*FREDFET (फास्ट-रिवर्स या फास्ट-रिकवरी एपिटैक्सियल डायोड FET) एक विशेष FET है | *FREDFET (फास्ट-रिवर्स या फास्ट-रिकवरी एपिटैक्सियल डायोड FET) एक विशेष FET है जिसे बॉडी डायोड की एक बहुत तेजी से रिकवरी (टर्न-ऑफ) प्रदान करने के लिए डिज़ाइन किया गया है, जो इसे इलेक्ट्रिक मोटर्स, जैसे आगमनात्मक भार विशेष रूप से मध्यम- संचालित ब्रशलेस डीसी मोटर्स चलाने के लिए सुविधाजनक बनाता है। | ||

*HIGFET (हेटरोस्ट्रक्चर इंसुलेटेड-गेट फील्ड-इफेक्ट ट्रांजिस्टर) का उपयोग | *HIGFET (हेटरोस्ट्रक्चर इंसुलेटेड-गेट फील्ड-इफेक्ट ट्रांजिस्टर) का उपयोग मुख्य रूप से अनुसंधान में किया जाता है।<ref>[https://www.freepatentsonline.com/5614739.html freepatentsonline.com], HIGFET and method - Motorola]</ref> | ||

*MODFET (मॉड्यूलेशन-डॉप्ड फील्ड-इफेक्ट ट्रांजिस्टर) सक्रिय क्षेत्र के ग्रेडेड डोपिंग द्वारा गठित क्वांटम अच्छी तरह से संरचना का उपयोग | *MODFET (मॉड्यूलेशन-डॉप्ड फील्ड-इफेक्ट ट्रांजिस्टर) | ||

** एक उच्च-इलेक्ट्रॉन-मोबिलिटी ट्रांजिस्टर है,जो सक्रिय क्षेत्र के ग्रेडेड डोपिंग द्वारा गठित क्वांटम अच्छी तरह से संरचना का उपयोग करता है। | |||

** | |||

* | |||

*TFET (टनल फील्ड-इफेक्ट ट्रांजिस्टर) बैंड-टू-बैंड टनलिंग पर आधारित है।<ref>{{cite journal|author=Ionescu, A. M.|author2=Riel, H.|author2-link=Heike Riel|doi=10.1038/nature10679|title=Tunnel field-effect transistors as energy-efficient electronic switches|journal=[[Nature (journal)|Nature]]|volume=479|issue=7373|pages=329–337|year=2011|pmid=22094693|bibcode=2011Natur.479..329I|s2cid=4322368}}</ref> | *TFET (टनल फील्ड-इफेक्ट ट्रांजिस्टर) बैंड-टू-बैंड टनलिंग पर आधारित है।<ref>{{cite journal|author=Ionescu, A. M.|author2=Riel, H.|author2-link=Heike Riel|doi=10.1038/nature10679|title=Tunnel field-effect transistors as energy-efficient electronic switches|journal=[[Nature (journal)|Nature]]|volume=479|issue=7373|pages=329–337|year=2011|pmid=22094693|bibcode=2011Natur.479..329I|s2cid=4322368}}</ref> | ||

* TQFET (टोपोलॉजिकल क्वांटम फील्ड-इफेक्ट ट्रांजिस्टर) एक | * TQFET (टोपोलॉजिकल क्वांटम फील्ड-इफेक्ट ट्रांजिस्टर) एक 2डी सामग्री को अपव्यय रहित टोपोलॉजिकल इंसुलेटर ('ऑन' स्टेट) से पारंपरिक इंसुलेटर ('ऑफ' स्टेट) में एक लागू विद्युत क्षेत्र का उपयोग करके स्विच करता है। | ||

*HEMT ( | *HEMT (हाई-इलेक्ट्रॉन-मोबिलिटी ट्रांजिस्टर), जिसे HFET (हेटरोस्ट्रक्चर FET) भी कहा जाता है, AlGaAs जैसे एक टर्नरी सेमीकंडक्टर में बैंडगैप इंजीनियरिंग का उपयोग करके बनाया जा सकता है।पूरी तरह से समाप्त वाइड-बैंड-गैप सामग्री गेट और बॉडी के बीच अलगाव बनाती है। | ||

*MESFET ( | *MESFET ( मेटल-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) एक शोट्की (Schottky) बैरियर के साथ जेएफईटी के पी-एन जंक्शन को प्रतिस्थापित करता है और GaAs और अन्य III-V अर्धचालक सामग्री में उपयोग किया जाता है। | ||

*NOMFET एक नैनोपार्टिकल ऑर्गेनिक मेमोरी फील्ड-इफेक्ट ट्रांजिस्टर है।<ref>{{cite news|url=https://www.sciencedaily.com/releases/2010/01/100125122101.htm|title=Organic transistor paves way for new generations of neuro-inspired computers|work=[[ScienceDaily]]|date=January 29, 2010|access-date=January 14, 2019}}</ref> | *NOMFET एक नैनोपार्टिकल ऑर्गेनिक मेमोरी फील्ड-इफेक्ट ट्रांजिस्टर है।<ref>{{cite news|url=https://www.sciencedaily.com/releases/2010/01/100125122101.htm|title=Organic transistor paves way for new generations of neuro-inspired computers|work=[[ScienceDaily]]|date=January 29, 2010|access-date=January 14, 2019}}</ref> | ||

*GNRFET (ग्राफीन नैनोरिबोन फ़ील्ड-इफेक्ट ट्रांजिस्टर) अपने चैनल के लिए एक ग्राफीन नैनोरिबोन का उपयोग करता है।<ref>{{cite journal|author=Sarvari H.|author2=Ghayour, R.|author3=Dastjerdy, E.|title=Frequency analysis of graphene nanoribbon FET by Non-Equilibrium Green's Function in mode space|journal=Physica E: Low-dimensional Systems and Nanostructures|volume=43|issue=8|pages=1509–1513|year=2011|doi=10.1016/j.physe.2011.04.018|bibcode=2011PhyE...43.1509S}}</ref> | *GNRFET (ग्राफीन नैनोरिबोन फ़ील्ड-इफेक्ट ट्रांजिस्टर) अपने चैनल के लिए एक ग्राफीन नैनोरिबोन का उपयोग करता है।<ref>{{cite journal|author=Sarvari H.|author2=Ghayour, R.|author3=Dastjerdy, E.|title=Frequency analysis of graphene nanoribbon FET by Non-Equilibrium Green's Function in mode space|journal=Physica E: Low-dimensional Systems and Nanostructures|volume=43|issue=8|pages=1509–1513|year=2011|doi=10.1016/j.physe.2011.04.018|bibcode=2011PhyE...43.1509S}}</ref> | ||

*VESFET (वर्टिकल-स्लिट फील्ड-इफेक्ट ट्रांजिस्टर) एक | *VESFET (वर्टिकल-स्लिट फील्ड-इफेक्ट ट्रांजिस्टर) एक चौकोर आकार का जंक्शन रहित FET है जिसमें एक संकीर्ण स्लिट है जो स्रोत को जोड़ता है और विपरीत कोनों पर ड्रेन को जोड़ता है।दो गेट दूसरे कोनों पर कब्जा करते हैं और स्लिट के माध्यम से करंट को नियंत्रित करते हैं।<ref>{{cite book|author=Jerzy Ruzyllo|title=Semiconductor Glossary: A Resource for Semiconductor Community|url=https://books.google.com/books?id=UlItDQAAQBAJ&pg=PA244|year=2016|publisher=World Scientific|isbn=978-981-4749-56-5|page=244}}</ref> | ||

*CNTFET (कार्बन नैनोट्यूब फील्ड-इफेक्ट ट्रांजिस्टर)। | *CNTFET (कार्बन नैनोट्यूब फील्ड-इफेक्ट ट्रांजिस्टर)। | ||

*OFET ( | *OFET (ऑर्गेनिक फील्ड-इफेक्ट ट्रांजिस्टर) अपने चैनल में एक ऑर्गेनिक अर्धचालक का उपयोग करता है। | ||

*QFET (क्वांटम फील्ड इफेक्ट ट्रांजिस्टर) | *QFET (क्वांटम फील्ड इफेक्ट ट्रांजिस्टर) पारंपरिक ट्रांजिस्टर के इलेक्ट्रॉन चालन क्षेत्र को समाप्त करके ट्रांजिस्टर संचालन की गति को बढ़ाने के लिए क्वांटम टनलिंग का लाभ उठाता है। | ||

*SB-FET ( | *SB-FET (स्कॉट्की-बैरियर फील्ड-इफेक्ट ट्रांजिस्टर) धातु के स्रोत और ड्रेन कॉन्टैक्ट इलेक्ट्रोड के साथ एक फील्ड-इफेक्ट ट्रांजिस्टर है, जो सोर्स-चैनल और ड्रेन-चैनल इंटरफेस दोनों में शोट्की(Schottky) बैरियर बनाते हैं।<ref>{{cite journal|author=Prakash, Abhijith|author2=Ilatikhameneh, Hesameddin|author3=Wu, Peng|author4=Appenzeller, Joerg|year=2017|title=Understanding contact gating in Schottky barrier transistors from 2D channels|journal=Scientific Reports|volume=7|issue=1|pages=12596|doi=10.1038/s41598-017-12816-3|pmid=28974712|pmc=5626721|arxiv=1707.01459|bibcode=2017NatSR...712596P|issn=2045-2322|oclc=1010581463}}</ref> | ||

*GFET एक अत्यधिक संवेदनशील ग्राफीन-आधारित क्षेत्र प्रभाव ट्रांजिस्टर है जिसका उपयोग बायोसेंसर और रासायनिक सेंसर के रूप में किया जाता है।ग्राफीन की | *GFET एक अत्यधिक संवेदनशील ग्राफीन-आधारित क्षेत्र प्रभाव ट्रांजिस्टर है जिसका उपयोग बायोसेंसर और रासायनिक सेंसर के रूप में किया जाता है।ग्राफीन की दो आयामी संरचना के कारण, इसके भौतिक गुणों के साथ, GFETs संवेदनशीलता में वृद्धि करते है और संवेदन अनुप्रयोगों में 'झूठी सकारात्मकता' के उदाहरणों को कम करते हैं।<ref>{{cite web|author=Miklos, Bolza|title=What Are Graphene Field Effect Transistors (GFETs)?|url=https://www.graphenea.com/pages/what-are-graphene-field-effect-transistors-gfets|website=Graphenea|access-date=14 January 2019}}</ref> | ||

*Fe FET गेट के बीच एक फेरोइलेक्ट्रिक का उपयोग करता है, जिससे ट्रांजिस्टर | *Fe FET गेट के बीच एक फेरोइलेक्ट्रिक का उपयोग करता है, जिससे ट्रांजिस्टर पूर्वाग्रह के अभाव में अपनी स्थिति बनाए रखता है, ऐसे उपकरणों में गैर -वाष्पशील मेमोरी के रूप में अनुप्रयोग हो सकता है। | ||

* VTFET | * VTFET या वर्टिकल-ट्रांसपोर्ट फ़ील्ड-इफेक्ट ट्रांजिस्टर, उच्च घनत्व और कम शक्ति की अनुमति देने के लिए IBM का 2021 में finFET का संशोधन।<ref>[https://www.marktechpost.com/2021/12/21/ibm-research-unveils-vtfet-a-revolutionary-new-chip-architecture-which-is-two-times-the-performance-finfet/ ''IBM Research Unveils ‘VTFET’: A Revolutionary New Chip Architecture Which is Two Times the Performance finFET'' Dec 2021]</ref> | ||

== लाभ == | == लाभ == | ||

फील्ड-इफेक्ट ट्रांजिस्टर में 100 MΩ या उससे अधिक के क्रम में उच्च गेट-टू-ड्रेन करंट प्रतिरोध होता है, जो नियंत्रण और प्रवाह के बीच उच्च स्तर का अलगाव प्रदान करता | फील्ड-इफेक्ट ट्रांजिस्टर में 100 MΩ या उससे अधिक के क्रम में उच्च गेट-टू-ड्रेन करंट प्रतिरोध होता है, जो नियंत्रण और प्रवाह के बीच उच्च स्तर का अलगाव प्रदान करता है क्योंकि करंट का शोर आकार देने के समय के साथ बढ़ेगा।{{clarify|date=December 2021}}<ref>[http://www-physics.lbl.gov/~spieler/physics_198_notes/PDF/VIII-5-noise.pdf VIII.5. Noise in Transistors]</ref> एक एफईटी आमतौर पर बाइपोलर जंक्शन ट्रांजिस्टर (बीजेटी) की तुलना में कम शोर करता है वीएचएफ और सैटेलाइट रिसीवर के लिए ट्यूनर, कम-शोर वाले एम्पलीफायरों जैसे शोर-संवेदनशील इलेक्ट्रॉनिक्स में पाया जाता है।यह विकिरण के प्रति अपेक्षाकृत प्रतिरक्षा है। यह शून्य ड्रेन करंट में कोई ऑफसेट वोल्टेज नहीं प्रदर्शित करता है और एक उत्कृष्ट सिग्नल चॉपर बनाता है इसमें आमतौर पर बीजेटी (BJT) की तुलना में बेहतर थर्मल स्थिरता होती है।<ref name=millman/> | ||

क्योंकि फेट्स (FETs)को गेट चार्ज द्वारा नियंत्रित किया जाता है, एक बार गेट बंद होने या खुला होने के बाद, कोई अतिरिक्त पावर ड्रॉ नहीं होता है, क्योंकि कुछ अवस्थाओं में एक बाइपोलर जंक्शन ट्रांजिस्टर या नॉन-लैचिंग रिले के साथ | क्योंकि फेट्स (FETs)को गेट चार्ज द्वारा नियंत्रित किया जाता है, एक बार गेट बंद होने या खुला होने के बाद, कोई अतिरिक्त पावर ड्रॉ नहीं होता है, क्योंकि कुछ अवस्थाओं में एक बाइपोलर जंक्शन ट्रांजिस्टर या नॉन-लैचिंग रिले के साथ होगा यह बेहद कम-शक्ति स्विचिंग की अनुमति देता है, जो बदले में परिपथ के अधिक लघुकरण की अनुमति देता है क्योंकि अन्य प्रकार के स्विचों की तुलना में गर्मी अपव्यय की आवश्यकता कम हो जाती है। | ||

== नुकसान == | == नुकसान == | ||

एक फील्ड-इफेक्ट ट्रांजिस्टर में एक | एक फील्ड-इफेक्ट ट्रांजिस्टर में एक बाइपोलर जंक्शन ट्रांजिस्टर की तुलना में अपेक्षाकृत कम लाभ -बैंडविथ उत्पाद होता है।MOSFETs अधिभार वोल्टेज के लिए अतिसंवेदनशील होते हैं, इस प्रकार स्थापना के दौरान विशेष रुप से संभालने(हैंडलिंग) की आवश्यकता होती है।<ref>{{cite book|author=Allen Mottershead|title=Electronic devices and siraj circuits|year=2004|publisher=Prentice-Hall of India|location=New Delhi|isbn=978-81-203-0124-5}}</ref> गेट और चैनल के बीच MOSFET की नाजुक इंसुलेटिंग परत इसे इलेक्ट्रोस्टैटिक डिस्चार्ज के लिए या हैंडलिंग के दौरान थ्रेशोल्ड वोल्टेज में परिवर्तन के प्रति संवेदनशील बनाती है। इसमें कोई समस्या नहीं होती है अगर उपकरण को ठीक से डिज़ाइन किए गए परिपथ में स्थापित किया जाए। | ||

FETs में अक्सर कम " | FETs में अक्सर कम "ऑन" प्रतिरोध होता है और उच्च "ऑफ" प्रतिरोध होता है। हालांकि मध्यवर्ती प्रतिरोध महत्वपूर्ण हैं और इसलिए FETs स्विच करते समय बड़ी मात्रा में बिजली को नष्ट कर सकते हैं।इस प्रकार, दक्षता जल्दी से स्विच करने पर एक प्रीमियम लगा सकती है, लेकिन यह उन संक्रमणों का कारण बन सकता है जो आवारा अधिष्ठापन को उत्तेजित कर सकते हैं और महत्वपूर्ण वोल्टेज उत्पन्न कर सकते हैं जो गेट पर युगल कर सकते हैं और अनजाने में स्विचिंग का कारण बन सकते हैं, इसलिए FET परिपथ को सावधानीपूर्वक लेआउट की आवश्यकता हो सकती है और स्विचिंग गति और बिजली अपव्यय के बीच ट्रेडों को शामिल किया जा सकता है। वोल्टेज रेटिंग और "ऑन" रेजिस्टेंस के बीच एक ट्रेड-ऑफ भी है इसलिए उच्च-वोल्टेज एफईटीएस में अपेक्षाकृत उच्च ऑन" रेजिस्टेंस होता है और इसलिए चालन लॉस होता है।<ref>{{Cite web|last=Bhalla|first=Anup|date=2021-09-17|title=Origins of SiC FETs and Their Evolution Toward the Perfect Switch|url=https://www.powerelectronicsnews.com/origins-of-sic-fets-and-their-evolution-toward-the-perfect-switch/|access-date=2022-01-21|website=Power Electronics News|language=en-US}}</ref> | ||

== विफल मोड == | == विफल मोड == | ||

फील्ड-इफेक्ट ट्रांजिस्टर अपेक्षाकृत मजबूत होते हैं, खासकर जब निर्माता द्वारा परिभाषित विद्युत सीमाओं (उचित व्युत्पन्न) के भीतर संचालित होता हैं। हालांकि, आधुनिक एफईटी उपकरण अक्सर एक बॉडी डायोड को शामिल कर सकते | फील्ड-इफेक्ट ट्रांजिस्टर अपेक्षाकृत मजबूत होते हैं, खासकर जब निर्माता द्वारा परिभाषित विद्युत सीमाओं (उचित व्युत्पन्न) के भीतर संचालित होता हैं। हालांकि, आधुनिक एफईटी उपकरण अक्सर एक बॉडी डायोड को शामिल कर सकते हैं, यदि बॉडी डायोड की विशेषताओं को ध्यान में नहीं रखा जाता है, तो एफईटी धीमी गति से बॉडी डायोड व्यवहार का अनुभव कर सकता है, जहां एक परजीवी ट्रांजिस्टर चालू हो जाएगा और एफईटी(FET) के बंद होने पर उच्च धारा को ड्रेन से स्रोत तक खींचने की अनुमति देगा।<ref>[https://www.dfrsolutions.com/hubfs/Resources/Slow_Body_Diode_Failures.pdf?t=1513022462214 Slow Body Diode Failures of Field Effect Transistors (FETs): A Case Study].</ref> | ||

== उपयोग == | == उपयोग == | ||

सबसे अधिक इस्तेमाल किया जाने वाला FET MOSFET है। CMOS (कॉम्प्लिमेंटरी मैटल ऑक्साइड सेमीकंडक्टर) प्रक्रिया प्रौद्योगिकी आधुनिक डिजिटल एकीकृत परिपथ का आधार है। यह प्रक्रिया प्रौद्योगिकी की एक ऐसी व्यवस्था का उपयोग करती है जहां पी-चैनल एमओएसएफईटी और एन-चैनल एमओएसएफईटी श्रृंखला में जुड़े होते हैं जैसे कि जब कोई चालू होता है, तो दूसरा बंद हो जाता है। | |||

सबसे अधिक इस्तेमाल किया जाने वाला FET MOSFET है। CMOS ( | |||

एफईटी(FETs) में, रैखिक मोड में संचालित होने पर इलेक्ट्रॉन चैनल के माध्यम से किसी भी दिशा में प्रवाह कर सकते हैं। ड्रेन टर्मिनल और सोर्स टर्मिनल का नामकरण सम्मेलन कुछ हद तक मनमाना है, क्योंकि उपकरण आमतौर पर | एफईटी(FETs) में, रैखिक मोड में संचालित होने पर इलेक्ट्रॉन चैनल के माध्यम से किसी भी दिशा में प्रवाह कर सकते हैं। ड्रेन टर्मिनल और सोर्स टर्मिनल का नामकरण सम्मेलन कुछ हद तक मनमाना है, क्योंकि उपकरण आमतौर पर स्रोत से ड्रेन तक सममित रूप से निर्मित होते हैं। यह एफईटीएस (FETs) को पथों बहुसंकेतन (मल्टीप्लेक्सिंग) के बीच एनालॉग संकेतों को स्विच करने के लिए उपयुक्त बनाता है। इस अवधारणा के साथ, उदाहरण के लिए एक सॉलिड-स्टेट मिश्रण बोर्ड का निर्माण किया जा सकता है, FET को आमतौर पर एक एम्पलीफायर के रूप में उपयोग किया जाता है। उदाहरण के लिए, इसके बड़े इनपुट प्रतिरोध और कम आउटपुट प्रतिरोध के कारण यह कॉमन-ड्रेन (स्रोत अनुयायी) विन्यास में बफर के रूप में प्रभावी है। | ||

IGBT का उपयोग आंतरिक दहन इंजन इग्निशन कॉइल को स्विच करने में किया जाता है, जहां तेजी से स्विचिंग और वोल्टेज अवरुद्ध क्षमताएं महत्वपूर्ण हैं। | IGBT का उपयोग आंतरिक दहन इंजन इग्निशन कॉइल को स्विच करने में किया जाता है, जहां तेजी से स्विचिंग और वोल्टेज अवरुद्ध क्षमताएं महत्वपूर्ण हैं। | ||

| Line 156: | Line 145: | ||

== स्रोत-गेटेड ट्रांजिस्टर == | == स्रोत-गेटेड ट्रांजिस्टर == | ||

स्रोत-गेटेड ट्रांजिस्टर बड़े क्षेत्र के इलेक्ट्रॉनिक्स जैसे प्रदर्शन स्क्रीन में निर्माण और पर्यावरणीय मुद्दों के लिए अधिक मजबूत हैं, लेकिन एफईटी(FETs) की तुलना में संचालन में धीमे हैं।<ref>{{cite journal|author=Sporea, R.A.|author2=Trainor, M.J.|author3=Young, N.D.|author4=Silva, S.R.P.|title=Source-gated transistors for order-of-magnitude performance improvements in thin-film digital circuits|journal=Scientific Reports|year=2014|volume=4|pages=4295|doi=10.1038/srep04295|pmid = 24599023|pmc=3944386|bibcode=2014NatSR...4E4295S}}</ref> | स्रोत-गेटेड ट्रांजिस्टर बड़े क्षेत्र के इलेक्ट्रॉनिक्स जैसे प्रदर्शन स्क्रीन में निर्माण और पर्यावरणीय मुद्दों के लिए अधिक मजबूत हैं, लेकिन एफईटी(FETs) की तुलना में संचालन में धीमे हैं।<ref>{{cite journal|author=Sporea, R.A.|author2=Trainor, M.J.|author3=Young, N.D.|author4=Silva, S.R.P.|title=Source-gated transistors for order-of-magnitude performance improvements in thin-film digital circuits|journal=Scientific Reports|year=2014|volume=4|pages=4295|doi=10.1038/srep04295|pmid = 24599023|pmc=3944386|bibcode=2014NatSR...4E4295S}}</ref> | ||

== यह भी देखें == | == यह भी देखें == | ||

*रासायनिक क्षेत्र-प्रभाव ट्रांजिस्टर | *रासायनिक क्षेत्र-प्रभाव ट्रांजिस्टर | ||

| Line 169: | Line 156: | ||

==संदर्भ== | ==संदर्भ== | ||

{{Reflist}} | {{Reflist}} | ||

==बाहरी संबंध== | ==बाहरी संबंध== | ||

*[https://www.pbs.org/transistor/science/info/transmodern.html PBS The Field Effect Transistor] | *[https://www.pbs.org/transistor/science/info/transmodern.html PBS The Field Effect Transistor] | ||

*[https://www.wecanfigurethisout.org/VL/MOS_kit.htm How Semiconductors and Transistors Work (MOSFETs)] WeCanFigureThisOut.org | *[https://www.wecanfigurethisout.org/VL/MOS_kit.htm How Semiconductors and Transistors Work (MOSFETs)] WeCanFigureThisOut.org | ||

| Line 181: | Line 166: | ||

*[https://ljmayes.pnyhost.com/comp/vcr.html The Field Effect Transistor as a Voltage Controlled Resistor] | *[https://ljmayes.pnyhost.com/comp/vcr.html The Field Effect Transistor as a Voltage Controlled Resistor] | ||

*{{cite web|date=March 30, 2013 |title=The FET (field effect transistor)|url=https://www.youtube.com/watch?v=SjeK1nkiFvI|via=[[YouTube]]|publisher=rolinychupetin (L.R.Linares)}} | *{{cite web|date=March 30, 2013 |title=The FET (field effect transistor)|url=https://www.youtube.com/watch?v=SjeK1nkiFvI|via=[[YouTube]]|publisher=rolinychupetin (L.R.Linares)}} | ||

{{Authority control}} | {{Authority control}} | ||

{{DEFAULTSORT:Field-Effect Transistor}} | {{DEFAULTSORT:Field-Effect Transistor}} | ||

] | ] | ||

[[Category:Machine Translated Page]] | |||

[[Category:AC with 0 elements|Field-Effect Transistor]] | |||

[[Category:All articles needing additional references|Field-Effect Transistor]] | |||

[[Category:Articles needing additional references from September 2018|Field-Effect Transistor]] | |||

[[Category:Articles with hatnote templates targeting a nonexistent page|Field-Effect Transistor]] | |||

[[Category:Articles with invalid date parameter in template|Field-Effect Transistor]] | |||

[[Category:Articles with short description|Field-Effect Transistor]] | |||

[[Category:CS1 English-language sources (en)]] | |||

[[Category:CS1 maint|Field-Effect Transistor]] | |||

[[Category:Exclude in print|Field-Effect Transistor]] | |||

[[Category:Interwiki category linking templates|Field-Effect Transistor]] | |||

[[Category:Interwiki link templates|Field-Effect Transistor]] | |||

[[Category:Missing redirects|Field-Effect Transistor]] | |||

[[Category:Pages with script errors|Field-Effect Transistor]] | |||

[[Category:Short description with empty Wikidata description|Field-Effect Transistor]] | |||

[[Category:Template documentation pages|Documentation/doc]] | |||

[[Category:Templates that add a tracking category|Field-Effect Transistor]] | |||

[[Category:Templates used by AutoWikiBrowser|Cite web]] | |||

[[Category:Templates using TemplateData|Field-Effect Transistor]] | |||

[[Category:Wikimedia Commons templates|Field-Effect Transistor]] | |||

[[Category:Wikipedia articles needing clarification from December 2021|Field-Effect Transistor]] | |||

Latest revision as of 16:36, 23 August 2023

क्षेत्र प्रभाव ट्रांजिस्टर (फील्ड-इफेक्ट ट्रांजिस्टर) (FET), एक प्रकार का ट्रांजिस्टर है, जो अर्धचालक में करंट के प्रवाह को नियंत्रित करने के लिए एक विद्युत क्षेत्र का उपयोग करता है।FETS (JFETs या MOSFETs) तीन टर्मिनलों वाले उपकरण हैं: स्रोत, गेट और ड्रेन FETs गेट पर एक वोल्टेज को लगाकर विद्युत के प्रवाह को नियंत्रित करते हैं, जो बदले में ड्रेन और स्रोत के बीच चालकता को बदल देता है।

FETs को एकध्रुवीय ट्रांजिस्टर के रूप में भी जाना जाता है, क्योंकि वे एकल-वाहक-प्रकार के संचालन को शामिल करते हैं। अर्थात्, FETs अपने संचालन में आवेश वाहक के रूप में इलेक्ट्रॉनों (N-चैनल) या छेद (P-चैनल) का उपयोग करते हैं। फील्ड इफेक्ट ट्रांजिस्टर कम आवृत्तियों पर बहुत उच्च इनपुट प्रतिबाधा प्रदर्शित करते हैं। सबसे व्यापक रूप से इस्तेमाल किया जाने वाला फील्ड-इफेक्ट ट्रांजिस्टर MOSFET (मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड -इफेक्ट ट्रांजिस्टर) है।

इतिहास

एक फील्ड-इफेक्ट ट्रांजिस्टर (FET) की अवधारणा को पहली बार 1925 में ऑस्ट्रो-हंगेरियन भौतिक विज्ञानी जूलियस एडगर लिलिएनफेल्ड द्वारा[1] और 1934 में ऑस्कर हील द्वारा, पेटेंट कराया गया था। लेकिन वे अवधारणा के आधार पर एक व्यावहारिक अर्धचालक उपकरण बनाने में असमर्थ थे।17 साल के पेटेंट की समय सीमा समाप्त होने के बाद 1947 में बेल लैब्स में विलियम शॉक्ले के तहत काम करते हुए जॉन बार्डीन और वाल्टर हाउसर ब्रैटन द्वारा ट्रांजिस्टर प्रभाव को बाद में देखा गया और समझाया गया। शॉकली ने शुरू में एक अर्धचालक की चालकता को संशोधित करने की कोशिश करके एक कार्यशील एफईटी(FET) बनाने का प्रयास किया, लेकिन असफल रहा मुख्य रूप से सतह की अवस्थाओं, लटकने वाले बंधन, और जर्मेनियम और तांबे मिश्रित सामग्री की समस्याओं के कारण। काम करने वाले FET के निर्माण में उनकी विफलता के पीछे के रहस्यमय कारणों को समझने की कोशिश में, इसने 1947 में पॉइंट-कॉन्टैक्ट ट्रांजिस्टर का आविष्कार करने के बजाय बार्डीन और ब्रेटन को जन्म दिया, जिसके बाद 1948 में शॉक्ले के बाइपोलर जंक्शन ट्रांजिस्टर का आविष्कार किया गया।[2][3]

सफलतापूर्वक निर्मित होने वाला पहला एफईटी (FET) उपकरण, जंक्शन फील्ड-इफेक्ट ट्रांजिस्टर (JFET) था।[2]एक JFET को पहली बार 1945 में हेनरिक वेलकर द्वारा पेटेंट कराया गया था।[4] स्टेटिक इंडक्शन ट्रांजिस्टर (SIT), एक छोटे चैनल के साथ जेएफईटी का एक प्रकार जिसे जापानी इंजीनियरों जून-इची निशिज़ावा और वाई वतनबे द्वारा 1950 में आविष्कार किया गया था। 1952 में जेएफईटी पर शॉक्ले के सैद्धांतिक उपचार के बाद, एक काम करने वाले जेएफईटी का निर्माण 1953 में जॉर्ज एफ.डेसी और इयान एम. रॉस द्वारा किया गया।[5]

[6]जंक्शन ट्रांजिस्टर अपेक्षाकृत भारी उपकरण थे, जिनका एक द्रव्यमान-उत्पादन के आधार पर निर्माण करना मुश्किल था, इंसुलेटेड-गेट फील्ड-इफेक्ट ट्रांजिस्टर (IGFET) को जंक्शन ट्रांजिस्टर के संभावित विकल्प के रूप में सिद्धांतित किया गया था, लेकिन शोधकर्ता काम करने वाले IGFET का निर्माण करने में असमर्थ थे,जो बाहरी विद्युत क्षेत्र को सामग्री में प्रवेश करने से रोकते थे।[6]1950 के दशक के मध्य तक, शोधकर्ताओं ने बड़े पैमाने पर एफईटी अवधारणा को छोड़ दिया था और इसके बजाय बाइपोलर जंक्शन ट्रांजिस्टर (BJT) तकनीक पर ध्यान केंद्रित किया था।[7]MOSFET तकनीक की नींव विलियम शॉक्ले, जॉन बार्डीन और वाल्टर ब्रेटन के क्वारा रखी गई थी। शॉक्ले ने 1945 में एफईटी अवधारणा की कल्पना की, लेकिन वह एक कार्यशील उपकरण बनाने में असमर्थ थे। अगले साल बार्डेन ने सतही अवस्थाओं के संदर्भ में अपनी विफलता के बारे में बताया। बार्डेन ने अर्धचालक पर सतह अवस्थाओं के सिद्धांत को लागू किया (सतह अवस्थाओं पर पिछला काम 1939 में शॉक्ले द्वारा और 1932 में इगोर टैम द्वारा किया गया था) और देखा कि अर्धचालक सतह पर खींचे गए अतिरिक्त इलेक्ट्रॉनों के कारण बाहरी क्षेत्र सतह पर अवरुद्ध हो गया था। इलेक्ट्रॉन उन स्थानीयकृत अवस्थाओं में फंस जाते हैं जो एक व्युत्क्रम परत बनाते हैं। बार्डेन की परिकल्पना ने सतह भौतिकी के जन्म को चिह्नित किया। बार्डीन ने तब अर्धचालक की बहुत पतली परत के बजाय एक व्युत्क्रम परत का उपयोग करने का फैसला किया, जिसकी शॉक्ले ने अपने एफईटी डिजाइनों में कल्पना की थी। उनके सिद्धांत के आधार पर, 1948 में बार्डीन ने MOSFET के पूर्वज इंसुलेटेड-गेट एफईटी (IGFET)को एक व्युत्क्रम परत के साथ पेटेंट कराया। व्युत्क्रम परत अल्पसंख्यक वाहकों के प्रवाह को सीमित करती है, मॉड्यूलेशन और चालकता को बढा़ता है, हालांकि इसका इलेक्ट्रॉन परिवहन गेट के इन्सुलेटर या ऑक्साइड की गुणवत्ता पर निर्भर करता है। बार्डीन के पेटेंट के साथ -साथ एक व्युत्क्रम परत की अवधारणा आज सीएमओएस तकनीक का आधार बनती है। 1976 में शॉक्ले ने बार्डेन की सतह अवस्था परिकल्पना को अर्धचालक कार्यक्रम में सबसे महत्वपूर्ण अनुसंधान विचारों में से एक के रूप में वर्णित किया।[8]बार्डीन की सतह अवस्था के सिद्धांत के बाद 1947 के अंत में, रॉबर्ट गिबनी और ब्रेटन ने सतह की अवस्थाओं के प्रभावों को दूर करने के लिए धातु और अर्धचालक के बीच रखे गए इलेक्ट्रोलाइट के उपयोग का सुझाव दिया। बार्डीन ने आगे बढ़कर सुझाव दिया कि वह व्युत्क्रम परत की चालकता पर ध्यान केंद्रित करे।आगे के प्रयोगों ने उन्हें बेहतर परिणाम प्राप्त करने की उम्मीद में इलेक्ट्रोलाइट को एक ठोस ऑक्साइड परत से बदलने के लिए प्रेरित किया, उनका लक्ष्य ऑक्साइड की परत में प्रवेश करना और व्युत्क्रम परत तक पहुंचना था।हालांकि, बार्डेन ने सुझाव दिया कि वे सिलिकॉन से जर्मेनियम में आगे बढ़ते हुए इस प्रक्रिया से उनका ऑक्साइड अनजाने में धुल जाएगा। वेूलियन होडेसन का तर्क है कि ब्रेटेन और बार्डेन जर्मेनियम के बजाय सिलिकॉन के साथ काम कर रहे होते तो, फील्ड इफेक्ट ट्रांजिस्टर को बनाने में सफल नहीं होते।[8][9][10][11][12]1950 के दशक की पहली छमाही के अंत तक बार्डीन, ब्रेटन, किंग्स्टन, मॉरिसन और अन्य के सैद्धांतिक और प्रयोगात्मक कार्य के बाद, यह पूरी तरह से स्पष्ट हो गया कि सतह अवस्था दो प्रकार की थी। सतह अवस्थाओं को समूहों और अर्धचालक/ऑक्साइड इंटरफ़ेस के साथ जुड़ा हुआ पाया गया। परिवेश से ऑक्साइड द्वारा परमाणुओं, अणुओं और आयनों के सोखने के कारण धीमी सतह की स्थिति ऑक्साइड परत के साथ जुड़ी हुई पाई गई। उत्तरार्द्ध बहुत अधिक संख्या में पाए गए थे और उनके पास बहुत अधिक विश्राम समय था। उस समय फिलो फ़ार्न्सवर्थ और अन्य परमाणु स्वच्छ अर्धचालक सतहों के उत्पादन के विभिन्न तरीकों के साथ आए थे।

1955 में, कार्ल फ्रॉश और लिंकन डेरिक ने गलती से सिलिकॉन वेफर की सतह को सिलिकॉन डाइऑक्साइड की एक परत के साथ ढ़क दिया। उन्होंने दिखाया कि ऑक्साइड की परत ने कुछ डोपेंट को सिलिकॉन वेफर में रोका, जबकि दूसरों को जाने की अनुमति दी, इस प्रकार अर्धचालक सतह पर ऑक्सीकरण के निष्क्रिय प्रभाव की खोज की।1957 में, उन्होंने एक शोध पत्र प्रकाशित किया और अपने काम को सारांशित करते हुए अपनी तकनीक का पेटेंट कराया। उनके द्वारा विकसित की गई तकनीक को ऑक्साइड डिफ्यूजन मास्किंग के रूप में जाना जाता है, जिसका उपयोग बाद में MOSFET उपकरणों के निर्माण में किया जाएगा। बेल लैब्स में, फ्रॉश की तकनीक के महत्व को तुरंत महसूस किया गया था। उनके काम के परिणाम 1957 में प्रकाशित होने से पहले बीटीएल मेमो के रूप में बेल लैब्स के आसपास प्रसारित किए गए थे। शॉक्ले अर्धचालक में, शॉक्ले ने दिसंबर 1956 में जीन होर्नी सहित अपने सभी वरिष्ठ कर्मचारियों को अपने लेख के प्रीप्रिंट को प्रसारित किया था।[6][13][14]1955 में, इयान मुनरो रॉस ने एक FeFET या MFSFET के लिए पेटेंट दायर किया।इसकी संरचना एक आधुनिक दूसरे चैनल MOSFET की तरह थी, लेकिन फेरोइलेक्ट्रिक सामग्री का उपयोग ऑक्साइड के बजाय एक ढ़के हुए/इन्सुलेटर के रूप में किया गया था। सालों पहले उन्होंने इसे फ्लोटिंग गेट मोसफेट से स्मृति के रूप में कल्पना की थी। फरवरी 1957 में, जॉन वॉलमार्क ने फील्ड-इफेक्ट ट्रांजिस्टर(FET) के लिए एक पेटेंट दायर किया, जिसमें जर्मेनियम मोनोऑक्साइड का उपयोग गेट डाइइलेक्ट्रिक के रूप में किया गया था। उसी वर्ष अपने अन्य पेटेंट में, उन्होंने एक डबल गेट (FET) का वर्णन किया। मार्च 1957 में, बेल लैब्स के एक शोध वैज्ञानिक, अर्नेस्टो लैबेट ने बाद में अपनी प्रयोगशाला नोटबुक में प्रस्तावित MOSFET के समान एक उपकरण की कल्पना की, हालांकि लैबेट के उपकरण में स्पष्ट रूप से सिलिकॉन डाइऑक्साइड का उपयोग एक इन्सुलेटर के रूप में नहीं किया था।[15][16][17][18]

मेटल-ऑक्साइड-सेमिकंडक्टर एफईटी (MOSFET)

1950 के दशक के अंत में मिस्र के इंजीनियर मोहम्मद अटला के काम से FET अनुसंधान में सफलता मिली।[3]1958 में उन्होंने प्रायोगिक कार्य प्रस्तुत किया, जिसमें दिखाया गया कि स्वच्छ सिलिकॉन सतह पर पतली सिलिकॉन ऑक्साइड बढ़ने से सतह की अवस्थाएँ बेअसर हो जाती है।इसे सतही निष्क्रियता के रूप में जाना जाता है, एक ऐसी विधि जो अर्धचालक उद्योग के लिए महत्वपूर्ण हो गई क्योंकि इसने सिलिकॉन एकीकृत परिपथों के बड़े पैमाने पर उत्पादन को संभव बना दिया।[19][20]मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर (MOSFET) का आविष्कार तब मोहम्मद अटला और दाऊन काहंग ने 1959 में किया था।[21][22] MOSFET ने बड़े पैमाने पर बाइपोलर ट्रांजिस्टर और JFET दोनों का स्थान लिया[2]और डिजिटल इलेक्ट्रॉनिक विकास पर इसका गहरा प्रभाव पड़ा।[23][22]इसकी उच्च मापनीयता और [24]बाइपोलर जंक्शन ट्रांजिस्टर की तुलना में बहुत कम बिजली की खपत और उच्च घनत्व के साथ[25] MOSFET ने उच्च घनत्व वाले एकीकृत परिपथों का निर्माण करना संभव बना दिया।[26] MOSFET भी JFET की तुलना में उच्च शक्ति को संभालने में सक्षम है।[27] MOSFET पहला सही मायने में कॉम्पैक्ट ट्रांजिस्टर था और व्यापक उपयोग के लिए बड़े पैमाने पर उत्पादित किया जा सकता था।[6]MOSFET कंप्यूटर, इलेक्ट्रॉनिक्स[20]और संचार प्रौद्योगिकी में सामान्य प्रकार का ट्रांजिस्टर बन गया।[28] यूएस पेटेंट और ट्रेडमार्क कार्यालय ने इसे एक अभूतपूर्व आविष्कार कहा जिसने दुनिया भर में जीवन और संस्कृति को बदल दिया।[28]

कॉम्प्लिमेंटरी एमओएस (CMOS), MOSFETS के लिए एक अर्धचालक उपकरण निर्माण प्रक्रिया, 1963 में फेयरचाइल्ड अर्धचालक में चिह-तांग साह और फ्रैंक वानलास द्वारा विकसित किया गया था।[29][30] फ्लोटिंग-गेट MOSFET की पहली रिपोर्ट 1967 में डॉन कांग और साइमन सेज़ द्वारा बनाई गई थी।[31] डबल-गेट MOSFET को पहली बार 1984 में इलेक्ट्रोटेक्निकल प्रयोगशाला शोधकर्ताओं तोशीहिरो सेकिगावा और युताका हयाशी द्वारा प्रदर्शित किया गया था।[32][33] FinFET (फिन फील्ड-इफेक्ट ट्रांजिस्टर), एक प्रकार का 3 डी नॉन-प्लानर मल्टी-गेट मोसफेट, जिसकी उत्पत्ति 1989 में हिताची सेंट्रल रिसर्च लेबोरेटरी में दीघ हिसामोटो और उनकी टीम के शोध से हुई थी।[34][35]

मूल जानकारी

FETS बहुसंख्यक-चार्ज-वाहक उपकरण हो सकते हैं, जिसमें करंट को मुख्य रूप से बहुसंख्यक वाहक, या अल्पसंख्यक-चार्ज-वाहक उपकरणों द्वारा ले जाया जाता है, जिसमें करंट मुख्य रूप से अल्पसंख्यक वाहक के प्रवाह के कारण होता है।[36] उपकरण में एक सक्रिय चैनल होता है, जिसके माध्यम से चार्ज वाहक, इलेक्ट्रॉनों या छेद स्रोत से ड्रेन में प्रवाहित होते हैं।स्रोत और ड्रेन टर्मिनल कंडक्टर ओमिक संपर्कों के माध्यम से अर्धचालक से जुड़े होते हैं।चैनल की चालकता गेट और स्रोत टर्मिनलों में लागू क्षमता का एक कार्य है।

FET के तीन टर्मिनल हैं:[37]

- स्रोत (S) जिसके माध्यम से वाहक चैनल में प्रवेश करते हैं।परंपरागत रूप से स्रोत(S) चैनल में प्रवेश करने वाला करंट IS द्वारा निर्दिष्ट किया जाता है।

- ड्रेन (D), जिसके माध्यम से वाहक चैनल छोड़ देते हैं।परंपरागत रूप से, डी पर चैनल में प्रवेश करने वाली धारा को आईडी द्वारा निर्दिष्ट किया जाता हैं। ड्रेन-से-स्रोत वोल्टेज VDS हैं।

- गेट (G), वह टर्मिनल जो चैनल चालकता को नियंत्रित करता है।वोल्टेज को जी(G) पर लागू करके, कोई भी आईडी(ID) को नियंत्रित कर सकता है।

टर्मिनलों के बारे में अधिक जानकारी

सभी एफईटी(FETs) में स्रोत, ड्रेन और गेट टर्मिनल होते हैं जो BJTS के एमिटर, कलेक्टर और बेस के अनुरूप होते हैं। अधिकांश एफईटी में एक चौथा टर्मिनल होता है जिसे बॉडी, बेस, बल्क या सब्सट्रेट कहा जाता है। यह चौथा टर्मिनल ट्रांजिस्टर को संचालन में पूर्वाग्रह करने का कार्य करता है सर्किट डिजाइनों में बॉडी टर्मिनल का गैर-तुच्छ उपयोग करना दुर्लभ है, लेकिन एक एकीकृत परिपथ के भौतिक लेआउट को स्थापित करते समय इसकी उपस्थिति महत्वपूर्ण है। गेट का आकार, आरेख में लंबाई L, स्रोत और ड्रेन के बीच की दूरी है, चौड़ाई आरेख में क्रॉस सेक्शन के लिए लंबवत दिशा में ट्रांजिस्टर का विस्तार है। 1माइक्रोन की एक गेट लंबाई, ऊपरी आवृत्ति को लगभग 5 गीगाहर्ट्ज, 0.2माइक्रोन को लगभग 30 गीगाहर्ट्ज तक सीमित करता है।

टर्मिनलों के नाम उनके कार्यों को संदर्भित करते हैं। गेट टर्मिनल को एक भौतिक गेट के उद्घाटन और समापन को नियंत्रित करने के रूप में माना जा सकता है। यह गेट इलेक्ट्रॉनों को स्रोत और ड्रेन के बीच एक चैनल बनाने या समाप्त करके उनके मार्ग को प्रवाहित करने या अवरुद्ध करने की अनुमति देता है। स्रोत टर्मिनल से ड्रेन टर्मिनल की ओर इलेक्ट्रॉन-प्रवाह एक लागू वोल्टेज से प्रभावित होता है। बॉडी केवल अर्धचालक के समूह को संदर्भित करता है जिसमें गेट, स्रोत और ड्रेन स्थित है। आमतौर पर बॉडी टर्मिनल FET के आधार पर, सर्किट के भीतर उच्चतम या निम्नतम वोल्टेज से जुड़ा होता है। बॉडी टर्मिनल और सोर्स टर्मिनल कभी-कभी एक साथ जुड़े होते हैं क्योंकि स्रोत अक्सर परिपथ(circuit) के भीतर उच्चतम या निम्नतम वोल्टेज से जुड़ा होता है, हालांकि एफईटी के कई उपयोग होते हैं जिनमें ऐसा विन्यास नहीं होता है, जैसे कि ट्रांसमिशन गेट और कैस्कोड सर्किट।

BJTS के विपरीत, FET के विशाल बहुमत विद्युत रूप से सममित हैं। इस प्रकार स्रोत और ड्रेन टर्मिनलों को व्यावहारिक सर्किट में आपस में बदला जा सकता है जिसमें परिचालन विशेषताओं या कार्य में कोई बदलाव नहीं होता है। यह भ्रामक हो सकता है जब एफईटी योजनाबद्ध आरेखों और सर्किटों में पीछे की ओर जुड़ा हुआ प्रतीत होता है, क्योंकि एफईटी के भौतिक अभिविन्यास को अन्य कारणों से तय किया गया था, जैसे कि मुद्रित सर्किट लेआउट।

करंट पर गेट वोल्टेज का प्रभाव

एफईटी गेट और सोर्स टर्मिनलों में लागू वोल्टेज से निर्मित और प्रभावित "प्रवाहकीय चैनल" के आकार को प्रभावित करके स्रोत से ड्रेन में इलेक्ट्रॉनों (या इलेक्ट्रॉन छेद) के प्रवाह को नियंत्रित करता है। प्रवाहकीय चैनल वह धारा है जिसके माध्यम से इलेक्ट्रॉन स्रोत से ड्रेन में प्रवाहित होते हैं।

एन-चैनल एफईटी

एन-चैनल "रिक्तीकरण मोड" उपकरण में, एक नकारात्मक गेट-टू-सोर्स वोल्टेज छोटे क्षेत्र को चौड़ाई में विस्तार करने और चैनल को संकीर्ण करने, पक्षों से चैनल पर अतिक्रमण करने का कारण बनता है। यदि सक्रिय क्षेत्र चैनल को पूरी तरह से बंद करने के लिए फैलता है, तो स्रोत से नाली तक चैनल का प्रतिरोध बड़ा हो जाता है और FET प्रभावी रूप से एक स्विच की तरह बंद हो जाता है। इसे "पिंच-ऑफ" कहा जाता है और जिस वोल्टेज पर यह होता है उसे "पिंच-ऑफ वोल्टेज"कहते है। इसके विपरीत, एक सकारात्मक गेट-टू-सोर्स वोल्टेज चैनल के आकार को बढ़ाता है और इलेक्ट्रॉनों को आसानी से प्रवाहित करने की अनुमति देता है (सही आंकड़ा देखें, जब एक चालन चैनल होता है और करंट ज्यादा होता है)।

एन-चैनल "वृद्धि मोड" उपकरण में एक प्रवाहकीय चैनल ट्रांजिस्टर के भीतर स्वाभाविक रूप से मौजूद नहीं होता है और जुड़ने के लिए एक सकारात्मक गेट-टू-सोर्स वोल्टेज आवश्यक है। सकारात्मक वोल्टेज बॉडी के भीतर मुक्त-अस्थायी इलेक्ट्रॉनों को गेट की ओर आकर्षित करता है, जिससे एक प्रवाहकीय चैनल बनता है। लेकिन पहले, FET के बॉडी में जोड़े गए डोपेंट आयनों का मुकाबला करने के लिए गेट के पास पर्याप्त इलेक्ट्रॉनों को आकर्षित किया जाना चाहिए यह एक ऐसा क्षेत्र बनाता है जिसमें कोई मोबाइल वाहक नहीं होता है जिसे कमी क्षेत्र कहा जाता है और जिस वोल्टेज पर ऐसा होता है, उसे FET के थ्रेशोल्ड वोल्टेज के रूप में संदर्भित किया जाता है। आगे गेट-टू-सोर्स वोल्टेज वृद्धि गेट की ओर और भी अधिक इलेक्ट्रॉनों को आकर्षित करेगी जो स्रोत से ड्रेन तक सक्रिय चैनल में सक्षम हैं, इस प्रक्रिया को इन्वर्स कहा जाता है।

पी-चैनल एफईटी

पी-चैनल की "वृद्धि मोड" उपकरण में, गेट से बॉडी तक एक सकारात्मक वोल्टेज गेट-इन्सुलेटर/अर्धचालक इंटरफ़ेस को इलेक्ट्रॉनों को मजबूर करके घटती हुई परत को चौड़ा करता है, जिससे स्थिर, सकारात्मक चार्ज स्वीकर्ता आयनों के वाहक-मुक्त क्षेत्र को उजागर किया जाता है।

इसके विपरीत, एक पी-चैनल वृद्धि मोड उपकरणों में, एक प्रवाहकीय क्षेत्र मौजूद नहीं है और एक चालन चैनल उत्पन्न करने के लिए नकारात्मक वोल्टेज का उपयोग किया जाना चाहिए।

चैनल पर ड्रेन-टू-सोर्स वोल्टेज का प्रभाव

गेट-टू-सोर्स वोल्टेज की तुलना में ड्रेन-टू-सोर्स वोल्टेज पर या तो वृद्धि- या रिक्तीकरण-मोड उपकरणों के लिए, गेट वोल्टेज को बदलने से चैनल प्रतिरोध में बदलाव आएगा और ड्रेन करंट ड्रेन वोल्टेज के लिए आनुपातिक होगा। इस मोड में FET एक चर अवरोधक की तरह काम करता है और FET को एक रैखिक मोड या ओमिक मोड में काम करने के लिए कहा जाता है।[38][39]यदि ड्रेन-टू-सोर्स वोल्टेज बढ़ाया जाता है, तो यह स्रोत से ड्रेन तक वोल्टेज क्षमता के एक ढाल के कारण चैनल के आकार में एक महत्वपूर्ण विषम परिवर्तन पैदा करता है। इन्वर्स क्षेत्र का आकार चैनल के ड्रेन के अंत के पास "पिंच-ऑफ" हो जाता है।यदि ड्रेन-टू-सोर्स वोल्टेज को और बढ़ाया जाता है, तो चैनल का पिंच-ऑफ पॉइंट ड्रन से स्रोत की ओर बढ़ना शुरू कर देता है।एफईटी (FET) को संतृप्ति मोड कहा जाता है,[40] हालांकि कुछ लेखक इसे बाइपोलर ट्रांजिस्टर ऑपरेटिंग क्षेत्रों के साथ बेहतर सादृश्य के लिए इसे सक्रिय मोड के रूप में संदर्भित करते हैं।[41][42] संतृप्ति मोड या ओमिक और संतृप्ति के बीच के क्षेत्र का उपयोग तब किया जाता है जब प्रवर्धन की आवश्यकता होती है। बीच के क्षेत्र को कभी-कभी ओमिक या रैखिक क्षेत्र का हिस्सा माना जाता है, जहां ड्रेन की धारा ड्रेन वोल्टेज के साथ लगभग रैखिक नहीं होती है।

भले ही गेट-टू-सोर्स वोल्टेज द्वारा गठित प्रवाहकीय चैनल अब संतृप्ति मोड के दौरान स्रोत को ड्रेन से नहीं जोड़ता है, वाहक बहने से अवरुद्ध नहीं होते हैं। फिर से एक एन-चैनल वृद्धि-मोड उपकरणों को ध्यान में रखते हुए, पी-टाइप बॉडी क्षेत्र में एक कमी मौजूद करता है, जो प्रवाहकीय चैनल , ड्रेन और स्रोत क्षेत्रों के आसपास है। चैनल को शामिल करने वाले इलेक्ट्रॉन रिक्त क्षेत्र के माध्यम से चैनल से बाहर जाने के लिए स्वतंत्र है यदि ड्रेन-से-स्रोत वोल्टेज द्वारा ड्रेन की ओर आकर्षित किया जाता है। अवक्षय क्षेत्र वाहकों से मुक्त होता है और इसमें सिलिकॉन के समान प्रतिरोध होता है ड्रेन-टू-सोर्स वोल्टेज की कोई भी वृद्धि ड्रेन से पिंच-ऑफ पॉइंट तक की दूरी को बढ़ाएगी, जिससे ड्रेन-टू-सोर्स वोल्टेज के अनुपात में अवक्षय क्षेत्र के प्रतिरोध में वृद्धि होगी। यह आनुपातिक परिवर्तन ड्रेन-से-स्रोत करंट को अपेक्षाकृत निश्चित रूप से स्थिर रहने का कारण बनता है, ड्रेन-टू-सोर्स वोल्टेज में परिवर्तन से स्वतंत्र, संचालन के रैखिक मोड में इसके ओमिक व्यवहार के विपरीत इस प्रकार संतृप्ति मोड में एफईटी एक अवरोधक के बजाय एक निरंतर-वर्तमान स्रोत के रूप में व्यवहार करता है और प्रभावी रूप से वोल्टेज एम्पलीफायर के रूप में उपयोग किया जा सकता है। इस मामले में, गेट-टू-सोर्स वोल्टेज चैनल के माध्यम से निरंतर करंट के स्तर को निर्धारित करता है।

संयोजन

एफईटी का निर्माण विभिन्न अर्धचालकों से किया जा सकता है, जिनमें से सिलिकॉन अब तक का सबसे आम तरीका है।अधिकांश एफईटी पारंपरिक थोक अर्धचालक प्रसंस्करण तकनीकों का उपयोग करके, सक्रिय क्षेत्र या चैनल के रूप में एकल क्रिस्टल अर्धचालक वेफर का उपयोग करके बनाए जाते हैं।

अधिक असामान्य बॉडी सामग्री में ऐमौरफस सिलिकॉन, पॉलीक्रिस्टलाइन सिलिकॉन या थिन-फिल्म ट्रांजिस्टर या औरगैनिक फिल्ड-एफेकट ट्रांजिस्टर (OFETs) में अन्य ऐमौरफस अर्धचालक हैं जो कार्बनिक अर्धचालकों पर आधारित हैं,अक्सर ओएफईटी गेट इंसुलेटर और इलेक्ट्रोड कार्बनिक पदार्थों से बने होते हैं इस तरह के FETs को सिलिकॉन कार्बाइड (SiC), गैलियम आर्सेनाइड (GaAs), गैलियम नाइट्राइड (GaN) और इंडियम गैलियम आर्सेनाइड (InGaAs) जैसी विभिन्न सामग्रियों का उपयोग करके निर्मित किया जाता है।

जून 2011 में, आईबीएम (IBM)ने घोषणा की कि,उसने एक एकीकृत परिपथ में ग्राफीन-आधारित एफईटीएस का सफलतापूर्वक उपयोग किया था।[43][44] ये ट्रांजिस्टर लगभग 2.23 (GHz)गीगाहर्ट्ज़ कटऑफ आवृत्ति के लिए सक्षम हैं, जो मानक सिलिकॉन एफईटी(FETs) से बहुत अधिक है।[45]

प्रकार

एक एफईटी के चैनल को एन-टाइप अर्धचालकों या पी-टाइप अर्धचालकों का उत्पादन करने के लिए डोप किया जाता है। वृद्धि मोड एफईटी के मामले में, ड्रेन और स्रोत को चैनल के विपरीत प्रकार से डोप किया जा सकता है, या चैनल के समान प्रकार से डोप किया जा सकता है, जैसे कि मोड फेट्स के रूप में। फील्ड-इफेक्ट ट्रांजिस्टर भी चैनल और गेट के बीच इन्सुलेशन की विधि द्वारा प्रतिष्ठित हैं। FETs के प्रकारों में शामिल हैं:

- MOSFET (मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) गेट और बॉडी के बीच एक इन्सुलेटर का उपयोग करता है (आमतौर पर SiO2)। यह अब तक का सबसे आम प्रकार है।

- DGMOSFET (डुअल-गेट मेटल-ऑक्साइड-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) या DGMOS, एक MOSFET जिसमें दो इंसुलेटेड गेट होते हैं।

- IGBT (इंसुलेटेड-गेट बाइपोलर ट्रांजिस्टर) बिजली नियंत्रण के लिए एक उपकरण है।इसकी संरचना एक MOSFET जैसी है जो एक बाइपोलर जैसे मुख्य चालन चैनल के साथ युग्मित है।आमतौर पर संचालन के 200-3000 V ड्रेन-टू-सोर्स वोल्टेज रेंज के लिए उपयोग किए जाते है।पावर MOSFETS अभी भी 1से200 V के ड्रेन-से-स्रोत वोल्टेज के लिए पसंदीदा उपकरण है।

- JLNT (जंक्शनलेस नैनोवायर ट्रांजिस्टर) एक प्रकार का फील्ड-इफेक्ट ट्रांजिस्टर (FET) है जिस चैनल में अनेक नैनोवायर है और किसी भी जंक्शन को प्रस्तुत नहीं करता है।

- MNOS (मेटल-नाइट्राइड-ऑक्साइड-सेमीकंडक्टर ट्रांजिस्टर) गेट और बॉडी के बीच एक नाइट्राइड-ऑक्साइड परत इन्सुलेटर का उपयोग करता है।

- ISFET (आयन सेंनसिटीव फिल्ड-एफेकट ट्रांजिस्टर) का उपयोग समाधान में आयन सांद्रता को मापने के लिए किया जा सकता है जब आयन सांद्रता (H+, pH इलेक्ट्रोड देखें) में परिवर्तन होता है, तो ट्रांजिस्टर के माध्यम से प्रवाहित धारा तदनुसार बदल जाएगी।

- BioFET (बायोलाजिकल सेंनसिटीव फिल्ड-एफेकट ट्रांजिस्टर) ISFET तकनीक पर आधारित सेंसर/बायोसेंसर का एक वर्ग है, जिसका उपयोग आवेशित अणुओं का पता लगाने के लिए किया जाता है,जब एक आवेशित अणु मौजूद हो तो बायोफेट(BioFET) सतह पर इलेक्ट्रोस्टैटिक क्षेत्र में परिवर्तन ट्रांजिस्टर के माध्यम से करंट में एक औसत दर्जे का परिवर्तन होता है।इनमें एंजाइम संशोधित FETs (ENFETs), इम्यूनोलॉजिकल रूप से संशोधित FETs(ImmunoFETs), जीन-संशोधित FETS (GenFETs), DNAFETs, सेल-आधारित बायोफेट (CPFETs), बीटल/चिप FETs (BeetleFETs) और आयन-चैनलों पर आधारित एफईटी (FETs) शामिल हैं।[46]

- DNAFET (डीएनए फील्ड-इफेक्ट ट्रांजिस्टर) एक विशेष FET है जो कि डीएनए स्ट्रैंड्स का पता लगाने के लिए सिंगल-स्ट्रैंड डीएनए अणुओं से बने गेट का उपयोग करके बायोसेंसर के रूप में कार्य करता है।

- GAAFET या गेट-ऑल-अराउंड FET सहित finFET शामिल है, जिसका उपयोग उच्च घनत्व प्रोसेसर चिप्स पर किया जाता हैं।

- JFET (जंक्शन फील्ड-इफेक्ट ट्रांजिस्टर) बॉडी से गेट को अलग करने के लिए एक रिवर्स बायस्ड पी-एन जंक्शन का उपयोग करता है।

- SIT (स्टेटिक इंडक्शन ट्रांजिस्टर) एक छोटे चैनल वाले JFET का एक प्रकार है।

- DEPFET एक FET है जो पूरी तरह से समाप्त सब्सट्रेट में बनता है और एक ही समय में सेंसर, एम्पलीफायर और मेमोरी नोड के रूप में कार्य करता है। इसका उपयोग इमेज (फोटॉन) सेंसर के रूप में किया जा सकता है।

- FREDFET (फास्ट-रिवर्स या फास्ट-रिकवरी एपिटैक्सियल डायोड FET) एक विशेष FET है जिसे बॉडी डायोड की एक बहुत तेजी से रिकवरी (टर्न-ऑफ) प्रदान करने के लिए डिज़ाइन किया गया है, जो इसे इलेक्ट्रिक मोटर्स, जैसे आगमनात्मक भार विशेष रूप से मध्यम- संचालित ब्रशलेस डीसी मोटर्स चलाने के लिए सुविधाजनक बनाता है।

- HIGFET (हेटरोस्ट्रक्चर इंसुलेटेड-गेट फील्ड-इफेक्ट ट्रांजिस्टर) का उपयोग मुख्य रूप से अनुसंधान में किया जाता है।[47]

- MODFET (मॉड्यूलेशन-डॉप्ड फील्ड-इफेक्ट ट्रांजिस्टर)

- एक उच्च-इलेक्ट्रॉन-मोबिलिटी ट्रांजिस्टर है,जो सक्रिय क्षेत्र के ग्रेडेड डोपिंग द्वारा गठित क्वांटम अच्छी तरह से संरचना का उपयोग करता है।

- TFET (टनल फील्ड-इफेक्ट ट्रांजिस्टर) बैंड-टू-बैंड टनलिंग पर आधारित है।[48]

- TQFET (टोपोलॉजिकल क्वांटम फील्ड-इफेक्ट ट्रांजिस्टर) एक 2डी सामग्री को अपव्यय रहित टोपोलॉजिकल इंसुलेटर ('ऑन' स्टेट) से पारंपरिक इंसुलेटर ('ऑफ' स्टेट) में एक लागू विद्युत क्षेत्र का उपयोग करके स्विच करता है।

- HEMT (हाई-इलेक्ट्रॉन-मोबिलिटी ट्रांजिस्टर), जिसे HFET (हेटरोस्ट्रक्चर FET) भी कहा जाता है, AlGaAs जैसे एक टर्नरी सेमीकंडक्टर में बैंडगैप इंजीनियरिंग का उपयोग करके बनाया जा सकता है।पूरी तरह से समाप्त वाइड-बैंड-गैप सामग्री गेट और बॉडी के बीच अलगाव बनाती है।

- MESFET ( मेटल-सेमिकंडक्टर फील्ड-इफेक्ट ट्रांजिस्टर) एक शोट्की (Schottky) बैरियर के साथ जेएफईटी के पी-एन जंक्शन को प्रतिस्थापित करता है और GaAs और अन्य III-V अर्धचालक सामग्री में उपयोग किया जाता है।

- NOMFET एक नैनोपार्टिकल ऑर्गेनिक मेमोरी फील्ड-इफेक्ट ट्रांजिस्टर है।[49]

- GNRFET (ग्राफीन नैनोरिबोन फ़ील्ड-इफेक्ट ट्रांजिस्टर) अपने चैनल के लिए एक ग्राफीन नैनोरिबोन का उपयोग करता है।[50]

- VESFET (वर्टिकल-स्लिट फील्ड-इफेक्ट ट्रांजिस्टर) एक चौकोर आकार का जंक्शन रहित FET है जिसमें एक संकीर्ण स्लिट है जो स्रोत को जोड़ता है और विपरीत कोनों पर ड्रेन को जोड़ता है।दो गेट दूसरे कोनों पर कब्जा करते हैं और स्लिट के माध्यम से करंट को नियंत्रित करते हैं।[51]

- CNTFET (कार्बन नैनोट्यूब फील्ड-इफेक्ट ट्रांजिस्टर)।

- OFET (ऑर्गेनिक फील्ड-इफेक्ट ट्रांजिस्टर) अपने चैनल में एक ऑर्गेनिक अर्धचालक का उपयोग करता है।

- QFET (क्वांटम फील्ड इफेक्ट ट्रांजिस्टर) पारंपरिक ट्रांजिस्टर के इलेक्ट्रॉन चालन क्षेत्र को समाप्त करके ट्रांजिस्टर संचालन की गति को बढ़ाने के लिए क्वांटम टनलिंग का लाभ उठाता है।

- SB-FET (स्कॉट्की-बैरियर फील्ड-इफेक्ट ट्रांजिस्टर) धातु के स्रोत और ड्रेन कॉन्टैक्ट इलेक्ट्रोड के साथ एक फील्ड-इफेक्ट ट्रांजिस्टर है, जो सोर्स-चैनल और ड्रेन-चैनल इंटरफेस दोनों में शोट्की(Schottky) बैरियर बनाते हैं।[52]