संख्यात्मक रूप से नियंत्रित दोलित्र: Difference between revisions

No edit summary |

No edit summary |

||

| (3 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{short description|Digital signal generator}} | {{short description|Digital signal generator}} | ||

एक '''संख्यात्मक रूप से नियंत्रित दोलित्र | एक '''संख्यात्मक रूप से नियंत्रित दोलित्र (एनसीओ)''' एक डिजिटल [[ संकेतक उत्पादक |संकेतक उत्पादक]] है जो एक [[तुल्यकालिक सर्किट]] (अर्थात, क्लॉक्ड), असतत-समय, एक [[तरंग]] के असतत-मूल्यवान प्रतिनिधित्व, सामान्यतः [[sinusoidal|साइनसॉइडल]] बनाता है।<ref name="IEEE">{{cite book |last=Radatz |first=J. |title=इलेक्ट्रिकल और इलेक्ट्रॉनिक्स शर्तों का IEEE मानक शब्दकोश|publisher=IEEE Standards Office |location=New York, NY |year=1997 }}</ref> इस प्रकार [[प्रत्यक्ष डिजिटल सिंथेसाइज़र]] (डीडीएस) बनाने के लिए एनसीओ अधिकांशतः आउटपुट पर [[डिज़िटल से एनालॉग कन्वर्टर]] (डीएसी) के संयोजन के साथ प्रयोग किया जाता है।{{#tag:ref|While some authors use the terms DDS and NCO interchangeably,<ref name="latticeSC" /> by convention an NCO refers to the digital (i.e. the discrete-time, discrete amplitude) portion of a DDS<ref name="IEEE"/>}} | ||

संख्यात्मक रूप से नियंत्रित ऑसिलेटर चपलता, त्रुटिहीनता, स्थिरता और विश्वसनीयता की स्थितियों में अन्य प्रकार के ऑसिलेटर की तुलना में कई फायदे प्रदान करते हैं।<ref name="latticeSC">{{ cite web | title = संख्यात्मक रूप से नियंत्रित थरथरानवाला| url = http://www.latticesemi.com/Products/DesignSoftwareAndIP/IntellectualProperty/IPCore/IPCores02/NumericallyControlledOscillator.aspx | publisher = Lattice Semiconductor Corporation | year = 2009 }}</ref> इस प्रकार एनसीओ का उपयोग कई संचार प्रणालियों में किया जाता है, जिसमें 3जी वायरलेस और सॉफ्टवेयर रेडियो सिस्टम, डिजिटल [[ चरण बंद लूप ]], रडार सिस्टम, ऑप्टिकल या ध्वनिक ट्रांसमिशन के लिए ड्राइवर और मल्टीलेवल [[ आवृत्ति पारी कुंजीयन ]]/[[ चरण-शिफ्ट कुंजीयन ]] मॉड्यूलेटर/डीमोडुलेटर में उपयोग किए जाने वाले डिजिटल अप/डाउन कन्वर्टर्स सम्मिलित हैं।<ref name="latticeSC"/> | संख्यात्मक रूप से नियंत्रित ऑसिलेटर चपलता, त्रुटिहीनता, स्थिरता और विश्वसनीयता की स्थितियों में अन्य प्रकार के ऑसिलेटर की तुलना में कई फायदे प्रदान करते हैं।<ref name="latticeSC">{{ cite web | title = संख्यात्मक रूप से नियंत्रित थरथरानवाला| url = http://www.latticesemi.com/Products/DesignSoftwareAndIP/IntellectualProperty/IPCore/IPCores02/NumericallyControlledOscillator.aspx | publisher = Lattice Semiconductor Corporation | year = 2009 }}</ref> इस प्रकार एनसीओ का उपयोग कई संचार प्रणालियों में किया जाता है, जिसमें 3जी वायरलेस और सॉफ्टवेयर रेडियो सिस्टम, डिजिटल [[ चरण बंद लूप |चरण बंद लूप]] , रडार सिस्टम, ऑप्टिकल या ध्वनिक ट्रांसमिशन के लिए ड्राइवर और मल्टीलेवल [[ आवृत्ति पारी कुंजीयन |आवृत्ति पारी कुंजीयन]] /[[ चरण-शिफ्ट कुंजीयन | चरण-शिफ्ट कुंजीयन]] मॉड्यूलेटर/डीमोडुलेटर में उपयोग किए जाने वाले डिजिटल अप/डाउन कन्वर्टर्स सम्मिलित हैं।<ref name="latticeSC"/> | ||

== ऑपरेशन == | == ऑपरेशन == | ||

| Line 10: | Line 10: | ||

*एक चरण-से-आयाम कनवर्टर (पीएसी), जो चरण संचायक आउटपुट शब्द (चरण शब्द) का उपयोग सामान्यतः एक तरंगरूप [[तालिका देखो]] (एलयूटी) में एक सूचकांक के रूप में करता है जिससे कि एक समान आयाम नमूना प्रदान किया जा सके। कभी-कभी उत्तम त्रुटिहीनता प्रदान करने और चरण त्रुटि शोर को कम करने के लिए लुक-अप तालिका के साथ रैखिक इंटरपोलेशन का उपयोग किया जाता है। इस प्रकार चरण को आयाम में परिवर्तित करने के अन्य तरीके, गणितीय एल्गोरिदम जैसे कि बिजली श्रृंखला का उपयोग किया जा सकता है, विशेष रूप से एक सॉफ्टवेयर एनसीओ में किया जाता हैं। | *एक चरण-से-आयाम कनवर्टर (पीएसी), जो चरण संचायक आउटपुट शब्द (चरण शब्द) का उपयोग सामान्यतः एक तरंगरूप [[तालिका देखो]] (एलयूटी) में एक सूचकांक के रूप में करता है जिससे कि एक समान आयाम नमूना प्रदान किया जा सके। कभी-कभी उत्तम त्रुटिहीनता प्रदान करने और चरण त्रुटि शोर को कम करने के लिए लुक-अप तालिका के साथ रैखिक इंटरपोलेशन का उपयोग किया जाता है। इस प्रकार चरण को आयाम में परिवर्तित करने के अन्य तरीके, गणितीय एल्गोरिदम जैसे कि बिजली श्रृंखला का उपयोग किया जा सकता है, विशेष रूप से एक सॉफ्टवेयर एनसीओ में किया जाता हैं। | ||

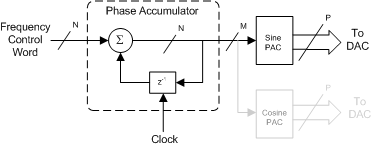

[[Image:Generic NCO.png|frame|चित्रा 1: वैकल्पिक चतुर्भुज आउटपुट के साथ संख्यात्मक रूप से नियंत्रित ऑसीलेटर]]जब क्लॉक किया जाता है, तो चरण संचायक (पीए) [[मॉड्यूल ऑपरेशन|मॉड्यूलो-2एन]] सॉटूथ वेवफॉर्म तरंग बनाता है | [[Image:Generic NCO.png|frame|चित्रा 1: वैकल्पिक चतुर्भुज आउटपुट के साथ संख्यात्मक रूप से नियंत्रित ऑसीलेटर]]जब क्लॉक किया जाता है, तो चरण संचायक (पीए) [[मॉड्यूल ऑपरेशन|मॉड्यूलो-2एन]] सॉटूथ वेवफॉर्म तरंग बनाता है जिसे फिर चरण-से-आयाम कनवर्टर (पीएसी) द्वारा एक सैंपल साइनसॉइड में परिवर्तित किया जाता है, जहां एन चरण संचायक में ले जाए गए बिट्स की संख्या है। इस प्रकार एन एनसीओ आवृत्ति रेज़ोल्यूशन सेट करता है और सामान्यतः पीएसी लुक-अप टेबल की मेमोरी स्पेस को परिभाषित करने वाली बिट्स की संख्या से अधिक बड़ा होता है। यदि पीएसी की क्षमता 2एम है, तो पीए आउटपुट शब्द को चित्र 1 में दिखाए अनुसार एम बिट्स में छोटा किया जाना चाहिए। इस प्रकार चूंकि, कटे हुए बिट्स को इंटरपोलेशन के लिए उपयोग किया जा सकता है। चरण आउटपुट शब्द का ट्रंकेशन आवृत्ति त्रुटिहीनता को प्रभावित नहीं करता है किन्तु एक समय-भिन्न आवधिक चरण त्रुटि उत्पन्न करता है जो नकली उत्पादों का प्राथमिक स्रोत है। इस प्रकार एक और नकली उत्पाद निर्माण तंत्र पीएसी आउटपुट (आयाम) शब्द का परिमित शब्द लंबाई प्रभाव है।<ref name="kroupa">{{cite book |last=Kroupa |first=V. F. |title=डायरेक्ट डिजिटल फ़्रीक्वेंसी सिंथेसाइज़र|publisher=IEEE Press |year=1999 |isbn=0-7803-3438-8}}</ref> | ||

इस प्रकार घड़ी की आवृत्ति के सापेक्ष आवृत्ति त्रुटिहीनता केवल चरण की गणना करने के लिए उपयोग किए जाने वाले अंकगणित की त्रुटिहीनता से सीमित होती है।<ref name="kroupa"/> | इस प्रकार घड़ी की आवृत्ति के सापेक्ष आवृत्ति त्रुटिहीनता केवल चरण की गणना करने के लिए उपयोग किए जाने वाले अंकगणित की त्रुटिहीनता से सीमित होती है।<ref name="kroupa"/> | ||

एनसीओ चरण- और आवृत्ति-चतुर हैं, और उपयुक्त नोड पर योग द्वारा [[ चरण मॉडुलन |चरण मॉडुलन]] या [[ आवृति का उतार - चढ़ाव |आवृति का उतार - चढ़ाव]] आउटपुट का उत्पादन करने के लिए तुच्छ रूप से संशोधित किया जा सकता है, या चित्र में दिखाए अनुसार [[चतुर्भुज चरण]] आउटपुट प्रदान करने के लिए साधारण | एनसीओ चरण- और आवृत्ति-चतुर हैं, और उपयुक्त नोड पर योग द्वारा [[ चरण मॉडुलन |चरण मॉडुलन]] या [[ आवृति का उतार - चढ़ाव |आवृति का उतार - चढ़ाव]] आउटपुट का उत्पादन करने के लिए तुच्छ रूप से संशोधित किया जा सकता है, या चित्र में दिखाए अनुसार [[चतुर्भुज चरण]] आउटपुट प्रदान करने के लिए साधारण रूप से संशोधित किया जा सकता है। | ||

== चरण संचायक == | == चरण संचायक == | ||

<!-- linked from redirect [[Phase accumulator]] --> | <!-- linked from redirect [[Phase accumulator]] --> | ||

एक बाइनरी चरण संचायक में एक एन-बिट बाइनरी [[योजक (इलेक्ट्रॉनिक्स)]] और एक [[हार्डवेयर रजिस्टर]] होता है, जैसा कि चित्र 1 में दिखाया गया है।<ref name="Grzeg"/> इस प्रकार प्रत्येक घड़ी चक्र एक नया एन-बिट आउटपुट उत्पन्न करता है जिसमें आवृत्ति | एक बाइनरी चरण संचायक में एक एन-बिट बाइनरी [[योजक (इलेक्ट्रॉनिक्स)]] और एक [[हार्डवेयर रजिस्टर]] होता है, जैसा कि चित्र 1 में दिखाया गया है।<ref name="Grzeg"/> इस प्रकार प्रत्येक घड़ी चक्र एक नया एन-बिट आउटपुट उत्पन्न करता है जिसमें आवृत्ति कंट्रोल वर्ड (एफसीडब्ल्यू) के साथ रजिस्टर से प्राप्त पिछले आउटपुट सम्मिलित होते हैं जो किसी दिए गए आउटपुट आवृत्ति के लिए स्थिर होते हैं। परिणामी आउटपुट तरंग चरण आकार के साथ एक सीढ़ी है <math>\Delta F</math>, एफसीडब्ल्यू का पूर्णांक मान हैं।<ref name="ADI"/> इस प्रकार कुछ कॉन्फ़िगरेशन में, चरण आउटपुट रजिस्टर के आउटपुट से लिया जाता है जो एक घड़ी चक्र [[विलंबता (इंजीनियरिंग)]] प्रस्तुत करता है किन्तु योजक को उच्च घड़ी दर पर संचालित करने की अनुमति देता है।<ref name="latticeSC"/> | ||

[[Image:Phase Accum Graph.png|frame|चित्रा 2: सामान्यीकृत चरण संचायक आउटपुट]]योजक को अतिप्रवाह करने के लिए डिज़ाइन किया गया है जब इसके ऑपरेंड के पूर्ण मूल्य का योग इसकी क्षमता से अधिक हो जाता है (2<sup>एन</sup>-1). अतिप्रवाह बिट को छोड़ दिया जाता है, इसलिए आउटपुट शब्द की चौड़ाई हमेशा इसकी इनपुट शब्द चौड़ाई के बराबर होती है। शेष <math>\phi _n</math>, जिसे अवशिष्ट कहा जाता है, रजिस्टर में संग्रहीत किया जाता है और इस समय से चक्र दोहराता है <math>\phi _n</math> (चित्र 2 देखें)।<ref name="Grzeg"/> इस प्रकार चूंकि एक चरण संचायक एक परिमित राज्य मशीन है, अंततः कुछ नमूना के पर अवशिष्ट को प्रारंभिक मूल्य पर वापस आना चाहिए <math>\phi _0</math>. अंतराल K को दी गई भव्य पुनरावृत्ति दर (GRR) के रूप में संदर्भित किया जाता है। | [[Image:Phase Accum Graph.png|frame|चित्रा 2: सामान्यीकृत चरण संचायक आउटपुट]]योजक को अतिप्रवाह करने के लिए डिज़ाइन किया गया है जब इसके ऑपरेंड के पूर्ण मूल्य का योग इसकी क्षमता से अधिक हो जाता है (2<sup>एन</sup>-1). अतिप्रवाह बिट को छोड़ दिया जाता है, इसलिए आउटपुट शब्द की चौड़ाई हमेशा इसकी इनपुट शब्द चौड़ाई के बराबर होती है। शेष <math>\phi _n</math>, जिसे अवशिष्ट कहा जाता है, रजिस्टर में संग्रहीत किया जाता है और इस समय से चक्र दोहराता है <math>\phi _n</math> (चित्र 2 देखें)।<ref name="Grzeg"/> इस प्रकार चूंकि एक चरण संचायक एक परिमित राज्य मशीन है, अंततः कुछ नमूना के पर अवशिष्ट को प्रारंभिक मूल्य पर वापस आना चाहिए <math>\phi _0</math>. अंतराल K को दी गई भव्य पुनरावृत्ति दर (GRR) के रूप में संदर्भित किया जाता है। | ||

:<math>\mbox{GRR}=\frac{2^N}{\mbox{GCD}(\Delta F,2^N)}</math> | :<math>\mbox{GRR}=\frac{2^N}{\mbox{GCD}(\Delta F,2^N)}</math> | ||

| Line 27: | Line 27: | ||

समीकरण (1) से पता चलता है कि चरण संचायक को विभाजित अनुपात के प्रोग्राम योग्य गैर-पूर्णांक आवृत्ति विभाजक के रूप में माना जा सकता है <math>\Delta F/2^N</math>.<ref name= "kroupa"/> | समीकरण (1) से पता चलता है कि चरण संचायक को विभाजित अनुपात के प्रोग्राम योग्य गैर-पूर्णांक आवृत्ति विभाजक के रूप में माना जा सकता है <math>\Delta F/2^N</math>.<ref name= "kroupa"/> | ||

== चरण-से-आयाम कनवर्टर == | == चरण-से-आयाम कनवर्टर == | ||

'''चरण-आयाम कनवर्टर''' पीए से प्राप्त ट्रंकेटेड चरण आउटपुट शब्द से नमूना-डोमेन तरंग बनाता है। पीएसी एक साधारण [[ केवल पढ़ने के लिये मेमोरी ]] हो सकती है जिसमें 2 होते हैं<sup>M</sup> वांछित आउटपुट तरंग के सन्निहित नमूने जो सामान्यतः एक साइनसॉइड होता है। इस प्रकार चूंकि अधिकांशतः, आवश्यक मेमोरी की मात्रा को कम करने के लिए विभिन्न तरकीबें अपनाई जाती हैं। इसमें विभिन्न त्रिकोणमितीय विस्तार सम्मिलित हैं,<ref>{{ cite patent | inventor-last = Miller | inventor-first = B. M. | issue-date = October 14, 2008 | title = संख्यात्मक रूप से नियंत्रित दोलक और संचालन की विधि| country-code = US | patent-number = 7437391 }}</ref> त्रिकोणमितीय सन्निकटन<ref name="Grzeg">{{ cite web | first1 = G. | last1 = Popek | first2 = M. | last2 = Kampik | title = टेलर सीरीज सन्निकटन का उपयोग करते हुए लो-स्पर संख्यात्मक रूप से नियंत्रित ऑसिलेटर| url = http://mechatronika.polsl.pl/owd/pdf2009/030.pdf | date = October 2009 | work = XI International PhD Workshop OWD 2009 | publisher = Silesian University of Technology | location = Gliwice, Poland }}</ref> और विधियाँ जो साइनसोइड्स द्वारा प्रदर्शित चतुर्भुज समरूपता का लाभ उठाती हैं।<ref>{{ cite patent | inventor1-last = McCallister | inventor1-first = R. D. | inventor2-last = Shearer | inventor2-first = D. | publication-date = 12/04/1984 | title = चतुर्थांश प्रतिकृति और फ़ंक्शन अपघटन का उपयोग करके संख्यात्मक रूप से नियंत्रित ऑसिलेटर| country-code = US | patent-number = 4486846 }}</ref> वैकल्पिक रूप से, पीएसी में [[रैंडम एक्सेस मेमोरी]] सम्मिलित हो सकती है जिसे [[मनमाना तरंग जनरेटर]] बनाने के लिए वांछित रूप से भरा जा सकता है। | '''चरण-आयाम कनवर्टर''' पीए से प्राप्त ट्रंकेटेड चरण आउटपुट शब्द से नमूना-डोमेन तरंग बनाता है। पीएसी एक साधारण [[ केवल पढ़ने के लिये मेमोरी |केवल पढ़ने के लिये मेमोरी]] हो सकती है जिसमें 2 होते हैं<sup>M</sup> वांछित आउटपुट तरंग के सन्निहित नमूने जो सामान्यतः एक साइनसॉइड होता है। इस प्रकार चूंकि अधिकांशतः, आवश्यक मेमोरी की मात्रा को कम करने के लिए विभिन्न तरकीबें अपनाई जाती हैं। इसमें विभिन्न त्रिकोणमितीय विस्तार सम्मिलित हैं,<ref>{{ cite patent | inventor-last = Miller | inventor-first = B. M. | issue-date = October 14, 2008 | title = संख्यात्मक रूप से नियंत्रित दोलक और संचालन की विधि| country-code = US | patent-number = 7437391 }}</ref> त्रिकोणमितीय सन्निकटन<ref name="Grzeg">{{ cite web | first1 = G. | last1 = Popek | first2 = M. | last2 = Kampik | title = टेलर सीरीज सन्निकटन का उपयोग करते हुए लो-स्पर संख्यात्मक रूप से नियंत्रित ऑसिलेटर| url = http://mechatronika.polsl.pl/owd/pdf2009/030.pdf | date = October 2009 | work = XI International PhD Workshop OWD 2009 | publisher = Silesian University of Technology | location = Gliwice, Poland }}</ref> और विधियाँ जो साइनसोइड्स द्वारा प्रदर्शित चतुर्भुज समरूपता का लाभ उठाती हैं।<ref>{{ cite patent | inventor1-last = McCallister | inventor1-first = R. D. | inventor2-last = Shearer | inventor2-first = D. | publication-date = 12/04/1984 | title = चतुर्थांश प्रतिकृति और फ़ंक्शन अपघटन का उपयोग करके संख्यात्मक रूप से नियंत्रित ऑसिलेटर| country-code = US | patent-number = 4486846 }}</ref> वैकल्पिक रूप से, पीएसी में [[रैंडम एक्सेस मेमोरी]] सम्मिलित हो सकती है जिसे [[मनमाना तरंग जनरेटर]] बनाने के लिए वांछित रूप से भरा जा सकता है। | ||

== नकली उत्पाद == | == नकली उत्पाद == | ||

| Line 44: | Line 44: | ||

:<math>\zeta _{max} \approx -6.02 \cdot P\;\mbox{dBc}.</math> | :<math>\zeta _{max} \approx -6.02 \cdot P\;\mbox{dBc}.</math> | ||

एक अन्य संबंधित नकली उत्पादन विधि ऊपर उल्लिखित जीआरआर के कारण साधारण | एक अन्य संबंधित नकली उत्पादन विधि ऊपर उल्लिखित जीआरआर के कारण साधारण मॉडुलन है। इन स्पर्स का आयाम बड़े एन के लिए कम है और उनकी आवृत्ति सामान्यतः पता लगाने योग्य होने के लिए बहुत कम है किन्तु वे कुछ अनुप्रयोगों के लिए समस्याएँ उत्पन्न कर सकते हैं।<ref name="Grzeg"/> | ||

एड्रेस लुकअप में ट्रंकेशन को कम करने का एक विधि यह है कि समानांतर में कई छोटी लुकअप टेबल हों और टेबल में इंडेक्स करने के लिए ऊपरी बिट्स का उपयोग किया जाए और निचले बिट्स को रैखिक या द्विघात प्रक्षेप के लिए तौला जाए। इस प्रकार अर्थात दो 16-बिट एलयूटीएस में देखने के लिए 24-बिट चरण संचायक का उपयोग करें। काटे गए 16 एमएसबी में पता, और वह प्लस 1. वजन के रूप में 8 एलएसबी का उपयोग करके रैखिक रूप से प्रक्षेपित करें। (इसके अतिरिक्त कोई 3 एलयूटीएस का उपयोग कर सकता है और द्विघात रूप से प्रक्षेपित कर सकता है)। यह कुछ मल्टीप्लायरों की कीमत पर स्मृति की समान मात्रा के लिए घटी हुई विकृति का परिणाम हो सकता है। | एड्रेस लुकअप में ट्रंकेशन को कम करने का एक विधि यह है कि समानांतर में कई छोटी लुकअप टेबल हों और टेबल में इंडेक्स करने के लिए ऊपरी बिट्स का उपयोग किया जाए और निचले बिट्स को रैखिक या द्विघात प्रक्षेप के लिए तौला जाए। इस प्रकार अर्थात दो 16-बिट एलयूटीएस में देखने के लिए 24-बिट चरण संचायक का उपयोग करें। काटे गए 16 एमएसबी में पता, और वह प्लस 1. वजन के रूप में 8 एलएसबी का उपयोग करके रैखिक रूप से प्रक्षेपित करें। (इसके अतिरिक्त कोई 3 एलयूटीएस का उपयोग कर सकता है और द्विघात रूप से प्रक्षेपित कर सकता है)। यह कुछ मल्टीप्लायरों की कीमत पर स्मृति की समान मात्रा के लिए घटी हुई विकृति का परिणाम हो सकता है। | ||

| Line 53: | Line 53: | ||

एएम स्पर स्तर लगभग -6.02 P -1.76 [[dBc|डीबीसी]] के बराबर है।<ref name="intersil">{{cite web | title = NCO एक स्थिर, सटीक सिंथेसाइज़र के रूप में| url = http://www.intersil.com/content/dam/Intersil/documents/tb31/tb318.pdf | id = TB318.1 | publisher = Intersil Corporation | year = 1998 }}</ref> | एएम स्पर स्तर लगभग -6.02 P -1.76 [[dBc|डीबीसी]] के बराबर है।<ref name="intersil">{{cite web | title = NCO एक स्थिर, सटीक सिंथेसाइज़र के रूप में| url = http://www.intersil.com/content/dam/Intersil/documents/tb31/tb318.pdf | id = TB318.1 | publisher = Intersil Corporation | year = 1998 }}</ref> | ||

=== शमन तकनीक === | === शमन तकनीक === | ||

ट्रंकेशन से पहले सफेद शोर की प्रारंभआत से फेज ट्रंकेशन स्पर्स को अधिक | ट्रंकेशन से पहले सफेद शोर की प्रारंभआत से फेज ट्रंकेशन स्पर्स को अधिक हद तक कम किया जा सकता है। ट्रंकेशन ऑपरेशन को रेखीय बनाने के लिए पीए आउटपुट शब्द के निचले डब्ल्यू + 1 बिट्स में तथाकथित गड़बड़ी शोर को सम्मिलित किया गया है। इस प्रकार अधिकांशतः सुधार दंड के बिना प्राप्त किया जा सकता है क्योंकि डीएसी शोर तल प्रणाली के प्रदर्शन पर हावी हो जाता है। एम्प्लिट्यूड ट्रंकेशन स्पर्स को इस तरह से कम नहीं किया जा सकता है। इस प्रकार पीएसी रोम में स्थिर मूल्यों में शोर का परिचय ट्रंकेशन त्रुटि शर्तों की चक्रीयता को खत्म नहीं करेगा और इस प्रकार वांछित प्रभाव प्राप्त नहीं करेगा।<ref name="kroupa"/> | ||

== यह भी देखें == | == यह भी देखें == | ||

* डिजिटल-से-एनालॉग कनवर्टर (डीएसी) | * डिजिटल-से-एनालॉग कनवर्टर (डीएसी) | ||

| Line 64: | Line 64: | ||

{{good article}} | {{good article}} | ||

{{DEFAULTSORT:Numerically controlled oscillator}} | {{DEFAULTSORT:Numerically controlled oscillator}} | ||

[[Category:Created On 19/06/2023|Numerically controlled oscillator]] | |||

[[Category:Good articles|Numerically controlled oscillator]] | |||

[[Category: Machine Translated Page]] | [[Category:Lua-based templates|Numerically controlled oscillator]] | ||

[[Category: | [[Category:Machine Translated Page|Numerically controlled oscillator]] | ||

[[Category:Pages with broken file links|Numerically controlled oscillator]] | |||

[[Category:Pages with script errors|Numerically controlled oscillator]] | |||

[[Category:Templates Vigyan Ready|Numerically controlled oscillator]] | |||

[[Category:Templates that add a tracking category|Numerically controlled oscillator]] | |||

[[Category:Templates that generate short descriptions|Numerically controlled oscillator]] | |||

[[Category:Templates using TemplateData|Numerically controlled oscillator]] | |||

[[Category:अंकीय संकेत प्रक्रिया|Numerically controlled oscillator]] | |||

[[Category:इलेक्ट्रॉनिक ऑसिलेटर्स|Numerically controlled oscillator]] | |||

[[Category:डिजिटल इलेक्ट्रॉनिक्स|Numerically controlled oscillator]] | |||

[[Category:सिंथेसाइज़र|Numerically controlled oscillator]] | |||

Latest revision as of 20:58, 5 July 2023

एक संख्यात्मक रूप से नियंत्रित दोलित्र (एनसीओ) एक डिजिटल संकेतक उत्पादक है जो एक तुल्यकालिक सर्किट (अर्थात, क्लॉक्ड), असतत-समय, एक तरंग के असतत-मूल्यवान प्रतिनिधित्व, सामान्यतः साइनसॉइडल बनाता है।[1] इस प्रकार प्रत्यक्ष डिजिटल सिंथेसाइज़र (डीडीएस) बनाने के लिए एनसीओ अधिकांशतः आउटपुट पर डिज़िटल से एनालॉग कन्वर्टर (डीएसी) के संयोजन के साथ प्रयोग किया जाता है।[3]

संख्यात्मक रूप से नियंत्रित ऑसिलेटर चपलता, त्रुटिहीनता, स्थिरता और विश्वसनीयता की स्थितियों में अन्य प्रकार के ऑसिलेटर की तुलना में कई फायदे प्रदान करते हैं।[2] इस प्रकार एनसीओ का उपयोग कई संचार प्रणालियों में किया जाता है, जिसमें 3जी वायरलेस और सॉफ्टवेयर रेडियो सिस्टम, डिजिटल चरण बंद लूप , रडार सिस्टम, ऑप्टिकल या ध्वनिक ट्रांसमिशन के लिए ड्राइवर और मल्टीलेवल आवृत्ति पारी कुंजीयन / चरण-शिफ्ट कुंजीयन मॉड्यूलेटर/डीमोडुलेटर में उपयोग किए जाने वाले डिजिटल अप/डाउन कन्वर्टर्स सम्मिलित हैं।[2]

ऑपरेशन

एक एनसीओ में सामान्यतः दो भाग होते हैं:

- एक चरण संचायक (पीए), जो अपने आउटपुट पर आयोजित मूल्य को प्रत्येक घड़ी के नमूने पर एक आवृत्ति नियंत्रण मूल्य जोड़ता है।

- एक चरण-से-आयाम कनवर्टर (पीएसी), जो चरण संचायक आउटपुट शब्द (चरण शब्द) का उपयोग सामान्यतः एक तरंगरूप तालिका देखो (एलयूटी) में एक सूचकांक के रूप में करता है जिससे कि एक समान आयाम नमूना प्रदान किया जा सके। कभी-कभी उत्तम त्रुटिहीनता प्रदान करने और चरण त्रुटि शोर को कम करने के लिए लुक-अप तालिका के साथ रैखिक इंटरपोलेशन का उपयोग किया जाता है। इस प्रकार चरण को आयाम में परिवर्तित करने के अन्य तरीके, गणितीय एल्गोरिदम जैसे कि बिजली श्रृंखला का उपयोग किया जा सकता है, विशेष रूप से एक सॉफ्टवेयर एनसीओ में किया जाता हैं।

जब क्लॉक किया जाता है, तो चरण संचायक (पीए) मॉड्यूलो-2एन सॉटूथ वेवफॉर्म तरंग बनाता है जिसे फिर चरण-से-आयाम कनवर्टर (पीएसी) द्वारा एक सैंपल साइनसॉइड में परिवर्तित किया जाता है, जहां एन चरण संचायक में ले जाए गए बिट्स की संख्या है। इस प्रकार एन एनसीओ आवृत्ति रेज़ोल्यूशन सेट करता है और सामान्यतः पीएसी लुक-अप टेबल की मेमोरी स्पेस को परिभाषित करने वाली बिट्स की संख्या से अधिक बड़ा होता है। यदि पीएसी की क्षमता 2एम है, तो पीए आउटपुट शब्द को चित्र 1 में दिखाए अनुसार एम बिट्स में छोटा किया जाना चाहिए। इस प्रकार चूंकि, कटे हुए बिट्स को इंटरपोलेशन के लिए उपयोग किया जा सकता है। चरण आउटपुट शब्द का ट्रंकेशन आवृत्ति त्रुटिहीनता को प्रभावित नहीं करता है किन्तु एक समय-भिन्न आवधिक चरण त्रुटि उत्पन्न करता है जो नकली उत्पादों का प्राथमिक स्रोत है। इस प्रकार एक और नकली उत्पाद निर्माण तंत्र पीएसी आउटपुट (आयाम) शब्द का परिमित शब्द लंबाई प्रभाव है।[4]

इस प्रकार घड़ी की आवृत्ति के सापेक्ष आवृत्ति त्रुटिहीनता केवल चरण की गणना करने के लिए उपयोग किए जाने वाले अंकगणित की त्रुटिहीनता से सीमित होती है।[4]

एनसीओ चरण- और आवृत्ति-चतुर हैं, और उपयुक्त नोड पर योग द्वारा चरण मॉडुलन या आवृति का उतार - चढ़ाव आउटपुट का उत्पादन करने के लिए तुच्छ रूप से संशोधित किया जा सकता है, या चित्र में दिखाए अनुसार चतुर्भुज चरण आउटपुट प्रदान करने के लिए साधारण रूप से संशोधित किया जा सकता है।

चरण संचायक

एक बाइनरी चरण संचायक में एक एन-बिट बाइनरी योजक (इलेक्ट्रॉनिक्स) और एक हार्डवेयर रजिस्टर होता है, जैसा कि चित्र 1 में दिखाया गया है।[5] इस प्रकार प्रत्येक घड़ी चक्र एक नया एन-बिट आउटपुट उत्पन्न करता है जिसमें आवृत्ति कंट्रोल वर्ड (एफसीडब्ल्यू) के साथ रजिस्टर से प्राप्त पिछले आउटपुट सम्मिलित होते हैं जो किसी दिए गए आउटपुट आवृत्ति के लिए स्थिर होते हैं। परिणामी आउटपुट तरंग चरण आकार के साथ एक सीढ़ी है , एफसीडब्ल्यू का पूर्णांक मान हैं।[6] इस प्रकार कुछ कॉन्फ़िगरेशन में, चरण आउटपुट रजिस्टर के आउटपुट से लिया जाता है जो एक घड़ी चक्र विलंबता (इंजीनियरिंग) प्रस्तुत करता है किन्तु योजक को उच्च घड़ी दर पर संचालित करने की अनुमति देता है।[2]

योजक को अतिप्रवाह करने के लिए डिज़ाइन किया गया है जब इसके ऑपरेंड के पूर्ण मूल्य का योग इसकी क्षमता से अधिक हो जाता है (2एन-1). अतिप्रवाह बिट को छोड़ दिया जाता है, इसलिए आउटपुट शब्द की चौड़ाई हमेशा इसकी इनपुट शब्द चौड़ाई के बराबर होती है। शेष , जिसे अवशिष्ट कहा जाता है, रजिस्टर में संग्रहीत किया जाता है और इस समय से चक्र दोहराता है (चित्र 2 देखें)।[5] इस प्रकार चूंकि एक चरण संचायक एक परिमित राज्य मशीन है, अंततः कुछ नमूना के पर अवशिष्ट को प्रारंभिक मूल्य पर वापस आना चाहिए . अंतराल K को दी गई भव्य पुनरावृत्ति दर (GRR) के रूप में संदर्भित किया जाता है।

जहाँ जीसीडी सबसे बड़ा सामान्य विभाजक कार्य है।इस प्रकार जीआरआर किसी दिए गए के लिए सही आवधिकता का प्रतिनिधित्व करता है जो एक उच्च संकल्प एनसीओ के लिए बहुत लंबा हो सकता है।[5] सामान्यतः हम औसत अतिप्रवाह दर द्वारा निर्धारित ऑपरेटिंग आवृत्ति में अधिक रुचि रखते हैं।[6]

- (1)

आवृत्ति संकल्प, आवृत्ति में सबसे छोटे संभव वृद्धिशील परिवर्तन के रूप में परिभाषित किया गया है[6]: (2)

समीकरण (1) से पता चलता है कि चरण संचायक को विभाजित अनुपात के प्रोग्राम योग्य गैर-पूर्णांक आवृत्ति विभाजक के रूप में माना जा सकता है .[4]

चरण-से-आयाम कनवर्टर

चरण-आयाम कनवर्टर पीए से प्राप्त ट्रंकेटेड चरण आउटपुट शब्द से नमूना-डोमेन तरंग बनाता है। पीएसी एक साधारण केवल पढ़ने के लिये मेमोरी हो सकती है जिसमें 2 होते हैंM वांछित आउटपुट तरंग के सन्निहित नमूने जो सामान्यतः एक साइनसॉइड होता है। इस प्रकार चूंकि अधिकांशतः, आवश्यक मेमोरी की मात्रा को कम करने के लिए विभिन्न तरकीबें अपनाई जाती हैं। इसमें विभिन्न त्रिकोणमितीय विस्तार सम्मिलित हैं,[7] त्रिकोणमितीय सन्निकटन[5] और विधियाँ जो साइनसोइड्स द्वारा प्रदर्शित चतुर्भुज समरूपता का लाभ उठाती हैं।[8] वैकल्पिक रूप से, पीएसी में रैंडम एक्सेस मेमोरी सम्मिलित हो सकती है जिसे मनमाना तरंग जनरेटर बनाने के लिए वांछित रूप से भरा जा सकता है।

नकली उत्पाद

नकली उत्सर्जन उत्पाद सिग्नल प्रोसेसिंग श्रृंखला में गैर-रैखिक संख्यात्मक प्रभावों के कारण आउटपुट तरंग के निर्माण में हार्मोनिक विरूपण या गैर-हार्मोनिक विरूपण का परिणाम हैं। यहां केवल संख्यात्मक त्रुटियों को कवर किया गया है। इस प्रकार डिजिटल-टू-एनालॉग कन्वर्टर में बनाए गए अन्य विरूपण तंत्रों के लिए डायरेक्ट डिजिटल सिंथेसाइज़र एवं डायरेक्ट-डिजिटल सिंथेसाइज़र लेख में संबंधित अनुभाग देखें।

फेज ट्रंकेशन स्पर्स

एनसीओ (एन) के चरण संचायक बिट्स की संख्या सामान्यतः 16 और 64 के बीच होती है। यदि पीए आउटपुट शब्द का उपयोग सीधे पीएसी लुक-अप टेबल को अनुक्रमित करने के लिए किया जाता है, तो रोम में एक उच्च भंडारण क्षमता की आवश्यकता होगी। इस प्रकार, पीए आउटपुट शब्द को उचित स्मृति स्थान तक फैलाने के लिए छोटा किया जाना चाहिए। चरण शब्द का ट्रंकेशन आउटपुट साइनसॉइड के चरण मॉडुलन का कारण बनता है जो काटे गए बिट्स की संख्या के अनुपात में गैर-हार्मोनिक विरूपण का परिचय देता है। इस विकृति द्वारा बनाए गए नकली उत्पादों की संख्या निम्न द्वारा दी गई है:

- (3)

जहाँ W काटे गए बिट्स की संख्या है।

इस प्रकार नकली-मुक्त गतिशील रेंज की गणना में, हम नकली उत्पाद में रुचि रखते हैं, जो वाहक आउटपुट स्तर के सापेक्ष सबसे बड़े आयाम के साथ दिया गया है:

जहां पी बिट्स में चरण-से-आयाम कनवर्टर की लुकअप टेबल का आकार है, अर्थात, चित्रा 1 में एम। डब्ल्यू> 4 के लिए,

एक अन्य संबंधित नकली उत्पादन विधि ऊपर उल्लिखित जीआरआर के कारण साधारण मॉडुलन है। इन स्पर्स का आयाम बड़े एन के लिए कम है और उनकी आवृत्ति सामान्यतः पता लगाने योग्य होने के लिए बहुत कम है किन्तु वे कुछ अनुप्रयोगों के लिए समस्याएँ उत्पन्न कर सकते हैं।[5]

एड्रेस लुकअप में ट्रंकेशन को कम करने का एक विधि यह है कि समानांतर में कई छोटी लुकअप टेबल हों और टेबल में इंडेक्स करने के लिए ऊपरी बिट्स का उपयोग किया जाए और निचले बिट्स को रैखिक या द्विघात प्रक्षेप के लिए तौला जाए। इस प्रकार अर्थात दो 16-बिट एलयूटीएस में देखने के लिए 24-बिट चरण संचायक का उपयोग करें। काटे गए 16 एमएसबी में पता, और वह प्लस 1. वजन के रूप में 8 एलएसबी का उपयोग करके रैखिक रूप से प्रक्षेपित करें। (इसके अतिरिक्त कोई 3 एलयूटीएस का उपयोग कर सकता है और द्विघात रूप से प्रक्षेपित कर सकता है)। यह कुछ मल्टीप्लायरों की कीमत पर स्मृति की समान मात्रा के लिए घटी हुई विकृति का परिणाम हो सकता है।

आयाम ट्रंकेशन स्पर्स

नकली उत्पादों का एक अन्य स्रोत पीएसी लुक अप तालिका (ओं) में निहित नमूनाकृत तरंग का आयाम परिमाणीकरण (सिग्नल प्रोसेसिंग) है। यदि डीएसी बिट्स की संख्या पी है, तो

एएम स्पर स्तर लगभग -6.02 P -1.76 डीबीसी के बराबर है।[9]

शमन तकनीक

ट्रंकेशन से पहले सफेद शोर की प्रारंभआत से फेज ट्रंकेशन स्पर्स को अधिक हद तक कम किया जा सकता है। ट्रंकेशन ऑपरेशन को रेखीय बनाने के लिए पीए आउटपुट शब्द के निचले डब्ल्यू + 1 बिट्स में तथाकथित गड़बड़ी शोर को सम्मिलित किया गया है। इस प्रकार अधिकांशतः सुधार दंड के बिना प्राप्त किया जा सकता है क्योंकि डीएसी शोर तल प्रणाली के प्रदर्शन पर हावी हो जाता है। एम्प्लिट्यूड ट्रंकेशन स्पर्स को इस तरह से कम नहीं किया जा सकता है। इस प्रकार पीएसी रोम में स्थिर मूल्यों में शोर का परिचय ट्रंकेशन त्रुटि शर्तों की चक्रीयता को खत्म नहीं करेगा और इस प्रकार वांछित प्रभाव प्राप्त नहीं करेगा।[4]

यह भी देखें

- डिजिटल-से-एनालॉग कनवर्टर (डीएसी)

- डिजिटल रूप से नियंत्रित ऑसिलेटर (डीसीओ)

- प्रत्यक्ष डिजिटल संश्लेषण (डीडीएस)

संदर्भ

- ↑ 1.0 1.1 Radatz, J. (1997). इलेक्ट्रिकल और इलेक्ट्रॉनिक्स शर्तों का IEEE मानक शब्दकोश. New York, NY: IEEE Standards Office.

- ↑ 2.0 2.1 2.2 2.3 "संख्यात्मक रूप से नियंत्रित थरथरानवाला". Lattice Semiconductor Corporation. 2009.

- ↑ While some authors use the terms DDS and NCO interchangeably,[2] by convention an NCO refers to the digital (i.e. the discrete-time, discrete amplitude) portion of a DDS[1]

- ↑ 4.0 4.1 4.2 4.3 Kroupa, V. F. (1999). डायरेक्ट डिजिटल फ़्रीक्वेंसी सिंथेसाइज़र. IEEE Press. ISBN 0-7803-3438-8.

- ↑ 5.0 5.1 5.2 5.3 5.4 Popek, G.; Kampik, M. (October 2009). "टेलर सीरीज सन्निकटन का उपयोग करते हुए लो-स्पर संख्यात्मक रूप से नियंत्रित ऑसिलेटर" (PDF). XI International PhD Workshop OWD 2009. Gliwice, Poland: Silesian University of Technology.

- ↑ 6.0 6.1 6.2 Murphy, Eva; Slattery, Colm (August 2004), "All About Direct Digital Synthesis", Analog Dialogue, Analog Devices, 38

- ↑ US 7437391, Miller, B. M., "संख्यात्मक रूप से नियंत्रित दोलक और संचालन की विधि", issued October 14, 2008

- ↑ US 4486846, McCallister, R. D. & Shearer, D., "चतुर्थांश प्रतिकृति और फ़ंक्शन अपघटन का उपयोग करके संख्यात्मक रूप से नियंत्रित ऑसिलेटर", published 12/04/1984

- ↑ "NCO एक स्थिर, सटीक सिंथेसाइज़र के रूप में" (PDF). Intersil Corporation. 1998. TB318.1.