फिल्ड-प्रोग्रामेबल गेट ऐरे (एफपीजीए): Difference between revisions

No edit summary |

No edit summary |

||

| Line 12: | Line 12: | ||

== इतिहास == | == इतिहास == | ||

एफपीजीए उद्योग, प्रोग्रामेबल रीड-ओनली मेमोरी ( | एफपीजीए उद्योग, प्रोग्रामेबल रीड-ओनली मेमोरी (प्रॉम) और प्रोग्रामेबल लॉजिक डिवाइसेस (पीएलडी) से उत्पन्न हुआ है। प्रॉम और पीएलडी दोनों के पास कारखाने या कार्य क्षेत्र (फील्ड-प्रोग्रामेबल) में बैचों में प्रोग्राम किए जाने का विकल्प था। हालांकि, प्रोग्रामेबल लॉजिक को लॉजिक गेट्स के बीच हार्ड-वायर्ड किया गया था।<ref name="history">{{cite web |url=http://filebox.vt.edu/users/tmagin/history.htm |title=History of FPGAs |access-date=2013-07-11 |url-status=dead |archive-url=https://web.archive.org/web/20070412183416/http://filebox.vt.edu/users/tmagin/history.htm |archive-date=April 12, 2007}}</ref> | ||

अल्टेरा की स्थापना 1983 में की गई और इसने 1984 में उद्योग को प्रथम रि-प्रोग्रामेबल लॉजिक डिवाइस-EP300 वितरित की जिसके पैकेज में क्वार्ट्ज विंडो थी | इसमें उपयोगकर्ताओं को साचे (डाई) पर डिवाइस कॉन्फ़िगरेशन का आयोजन करने वाले इप्रोम सेल्स को मिटाने के लिए अल्ट्रा-वायलेट लैंप को जलाने की सुविधा थी।<ref>{{cite web|url=https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html|title=In the Beginning|date=21 April 2015|work=altera.com}}</ref> | |||

ज़िलिनक्स | ज़िलिनक्स के सह-संस्थापक रॉस फ्रीमैन और बर्नार्ड वोंडर्सचमिट ने 1985 में प्रथम व्यावसायिक रूप से व्यवहार्य फील्ड-प्रोग्रामेबल गेट ऐरे XC2064 का आविष्कार किया।<ref name=":0">{{Cite web|url=http://www.xilinx.com/publications/archives/xcell/Xcell32.pdf|title=XCELL issue 32|publisher=Xilinx}}</ref> XC2064 में गेट्स के बीच प्रोग्रामेबल गेट्स और प्रोग्रामेबल इंटरकनेक्ट्स होते हैं, जो एक नई तकनीक और बाजार[6] की शुरुआत थी। XC2064 में 64 कॉन्फ़िगरेबल लॉजिक ब्लॉक्स (सीएलबी) होते हैं जिसमें दो तीन-इनपुट लुकअप टेबल (एलयुटी) होती हैं। लगभग 20 वर्षों के बाद, फ्रीमैन को उनके आविष्कार [8][9]के लिए राष्ट्रीय आविष्कारक हॉल ऑफ फेम में प्रवेश दिया गया। | ||

1987 में, नेवल सरफेस वारफेयर सेंटर | 1987 में, नेवल सरफेस वारफेयर सेंटर ने स्टीव कैसलमैन द्वारा प्रस्तावित प्रयोग को कंप्यूटर विकसित करने के लिए प्रयोग किया, जो 600,000 रिप्रोग्रामेबल गेट को कार्यान्यवित कर सके । कैसलमैन सफल रहे और सिस्टम से संबंधित पेटेंट 1992 में जारी किया गया।<ref name="history" /> | ||

अल्टेरा और ज़िलिनक्स | अल्टेरा और ज़िलिनक्स 1985 से मध्य-1990 तक अबाध रूप से विकसित होते रहे जब अन्य प्रतियोगियों ने बाजार में प्रवेश किया और उनकी हिस्सेदारी को काफी कम कर दिया। 1993 तक, एक्टेल के पास बाजार की लगभग 18% हिस्सेदारी हो गई।<ref name="four" /> | ||

सर्किट परिष्करण और उत्पादन की मात्रा के लिहाज से 1990 का दशक, एफपीजीए के विकास का स्वर्णिम समय था। 1990 के दशक की शुरुआत में, एफपीजीए का उपयोग मुख्य रूप से दूरसंचार और नेटवर्किंग में किया गया। दशक के अंत तक, एफपीजीए ने उपभोक्ता, मोटर वाहन और औद्योगिक अनुप्रयोगों में अपना स्थान बना लिया।<ref name="book">{{cite book |last = Maxfield |first = Clive| title = The Design Warrior's Guide to FPGAs: Devices, Tools and Flows| url = https://books.google.com/books?id=ZOadcQAACAAJ&pg=PA4| year = 2004| publisher = Elsevier| isbn = 978-0-7506-7604-5| page = 4}}</ref> | सर्किट परिष्करण और उत्पादन की मात्रा के लिहाज से 1990 का दशक, एफपीजीए के विकास का स्वर्णिम समय था। 1990 के दशक की शुरुआत में, एफपीजीए का उपयोग मुख्य रूप से दूरसंचार और नेटवर्किंग में किया गया। दशक के अंत तक, एफपीजीए ने उपभोक्ता, मोटर वाहन और औद्योगिक अनुप्रयोगों में अपना स्थान बना लिया।<ref name="book">{{cite book |last = Maxfield |first = Clive| title = The Design Warrior's Guide to FPGAs: Devices, Tools and Flows| url = https://books.google.com/books?id=ZOadcQAACAAJ&pg=PA4| year = 2004| publisher = Elsevier| isbn = 978-0-7506-7604-5| page = 4}}</ref> | ||

2013 तक | 2013 तक अल्टेरा (31 प्रतिशत), एक्टेल (10 प्रतिशत) और ज़िलिनक्स (36 प्रतिशत) एक साथ एफपीजीए बाजार के लगभग 77 प्रतिशत का प्रतिनिधित्व करते थे।<ref>{{cite web|url=http://sourcetech411.com/2013/04/top-fpga-companies-for-2013/|title=Top FPGA Companies For 2013|work=sourcetech411.com|date=2013-04-28}}</ref> | ||

माइक्रोसॉफ्ट | माइक्रोसॉफ्ट जैसी कंपनियों ने एफपीजीए के प्रति वाट बेहतर प्रदर्शन के कारण, उच्च प्रदर्शन और कम्प्यूटेशनल रूप से गहन प्रणालियों (जैसे डेटा सेंटर जो इसके बिंग खोज इंजन को संचालित करता है) को बढ़ाने के लिए एफपीजीए का उपयोग करना शुरू कर दिया है।<ref>{{cite magazine|url=https://www.wired.com/2014/06/microsoft-fpga/|title=Microsoft Supercharges Bing Search With Programmable Chips|date=16 June 2014|magazine=WIRED}}</ref> माइक्रोसॉफ्ट ने 2014 में बिंग को और तेज करने के लिए एफपीजीए का उपयोग करना शुरू किया और 2018 में अपने अज़ुर क्लाउड कंप्यूटिंग प्लेटफॉर्म और अन्य डेटा सेंटर वर्कलोड के लिए एफपीजीए का उपयोग करना शुरू कर दिया।<ref name="ProjCatapult" /> | ||

प्रस्तुत समयरेखा एफपीजीए डिजाइन के विभिन्न पहलुओं में प्रगति को दर्शाती है : | प्रस्तुत समयरेखा एफपीजीए डिजाइन के विभिन्न पहलुओं में प्रगति को दर्शाती है : | ||

| Line 45: | Line 45: | ||

;डिजाइन की शुरुवात | ;डिजाइन की शुरुवात | ||

डिजाइन स्टार्ट | डिजाइन स्टार्ट, एफपीजीए पर कार्यान्वयन के लिए नया कस्टम डिज़ाइन है। | ||

* 2005: 80,000<ref name="designstarts">Dylan McGrath, ''EE Times'', "[http://www.eetimes.com/conf/dac/showArticle.jhtml?articleID=164302400 Gartner Dataquest Analyst Gives ASIC, FPGA Markets Clean Bill of Health]". June 13, 2005. Retrieved February 5, 2009.</ref> | * 2005: 80,000<ref name="designstarts">Dylan McGrath, ''EE Times'', "[http://www.eetimes.com/conf/dac/showArticle.jhtml?articleID=164302400 Gartner Dataquest Analyst Gives ASIC, FPGA Markets Clean Bill of Health]". June 13, 2005. Retrieved February 5, 2009.</ref> | ||

* 2008: 90,000<ref name="eweekly">{{cite web|url=http://www.xilinx.com/support/documentation/data_sheets/ds112.pdf|title=Virtex-4 Family Overview|website=xilinx.com|access-date=14 April 2018}}</ref> | * 2008: 90,000<ref name="eweekly">{{cite web|url=http://www.xilinx.com/support/documentation/data_sheets/ds112.pdf|title=Virtex-4 Family Overview|website=xilinx.com|access-date=14 April 2018}}</ref> | ||

Revision as of 17:11, 20 September 2022

फील्ड-प्रोग्रामेबल गेट ऐरे (एफपीजीए) एक एकीकृत सर्किट है जो ग्राहक या डिजाइनर द्वारा कॉन्फ़िगर करने के लिए डिज़ाइन किया गया इसलिए इसको फील्ड-प्रोग्रामेबल नाम दिया है। एफपीजीए कॉन्फ़िगरेशन आमतौर पर हार्डवेयर विवरण भाषा (एचडीएल) का उपयोग करके निर्दिष्ट किया जाता है जैसा कि एप्लिकेशन-विशिष्ट एकीकृत सर्किट (एएसआईसी) के लिए उपयोग किया गया है। सर्किट आरेखों का उपयोग पहले कॉन्फ़िगरेशन को निर्दिष्ट करने के लिए किया गया था, लेकिन इलेक्ट्रॉनिक डिजाइन स्वचालन उपकरणों के आगमन के कारण यह तेजी से दुर्लभ होता जा रहा है।

एफपीजीए में प्रोग्रामेबल लॉजिक ब्लॉक की सरणी होती है और पुनर्निर्माण योग्य इंटरकनेक्ट्स का एक पदानुक्रम होता है, जिससे ब्लॉक को एक साथ जोड़ा जाता है। लॉजिक ब्लॉक को जटिल कॉम्बिनेशनल फ़ंक्शंस करने के लिए कॉन्फ़िगर किया जा सकता है, या सरल लॉजिक गेट्स जैसे AND और XOR के रूप में उपयोग में जा सकता है। अधिकांश एफपीजीए में, लॉजिक ब्लॉकों में मेमोरी तत्व भी शामिल हैं, जो साधारण फ्लिप-फ्लॉप हो सकते हैं या अतिरिक्त संपूर्ण मेमोरी ब्लॉक।[1] कई एफपीजीए को विभिन्न तर्क कार्यों को करने के लिए पुन: रिप्रोग्राम किया जा सकता है, जिससे कंप्यूटर सॉफ़्टवेयर जैसी लचीली पुनर्संयोजन कम्प्यूटिंग की सहूलियत मिलती है।

हार्डवेयर के साथ सिस्टम सॉफ्टवेयर विकास साथ-साथ कर सकने की क्षमता के कारण एफपीजीए की एम्बेडेड सिस्टम विकास में उल्लेखनीय भूमिका है, विकास के बहुत ही शुरुआती चरण में सिस्टम प्रदर्शन सिमुलेशन में सहयोग करता है और सिस्टम आर्किटेक्चर को अंतिम रूप देने से पहले विभिन्न सिस्टम परीक्षणों और डिजाइन पुनरावृत्तियों की अनुमति देता है।[2]

इतिहास

एफपीजीए उद्योग, प्रोग्रामेबल रीड-ओनली मेमोरी (प्रॉम) और प्रोग्रामेबल लॉजिक डिवाइसेस (पीएलडी) से उत्पन्न हुआ है। प्रॉम और पीएलडी दोनों के पास कारखाने या कार्य क्षेत्र (फील्ड-प्रोग्रामेबल) में बैचों में प्रोग्राम किए जाने का विकल्प था। हालांकि, प्रोग्रामेबल लॉजिक को लॉजिक गेट्स के बीच हार्ड-वायर्ड किया गया था।[3]

अल्टेरा की स्थापना 1983 में की गई और इसने 1984 में उद्योग को प्रथम रि-प्रोग्रामेबल लॉजिक डिवाइस-EP300 वितरित की जिसके पैकेज में क्वार्ट्ज विंडो थी | इसमें उपयोगकर्ताओं को साचे (डाई) पर डिवाइस कॉन्फ़िगरेशन का आयोजन करने वाले इप्रोम सेल्स को मिटाने के लिए अल्ट्रा-वायलेट लैंप को जलाने की सुविधा थी।[4]

ज़िलिनक्स के सह-संस्थापक रॉस फ्रीमैन और बर्नार्ड वोंडर्सचमिट ने 1985 में प्रथम व्यावसायिक रूप से व्यवहार्य फील्ड-प्रोग्रामेबल गेट ऐरे XC2064 का आविष्कार किया।[5] XC2064 में गेट्स के बीच प्रोग्रामेबल गेट्स और प्रोग्रामेबल इंटरकनेक्ट्स होते हैं, जो एक नई तकनीक और बाजार[6] की शुरुआत थी। XC2064 में 64 कॉन्फ़िगरेबल लॉजिक ब्लॉक्स (सीएलबी) होते हैं जिसमें दो तीन-इनपुट लुकअप टेबल (एलयुटी) होती हैं। लगभग 20 वर्षों के बाद, फ्रीमैन को उनके आविष्कार [8][9]के लिए राष्ट्रीय आविष्कारक हॉल ऑफ फेम में प्रवेश दिया गया।

1987 में, नेवल सरफेस वारफेयर सेंटर ने स्टीव कैसलमैन द्वारा प्रस्तावित प्रयोग को कंप्यूटर विकसित करने के लिए प्रयोग किया, जो 600,000 रिप्रोग्रामेबल गेट को कार्यान्यवित कर सके । कैसलमैन सफल रहे और सिस्टम से संबंधित पेटेंट 1992 में जारी किया गया।[3]

अल्टेरा और ज़िलिनक्स 1985 से मध्य-1990 तक अबाध रूप से विकसित होते रहे जब अन्य प्रतियोगियों ने बाजार में प्रवेश किया और उनकी हिस्सेदारी को काफी कम कर दिया। 1993 तक, एक्टेल के पास बाजार की लगभग 18% हिस्सेदारी हो गई।[6]

सर्किट परिष्करण और उत्पादन की मात्रा के लिहाज से 1990 का दशक, एफपीजीए के विकास का स्वर्णिम समय था। 1990 के दशक की शुरुआत में, एफपीजीए का उपयोग मुख्य रूप से दूरसंचार और नेटवर्किंग में किया गया। दशक के अंत तक, एफपीजीए ने उपभोक्ता, मोटर वाहन और औद्योगिक अनुप्रयोगों में अपना स्थान बना लिया।[7]

2013 तक अल्टेरा (31 प्रतिशत), एक्टेल (10 प्रतिशत) और ज़िलिनक्स (36 प्रतिशत) एक साथ एफपीजीए बाजार के लगभग 77 प्रतिशत का प्रतिनिधित्व करते थे।[8]

माइक्रोसॉफ्ट जैसी कंपनियों ने एफपीजीए के प्रति वाट बेहतर प्रदर्शन के कारण, उच्च प्रदर्शन और कम्प्यूटेशनल रूप से गहन प्रणालियों (जैसे डेटा सेंटर जो इसके बिंग खोज इंजन को संचालित करता है) को बढ़ाने के लिए एफपीजीए का उपयोग करना शुरू कर दिया है।[9] माइक्रोसॉफ्ट ने 2014 में बिंग को और तेज करने के लिए एफपीजीए का उपयोग करना शुरू किया और 2018 में अपने अज़ुर क्लाउड कंप्यूटिंग प्लेटफॉर्म और अन्य डेटा सेंटर वर्कलोड के लिए एफपीजीए का उपयोग करना शुरू कर दिया।[10]

प्रस्तुत समयरेखा एफपीजीए डिजाइन के विभिन्न पहलुओं में प्रगति को दर्शाती है :

- गेट्स

- 1987: 9,000 गेट्स, ज़िलिनक्स[6]*

- 1992: 600,000, नौसेना सतह युद्ध विभाग[3]*

- 2000 के दशक की आरम्भ: लाखों में[7]*

- 2013: 50 मिलियन, ज़िलिनक्स[11]

- बाजार का आकार

- 1985: पहला वाणिज्यिक एफपीजीए : ज़िलिनक्स XC2064[5][6]*

- 1987: $ 14 मिलियन[6]*

- c. 1993:> $ 385 मिलियन[6][failed verification]

- 2005: $ 1.9 बिलियन[12]

- 2010 का अनुमान: $ 2.75 बिलियन[12]*

- 2013: $ 5.4 बिलियन[13]

- 2020 अनुमान: $ 9.8 बिलियन[13]

- डिजाइन की शुरुवात

डिजाइन स्टार्ट, एफपीजीए पर कार्यान्वयन के लिए नया कस्टम डिज़ाइन है।

डिजाइन

समकालीन एफपीजीए के पास जटिल डिजिटल संगणना करने के लिए लॉजिक गेट्स और रैम ब्लॉक के बड़े संसाधन हैं। क्यों कि एफपीजीए डिजाइन बहुत तेज I/O दरें और द्विदिश डेटा बसों का उपयोग करते हैं, यह सेटअप समय और होल्ड समय के दायरे में मान्य डेटा के सही समय को सत्यापित करने के लिए एक चुनौती बन जाता है।

फ्लोर प्लानिंग इन समय सम्बंधित कमियों को पूरा करने के लिए एफपीजीए के भीतर संसाधन आवंटन को सक्षम बनाता है। एफपीजीए (FPGAs) का उपयोग किसी भी तार्किक फ़ंक्शन को लागू करने के लिए किया जा सकता है जो एप्लिकेशन-विशिष्ट एकीकृत सर्किट (ASIC) कर सकता है। शिपिंग के बाद कार्यक्षमता को अद्यतन करने की क्षमता, डिजाइन के एक हिस्से के आंशिक पुन: कॉन्फ़िगरेशन[16] और कम गैर-आवर्ती इंजीनियरिंग लागत, ASIC डिजाइन की तुलना में (आम तौर पर उच्च इकाई लागत के बावजूद) कई अनुप्रयोगों में उपयोगी है।[17]

कुछ एफपीजीए में डिजिटल सुविधाओं के अलावा एनालॉग विशेषताएं भी हैं। सबसे आम एनालॉग विशेषता इसके प्रत्येक आउटपुट पिन पर प्रोग्राम करने योग्य स्लीव रेट (slew rate) है, जिससे इंजीनियर को कम लोड किए गए पिनों पर कम दरों को सेट करने की सहूलियत मिलती है अन्यथा जो अस्वीकार्य रूप से रिंग या युगल बन जायेगा | उच्च गति वाले चैनलों पर भारी लोड किए गए पिनों की उच्च दर निर्धारित करता है जो अन्यथा बहुत धीरे चलेंगे।[18] इसके अलावा सामान्य क्वार्ट्ज-क्रिस्टल ऑसिलेटर (quartz-crystal oscillators), ऑन-चिप प्रतिरोध-कैपेसिटेंस ऑसिलेटर (on-chip resistance-capacitance oscillators), और क्लॉक उत्पत्ति और प्रबंधन के लिए उपयोग किए जाने वाले एम्बेडेड विभवांतर-नियंत्रित दोलन (voltage-controlled oscillators) के साथ चरण-बंद लूप (phase-locked loops) हैं, साथ ही साथ हाई-स्पीड सीरिएलाइज़र-डिसेरिएलाइज़र (SERDES) ट्रांसमिट क्लॉक और रिसीवर क्लॉक रिकवरी भी हैं । इनपुट पिन पर अंतर तुलनित्र जो अंतर सिग्नलिंग चैनलों से जुड़े होने के लिए डिज़ाइन किए गए हैं, काफी प्रचलित हैं। कुछ मिश्रित सिग्नल एफपीजीए में एनालॉग सिग्नल कंडीशनिंग ब्लॉक के साथ एकीकृत परिधीय, अनुरूप से अंकीय परिवर्तक (एनालॉग-टू-डिजिटल कन्वर्टर्स) और अंकीय-अनुरूप रूपांतरण (डिजिटल-टू-एनालॉग कन्वर्टर्स) को एक सिस्टम-ऑन-ए- चिप (SoC) के रूप में संचालित करने की सहूलियत है।[19] इस तरह के डिवाइस, एफपीजीए जो अपने आंतरिक प्रोग्रामेबल इंटरकनेक्ट फैब्रिक पर केवल डिजिटल 1 और 0 ही वहन करता है, और फील्ड-प्रोग्रामेबल एनालॉग ऐरे (FPAA), जो इसके आंतरिक प्रोग्रामेबल इंटरकनेक्ट फैब्रिक पर एनालॉग मान ही करता है, के बीच के अंतर को धुंधला कर देते हैं|

लॉजिक ब्लॉक

सबसे प्रचलित एफपीजीए आर्किटेक्चर में लॉजिक ब्लॉक की एक सरणी (जिसको कॉन्फिगुरबल लॉजिक ब्लॉक, सीएलबी (CLB) या लॉजिक एरे ब्लॉक, ऐलऐबी (LAB) भी कहते हैं जो उनके वेंडर पर निर्भर करता है), I/O पैड और रूटिंग चैनल होती है।[1]आम तौर पर सभी रूटिंग चैनलों में समान चौड़ाई (तारों की संख्या) होती है। बहुत से I/O पैड एक पंक्ति की ऊंचाई या सरणी में एक कॉलम की चौड़ाई में फिट हो सकते हैं।

एप्लिकेशन सर्किट को पर्याप्त संसाधनों के साथ एफपीजीए में मैप किया जाना चाहिए।जबकि CLB/LABS और I/OS की संख्या को आसानी से डिज़ाइन द्वारा निर्धारित किया जाता है, लेकिन समान मात्रा के साथ लॉजिक डिजाइनों के बीच आवश्यक रूटिंग ट्रैक की संख्या काफी भिन्न हो सकती है।(उदाहरण के लिए, क्रॉसबार स्विच(crossbar switch) को समान गेट काउंट के साथ सिस्टोलिक सरणी (systolic array) की तुलना में बहुत अधिक रूटिंग की आवश्यकता होती है। चूंकि अप्रयुक्त रूटिंग ट्रैक किसी भी लाभ को प्रदान किए बिना इसकी लागत (और प्रदर्शन को कम करते हैं) बढ़ाते हैं, एफपीजीए निर्माता केवल पर्याप्त ट्रैक प्रदान करने का प्रयास करते हैं ताकि अधिकांश डिज़ाइन जो लुकअप टेबल (LUTs) और I/OS के संदर्भ में फिट होंगे, को रूट किया जा सके। यह अनुमानों द्वारा निर्धारित किया जाता है जैसे कि किराए के नियम से प्राप्त या मौजूदा डिजाइनों के साथ प्रयोगों द्वारा। आज 2018 में, रूटिंग और इंटरकनेक्शन के लिए नेटवर्क-ऑन-चिप आर्किटेक्चर विकसित किए जा रहे हैं। [citation needed]

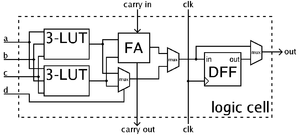

सामान्य तौर पर, लॉजिक ब्लॉक में कुछ लॉजिकल सेल्स (logical cells) होती हैं (जिन्हें एएलएम (ALM), ऐलई (LE), स्लाइस (Slice) आदि कहा जाता है)। किसी विशिष्ट सेल में 4-इनपुट ऐलयुटी (LUT), एक पूर्ण योजक (LA) और एक डी टाइप फ्लिप-फ्लॉप शामिल हैं। इन्हें दो 3-इनपुट ऐलयुटी में विभाजित किया जा सकता है। सामान्य अवस्था में उनको पहले बहुसंकेतक के माध्यम से 4-इनपुट ऐलयुटी (LUT) में जोड़ा जाता है। और अंकगणितीय तौर पर उनके आउटपुट को योजक को दिया जाता है। मोड के चयन को दूसरे MUX में प्रोग्राम किया जाता है। तीसरे MUX की प्रोग्रामिंग के आधार पर आउटपुट या तो सिंक्रोनस (synchronous) या असिंक्रोनस (asynchronous) हो सकता है। व्यावहारिक रूप में, योजक के पूरे या कुछ हिस्सों को जगह बचाने के लिए ऐलयुटी (LUTs) में फ़ंक्शन के रूप में संग्रहीत किया जाता है।[20][21][22]

हार्ड ब्लॉक

उपरोक्त क्षमताओं के आधार पर आधुनिक एफपीजीए वर्ग का विस्तार हुआ है, जिसमें सिलिकॉन में संभव उच्च स्तर की कार्यक्षमता शामिल है। सर्किट में एम्बेडेड इन सामान्य फ़ंक्शन के होने से आवश्यक क्षेत्र कम हो जाता है और सुरुवाती सर्किट्स से उन्हें बनाने की तुलना में अधिक गति प्रदान करता है। इनके उदाहरणों में गुणक (multipliers), जेनेरिक डीएसपी ब्लॉक (DSP blocks), एम्बेडेड प्रोसेसर (embedded processors), हाई स्पीड I/O लॉजिक और एम्बेडेड मेमोरीज (embedded memories) शामिल हैं।

उच्चस्तरीय एफपीजीए (FPGAs) में उच्च गति मल्टी-गीगाबिट ट्रांसरिसीवर ( multi-gigabit transceivers) और हार्ड आईपी कोर (hard IP cores) जैसे प्रोसेसर कोर ( processor cores), ईथरनेट माध्यम के एक्सेस कण्ट्रोल यूनिट ( Ethernet medium access control units), पीसीआई/पीसीआई एक्सप्रेस नियंत्रक (PCI/PCI Express controllers) और बाह्य मेमोरी कंट्रोलर (external memory controllers) हो सकते हैं। ये कोर प्रोग्रामेबल फैब्रिक के साथ मौजूद होते हैं लेकिन वे ऐलयुटी (LUTs) के बजाय ट्रांजिस्टर से बाहर बने होते हैं| इसलिए उनके पास ASIC के स्तर का प्रदर्शन और ऊर्जा खपत होती है जो कि पर्याप्त मात्रा में फैब्रिक के संसाधनों का सेवन किए बिना होता है| जिसको एप्लिकेशन-विशिष्ट कार्य के लिए फैब्रिक के संसाधनों का सेवन किया जा सकता है। मल्टी-गिगाबिट ट्रांससीवर्स (( multi-gigabit transceivers)) में उच्च प्रदर्शन एनालॉग इनपुट और आउटपुट सर्किटरी होते हैं जिसमें उच्च गति वाले सीरियलाइज़र (serializers) और डिसेरियलिज़र (deserializers) घटक होते हैं जिन्हें ऐलयुटी (LUTs) से बाहर नहीं बनाया जा सकता है। उच्च-स्तरीय भौतिक परत (PHY) कार्यक्षमता जैसे कि लाइन कोडिंग, सीरियलाइज़र (serializers) और डिसेरियलिज़र (deserializers) के साथ हार्ड लॉजिक में कार्यान्वित होना या न होना उस एफपीजीए पर निर्भर करता है|

सॉफ्ट कोर

हार्ड-मैक्रो (hard-macro) प्रोसेसर के विकल्प के रूप में, सॉफ्ट प्रोसेसर आईपी कोर (soft processor IP cores) का उपयोग करते हैं जो एफपीजीए लॉजिक के भीतर लागू किया जाता है। निओस-II (NIOS II), माइक्रोब्लेज़ (Microblaze) और लैटिसिमिको32 (Latticemico32) लोकप्रिय सॉफ्टकोर प्रोसेसर (softcore processors) के प्रचलित उदाहरण हैं। कई आधुनिक एफपीजीए को रन टाइम ("run time") पर प्रोग्राम किया जाता है, जिसके कारण पुन: उपयोग करने योग्य कंप्यूटिंग या पुनर्निर्माण योग्य सिस्टम - सीपीयू (CPUs) का विचार है जो प्रस्तुत कार्य के अनुरूप खुद को फिर से कॉन्फ़िगर करता है। इसके अतिरिक्त, नए गैर-एफपीजीए आर्किटेक्चर उभरने लगे हैं। सॉफ्टवेयर-कॉन्फ़िगर करने योग्य माइक्रोप्रोसेसर्स जैसे कि स्ट्रेच (Stretch) S5000 एक ही चिप पर प्रोसेसर कोर की सरणी और एफपीजीए जैसे प्रोग्रामेबल कोर प्रदान करके हाइब्रिड दृष्टिकोण को अपनाते हैं।

एकीकरण

This section needs additional citations for verification. (June 2017) (Learn how and when to remove this template message) |

2012 में कोर्स ग्रेन्ड (coarse-grained) संरचना दृष्टिकोण को प्रोग्राम ब्लॉकों और पारंपरिक एफपीजीए के इंटरकनेक्ट्स के संयोजन से एक कदम और आगे बढ़ाया गया, जो एम्बेडेड माइक्रोप्रोसेसरों और संबंधित बाह्य उपकरणों के साथ एक प्रोग्राम योग्य चिप पर एक पूर्ण प्रणाली बनाने के लिए किया गया। यह काम 1982 में रॉन पर्लॉफ (Ron Perloff) और बरोज़ एडवांस्ड सिस्टम्स ग्रुप (Burroughs Advanced Systems Group) के हनन पोटाश (Hanan Potash) द्वारा बनाई गई संरचना को दर्शाता है, जिसने SB24 नामक एकल चिप पर पुन: संयोजक सीपीयू (CPU) संरचना को जोड़ दिया है।[23] इस तरह की हाइब्रिड प्रौद्योगिकियों के उदाहरण Xilinx ZynQ-7000 में सभी प्रोग्रामेबल सिस्टम-ऑन-चिप (SoC) में पाए जा सकते हैं।[24] जिसमें एक 1.0 GHz ड्यूल-कोर आर्म कॉर्टेक्स (ARM Cortex)-A9 MPCore प्रोसेसर, एफपीजीए के लॉजिक फैब्रिक या अल्टेरा अरिया (Altera Arria) V एफपीजीए के भीतर एम्बेडेड है[25], जिसमें 800 MHz ड्यूल-कोर आर्म कॉर्टेक्स-A9 MPCore शामिल है। एटमेल एफपीएसएलआईसी (Atmel FPSLIC) एक और ऐसा उपकरण है, जो एटमेल (Atmel) के प्रोग्रामेबल लॉजिक संरचना के साथ संयोजन में एवीआर (AVR) प्रोसेसर का उपयोग करता है। माइक्रोसेमी स्मार्ट फ्यूजन (Microsemi Smart Fusion) डिवाइस के फ्लैश मेमोरी-आधारित एफपीजीए फैब्रिक में एक ARM Cortex-M3 हार्ड प्रोसेसर कोर (512 kB तक का फ़्लैश और 64 kB का RAM) और एनालॉग परिधीय जैसे कि मल्टी-चैनल एनालॉग-टू-डिजिटल कन्वर्टर्स और डिजिटल-टू-एनालॉग कन्वर्टर्स शामिल हैं।

क्लॉकिंग

एफपीजीए के अंदर निर्मित अधिकांश सर्किटरी सिंक्रोनस सर्किटरी है जिसमें एक घड़ी सिग्नल की आवश्यकता होती है। एफपीजीए (FPGAs) में घड़ी और रीसेट के लिए समर्पित वैश्विक और क्षेत्रीय रूटिंग नेटवर्क होते हैं ताकि उन्हें न्यूनतम छेड़-छाड़ के साथ वितरित किया जा सके। इसके अलावा, एफपीजीए (FPGAs) में आम तौर पर एनालॉग चरण-बंद लूप (phase-locked loop) और/या देरी-बंद लूप (delay-locked loop) घटकों को नई घड़ी आवृत्तियों को संश्लेषित करने और जिटर ( jitter) को कम करने के लिए भी शामिल किया जाता है। जटिल डिजाइन अलग -अलग आवृत्ति और चरण संबंधों के साथ कई घड़ियों का उपयोग कर सकते हैं, प्रत्येक अलग घड़ी डोमेन बनाते हैं। ये घड़ी संकेत स्थानीय रूप से आसलेटर (oscillator) द्वारा उत्पन्न किए जा सकते हैं या उन्हें उच्च गति सीरियल डेटा स्ट्रीम से पुनर्प्राप्त किया जा सकता है। मेटास्टेबिलिटी ( metastability) से बचने के लिए घड़ी डोमेन क्रॉसिंग सर्किटरी का निर्माण करते समय सावधानी बरतनी चाहिए।एफपीजीए (FPGAs) में आम तौर पर रैम (RAM) के ब्लॉक होते हैं जो दोहरे पोर्ट रैम ( dual port RAMs) के रूप में काम करने में सक्षम होते हैं। ये अलग-अलग घड़ियों के साथ दोहरे पोर्ट रैम, अलग-अलग घड़ी डोमेन को जोड़ने वाले फिफोस (FIFOs) और दोहरे पोर्ट बफ़र्स के निर्माण में सहायता करते हैं।

3डी आर्किटेक्चर

एफपीजीए (FPGAs) के आकार और ऊर्जा की खपत को कम करने के लिए, तबुला (Tabula) और ज़िलिनक्स (Xilinx) जैसे विक्रेताओं ने तीन-आयामी या क्रमबद्ध (stacked) आर्किटेक्चर पेश किया है।[26][27] इसके 28 nm 7-सीरीज़ एफपीजीएएस की शुरूआत के बाद 28 और एनबीएसपी; एनएम 7-सीरीज़ एफपीजीएएस, ज़िलिनक्स ने कहा कि उन एफपीजीएएस उत्पाद लाइनों में उच्चतम घनत्व वाले भागों में से कई का निर्माण, एक पैकेज में ही कई सांचों का उपयोग करके किया जाएगा। इसमें 3 डी निर्माण और स्टैक्ड-डाई असेंबली के लिए विकसित प्रौद्योगिकी का उपयोग किया जाता है ।

ज़िलिनक्स (Xilinx) के दृष्टिकोण के अनुसार कई (तीन या चार) सक्रिय एफपीजीएएस सांचे , सिलिकॉन इंटरपोसर (interposer) पास पास स्टैक किये जाते हैं | इंटरपोसर सिलिकॉन का एकल टुकड़ा है जिसमें निष्क्रिय इंटरकनेक्ट होते हैं।[27][28] मल्टी-डाई निर्माण, एफपीजीएएस के विभिन्न भागों को विभिन्न प्रक्रिया-प्रौद्योगिकियों के साथ बनाने की सहूलियत देता है, क्योंकि प्रक्रिया की आवश्यकताएं, एफपीजीएएस फैब्रिक और बहुत उच्च गति 28 Gbit/s सीरियल ट्रांसीवर्स के बीच भिन्न होती हैं। इस तरह से निर्मित एफपीजीएएस को विषम (heterogeneous) एफपीजीएएस कहा जाता है।[29]

अलटेरा (Altera) के विषम दृष्टिकोण में एकल मोनोलिथिक एफपीजीएएस साँचा शामिल है और इंटेल के एम्बेडेड मल्टी-डाई इंटरकनेक्ट ब्रिज (EMIB) तकनीक का उपयोग करके एफपीजीएएस से अन्य डाई/प्रौद्योगिकियों को जोड़ना शामिल है।[30]

प्रोग्रामिंग

एफपीजीएएस के व्यवहार को परिभाषित करने के लिए, उपयोगकर्ता हार्डवेयर विवरण भाषा (HDL) या योजनाबद्ध डिजाइन के रूप में डिज़ाइन प्रदान करता है। एचडीएल (HDL) फॉर्म बड़ी संरचनाओं के साथ काम करने के लिए अधिक अनुकूल है क्योंकि हर टुकड़े को हाथ से आकर्षित से चित्रित करने के बजाय उच्च-स्तरीय कार्यात्मक व्यवहार को निर्दिष्ट करना संभव है। हालांकि, योजनाबद्ध प्रविष्टि, डिजाइन और इसके घटक मॉड्यूल के आसान दृश्य के लिए अनुमति दे सकती है।

इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन टूल का उपयोग करके, प्रौद्योगिकी-मैप्ड नेटलिस्ट (netlist) तैयार किया जाता है । नेटलिस्ट (netlist) को प्लेस-एंड-रूट (place-and-rout) नामक सॉफ्टवेयर का उपयोग करके वास्तविक एफपीजीएएस आर्किटेक्चर के लिए फिट किया जा सकता है, जिसे आमतौर पर एफपीजीएएस कंपनी के मालिकाना स्थान-और-रूट सॉफ्टवेयर द्वारा किया जाता है। उपयोगकर्ता समय विश्लेषण, सिमुलेशन और अन्य सत्यापन और मान्यकरण तरीकों के माध्यम से मानचित्र, स्थान और मार्ग परिणामों का पुष्टिकरण करता है। डिजाइन और सत्यापन प्रक्रिया पूरी हो जाने के बाद, बाइनरी फ़ाइल बनती है और आमतौर पर एफपीजीएएस विक्रेता के मालिकाना सॉफ्टवेयर का उपयोग करते हुए, एफपीजीएएस को कॉन्फ़िगर करने के लिए (पुनः) उपयोग किया जाता है। यह फ़ाइल FPGA/CPLD को एक सीरियल इंटरफ़ेस (JTAG) के माध्यम से या EEPROM की तरह बाहरी मेमोरी डिवाइस में स्थानांतरित कर दी जाती है।

सबसे आम एचडीएल (HDLs), वीएचडीएल (VHDL) के साथ -साथ सिस्टम वरिलोग (Verilog) जैसे एक्सटेंशन हैं। हालांकि, एचडीएल (HDLs), जिनकी तुलना असेंबली भाषाओं के बराबर की गई है, में डिजाइनिंग की जटिलता को कम करने के लिए ,[by whom?] वैकल्पिक भाषाओं की शुरूआत के माध्यम से अमूर्त स्तर बढ़ाने के लिए प्रयास हो रहा है। नेशनल इंस्ट्रूमेंट्स की लैबव्यू (National Instruments' LabVIEW) ग्राफिकल प्रोग्रामिंग लैंग्वेज (कभी-कभी G के रूप में संदर्भित) में FPGA ऐड-इन मॉड्यूल है जो FPGA हार्डवेयर को लक्ष्य और प्रोग्राम कर सकता है। वरिलोग (Verilog) को एचडीएल को अधिक मजबूत और लचीला बनाने की प्रक्रिया को सरल बनाने के लिए बनाया गया था। वरिलोग (Verilog) वर्तमान में अत्यधिक लोकप्रिय है। वरिलोग (Verilog) इसके कार्यान्वयन के विवरण को छिपाने के लिए अमूर्तता का एक स्तर बनाता है। वीएचडीएल (VHDL) के विपरीत, वरिलोग (Verilog) में C-जैसा सिंटैक्स होता है।[31]

एफपीजीएएस (FPGAs) में जटिल प्रणालियों के डिजाइन को सरल बनाने के लिए, पूर्वनिर्धारित जटिल कार्यों और सर्किटों के पुस्तकालय मौजूद हैं जिन्हें डिजाइन प्रक्रिया को गति देने के लिए परीक्षण और अनुकूलित किया गया है। इन पूर्वनिर्धारित सर्किटों को आमतौर पर बौद्धिक संपदा (आईपी) कोर कहा जाता है, और एफपीजीए विक्रेताओं और अन्य-पक्ष आईपी आपूर्तिकर्ताओं से उपलब्ध हैं। वे शायद ही कभी स्वतंत्र होते हैं और आमतौर पर मालिकाना लाइसेंस के तहत जारी किए जाते हैं। डेवलपर समुदायों जैसे कि OpenCores ( जो आमतौर पर मुफ्त और ओपन-सोर्स सॉफ़्टवेयर के तहत जारी किया गया है जैसे कि जीपीएल (GPL), बीएसडी (BSD) या इसी तरह के अन्य लाइसेंस) से अन्य पूर्वनिर्धारित सर्किट उपलब्ध हैं। इस तरह के डिजाइनों को ओपन-सोर्स हार्डवेयर (open-source hardware) के रूप में जाना जाता है।

एक विशिष्ट डिजाइन प्रवाह में, FPGA एप्लिकेशन डेवलपर डिजाइन प्रक्रिया के दौरान कई चरणों में डिजाइन का अनुकरण करेगा। प्रारंभ में रजिस्टर-ट्रांसफर स्तर (VHDL) या वरिलोग (Verilog) में आरटीएल (RTL) विवरण सिस्टम को अनुकरण करने और परिणामों का निरीक्षण करने के लिए परीक्षण बेंच बनाकर अनुकरण करते हैं फिर, संश्लेषण इंजन डिज़ाइन को नेटलिस्ट के लिए मैप करते हैं, नेटलिस्ट को गेट-लेवल विवरण में अनुवादित किया जाता है, जहां त्रुटियों के बिना किये गए संश्लेषण की पुष्टि करने के लिए अनुकरण को दोहराया जाता है। अंत में डिजाइन को FPGA में बिंदु पर रखा गया है, जहाँ प्रसार-विलम्ब जोड़ा जा सकता है और अनुकरण फिर से इन मानों के साथ नेटलिस्ट पर वापस ला कर दुहराया जाता है ।

हाल ही में, प्रोग्रामर द्वारा ओपनसीएल (OpenCL-Open Computing Language) का उपयोग किया जा रहा है ताकि FPGA द्वारा प्रदान करने वाली प्रदर्शन और शक्ति क्षमता का लाभ उठाया जा सके। ओपनसीएल (OpenCL) प्रोग्रामर को C प्रोग्रामिंग भाषा में कोड विकसित करने और OpenCL निर्माणों का उपयोग करके OpenCL कर्नेल (kernels) के रूप में FPGA फ़ंक्शन को लक्षित करने की अनुमति देता है।[32] अधिक जानकारी के लिए, उच्च-स्तरीय संश्लेषण (high-level synthesis) और C टू HDL देखें।

अधिकांश FPGAs प्रोग्राम करने के लिए, SRAM-आधारित दृष्टिकोण पर भरोसा करते हैं। ये FPGA इन-सिस्टम प्रोग्रामेबल और री-प्रोग्रामेबल हैं, लेकिन इनको बाहरी बूट डिवाइस की आवश्यकता होती है। उदाहरण के लिए, फ्लैश मेमोरी या EEPROM डिवाइस जो अक्सर आंतरिक SRAM, जो रूटिंग और लॉजिक को नियंत्रित करता है, में सूचना को लोड कर सकते हैं। एसरैम (SRAM) दृष्टिकोण सीमोस (CMOS) पर आधारित है।

एसरैम (SRAM) दृष्टिकोण के दुर्लभ विकल्प हैं:

- फ्यूज: (Fuse) वन-टाइम प्रोग्रामेबल, द्विध्रुवी, अप्रचलित।

- एंटीफ्यूज़: (Antifuse) वन-टाइम प्रोग्रामेबल, सीमोस (CMOS), उदाहरण: एक्टेल SX (Actel SX) और एक्ससेलरेटर (Axcelerator) परिवार; क्विकलॉजिक एक्लिप्स II (QuickLogic Eclipse II) परिवार।[33]

- प्रोम (PROM): प्रोम प्रोग्रामेबल रीड-ओनली मेमोरी टेक्नोलॉजी, प्लास्टिक पैकेजिंग के कारण एक बार प्रोग्रामेबल, अप्रचलित।

- इप्रोम (EPROM): इरेज़ेबल प्रोग्रामेबल रीड-ओनली मेमोरी टेक्नोलॉजी, एक बार प्रोग्राम करने योग्य लेकिन खिड़की के साथ, पराबैंगनी (UV) प्रकाश के साथ मिटाया जा सकता है, सीमोस (CMOS), अप्रचलित।

- इइप्रोम (EEPROM): विद्युत रूप से इरेज़ेबल प्रोग्रामेबल रीड-ओनली मेमोरी टेक्नोलॉजी, प्लास्टिक पैकेजों में भी मिटाया जा सकता है, कुछ लेकिन सभी EEPROM उपकरणों को इन-सिस्टम प्रोग्राम नहीं किया जा सकता है, सीमोस (CMOS)।

- फ्लैश (Flash): फ्लैश-एरेस EPROM तकनीक, प्लास्टिक पैकेजों में भी मिटाया जा सकता है, कुछ लेकिन सभी फ्लैश डिवाइस इन-सिस्टम प्रोग्राम नहीं किए जा सकते हैं| आमतौर पर, फ्लैश सेल समान EEPROM सेल से छोटा होता है और इसलिए निर्माण के लिए कम खर्चीला होता है, सीमोस (CMOS), उदाहरण: एक्टेल प्रोसेक परिवार (Actel ProASIC family)।[33]

प्रमुख निर्माता

2016 में, लंबे समय तक उद्योग प्रतिद्वंद्वियों Xilinx (अब AMD का हिस्सा) और Altera (अब Intel सहायक) FPGA बाजार के अग्रणी थे।[34] उस समय, उन्होंने लगभग 90 प्रतिशत बाजार को नियंत्रित किया।

Xilinx (अब AMD) और Altera (अब Intel) दोनों विंडोज (Windows) और लिनक्स (Linux) (ISE/VIVADO और Quartus) के लिए मालिकाना इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन सॉफ्टवेयर प्रदान करते हैं जो इंजीनियरों को उनके डिजाइनों को डिजाइन, विश्लेषण, अनुकरण और संश्लेषित करने में सक्षम बनाता है।[35][36]

अन्य निर्माताओं में शामिल हैं:

- माइक्रोचिप (Microchip):

- माइक्रोसेमी (Microsemi, पहले एक्टेल:Actel), एंटीफ्यूज़, फ्लैश-आधारित, मिश्रित-सिग्नल FPGAs का उत्पादन करता है ;2018 में माइक्रोचिप द्वारा अधिग्रहित

- एटमेल (Atmel), कुछ Altera- संगत उपकरणों का दूसरा स्रोत; इसके अलावा FPSLIC[clarification needed] उपर्युक्त;[37] 2016 में माइक्रोचिप द्वारा अधिग्रहित

- लैटिस सेमीकंडक्टर (Lattice Semiconductor), जो कम-शक्ति SRAM- आधारित FPGAs का निर्माण करता है। जिसमें एकीकृत कॉन्फ़िगरेशन फ्लैश, इंस्टेंट-ऑन और लाइव पुनर्संरचना की विशेषता है|

- सिलिकॉनब्लू टेक्नोलॉजीज (SiliconBlue Technologies), जो वैकल्पिक एकीकृत गैर-वाष्पशील (nonvolatile) मेमोरी के साथ बेहद कम-शक्ति SRAM- आधारित FPGAs प्रदान करता है; 2011 में Lattice द्वारा अधिग्रहित |

- क्विकलॉजिक (QuickLogic),[38] जो बेहद कम पावर सेंसर हब, बेहद कम संचालित, कम घनत्व SRAM- आधारित FPGAs का निर्माण करता है, डिस्प्ले ब्रिड्जस MIPI & RGB इनपुट्स, MIPI, RGB और LVDS आउटपुट्स के साथ

- (एक्रोनिक्स ) Achronix, 1.5 GHz फैब्रिक स्पीड के साथ SRAM आधारित FPGAs का निर्माण[39]

मार्च 2010 में, तबुला (Tabula) ने अपनी FPGA तकनीक की घोषणा की, जो समय-डिवीजन मल्टीप्लेक्सिंग (time-multiplexed) लॉजिक का और इंटरकनेक्ट उपयोग करता है जो उच्च घनत्व वाले अनुप्रयोगों के लिए संभावित लागत में बचत का दावा करता है।[40] 24 मार्च, 2015 को, तबुला आधिकारिक तौर पर बंद हो गया।[41]

1 जून, 2015 को, इंटेल ने घोषणा की कि वह लगभग 16.7 बिलियन डॉलर में अल्टेरा (Altera) का अधिग्रहण करेगा और 30 दिसंबर, 2015 को अधिग्रहण पूरा कर लिया।[42]

27 अक्टूबर, 2020 को, एएमडी (AMD) ने घोषणा की कि यह ज़िलिनक्स (Xilinx) का अधिग्रहण करेगा।[43]

अनुप्रयोग

एफपीजीएएस का उपयोग किसी भी समस्या को हल करने के लिए किया जा सकता है जो कम्प्यूटेशनल है। यह इस मामूली से तथ्य से साबित होता है कि एफपीजीएएस का उपयोग सॉफ्ट माइक्रोप्रोसेसर को लागू करने के लिए किया जा सकता है, जैसे कि सिलिंक्स मिक्रोब्लाज़े (Xilinx Microblaze) या अल्टेरा निओस II (Altera Nios II)। इसकी उपयोगिता इस बात में निहित है कि वे कुछ अनुप्रयोगों के लिए काफी तेज हैं ऐसा कुछ प्रक्रियाओं के लिए उपयोग किए जाने वाले फाटकों की संख्या के संदर्भ में उनकी समानांतर प्रकृति और परिपक्वता का होना है।[44]

एफपीजीएएस (FPGAs) मूल रूप से मुद्रित सर्किट बोर्डों के लिए ग्लू लॉजिक (glue logic) को लागू करने के लिए सीपीएलडी (CPLDs) के प्रतियोगियों के रूप में शुरू हुआ। जैसे -जैसे उनके आकार, क्षमताओं और गति में वृद्धि हुई, FPGAs इन अतिरिक्त फंक्शन्स को उस स्तर तक के गया, जहां कुछ को अब पूर्ण सिस्टम्स ऑन चिप्स (SOCs) के रूप में विपणन किया जाता है। विशेष रूप से 1990 के दशक के उत्तरार्ध में FPGA आर्किटेक्चर में समर्पित गुणकों (dedicated multipliers) की शुरूआत के साथ, जिन अनुप्रयोग के लिए पारंपरिक रूप से डिजिटल सिग्नल प्रोसेसर हार्डवेयर (DSPS) एकमात्र रिजर्व था, इसके बजाय FPGAs को शामिल करना शुरू कर दिया।[45][46]

एफपीजीएएस (FPGAs) के विकास ने इन उपकरणों के उपयोग में वृद्धि को प्रेरित किया, जिनकी संरचना जटिल कार्यों के लिए अनुकूलित हार्डवेयर समाधानों के विकास की अनुमति देती है, जैसे कि 3डी एमआरआई छवि विभाजन (3D MRI image segmentation) , 3 डी असतत वेवलेट ट्रांसफ़ॉर्म (3D discrete wavelet transform), टोमोग्राफिक छवि पुनर्निर्माण (tomographic image reconstruction) या पीईटी/एमआरआई सिस्टम (PET/MRI systems)।[47][48] विकसित समाधान समानांतर प्रसंस्करण के साथ गहन गणना कार्यों का प्रदर्शन कर सकते हैं, गतिशील रूप से पुन: प्रोग्राम करने योग्य हैं (dynamically reprogrammable), और चिकित्सा इमेजिंग से जुड़ी सभी कठिन वास्तविक समय (real time) की आवश्यकताओं को पूरा करते भी लागत कम होती है।

FPGAs के उपयोग में एक और प्रचलन हार्डवेयर अक्सेलरेशन (hardware acceleration) है, जहां FPGA का उपयोग एल्गोरिथ्म के कुछ भागों को तेज करने और FPGA और जेनेरिक प्रोसेसर के बीच गणना के हिस्से को साझा करने के लिए कर सकता है। ऐसा लगता है, खोज इंजन बिंग (Bing) ने 2014 में अपने खोज एल्गोरिथ्म के लिए FPGA अक्सेलरेशन को अपनाया है।[49] 2018 तक, माइक्रोसॉफ्ट के "प्रोजेक्ट कैटापुल्ट" (Project Catapult) सहित AI एक्सेलेरेटर (AI accelerators) और मशीन लर्निंग (machine learning) के अनुप्रयोगों में कृत्रिम तंत्रिका नेटवर्क (artificial neural networks) को तेज करने के लिए FPGAs के उपयोग में वृद्धि देख रहे हैं[10] ।

परंपरागत रूप से,[when?] FPGAs को विशिष्ट ऊर्ध्वाधर अनुप्रयोगों के लिए आरक्षित किया गया है जहां उत्पादन मात्रा छोटी है। इन कम-मात्रा वाले अनुप्रयोगों के लिए, प्रोग्राम योग्य चिप के लिए प्रति यूनिट हार्डवेयर लागत में कंपनियां जो प्रीमियम भुगतान करती हैं, वह ASIC बनाने पर खर्च किए गए विकास संसाधनों की तुलना में अधिक सस्ती है। 2017 तक, नई लागत और प्रदर्शन की गतिशीलता ने व्यवहार्य अनुप्रयोगों की सीमा को व्यापक बनाया है।

कंपनी गीगाबाइट टेक्नोलॉजी ( Gigabyte Technology) ने एक i-RAM कार्ड बनाया, जिसमें Xilinx FPGA का उपयोग किया गया, हालांकि बड़ी मात्रा में बनाए जाने पर यह कस्टम मेड चिप सस्ता होगा। यह FPGA जल्दी से बाजार में लाने के लिए चुना गया था और 1000 इकाइयों की प्रारंभिक खपत इस FPGA को सबसे अच्छा विकल्प बना रहा था। यह डिवाइस लोगों को हार्ड ड्राइव के रूप में कंप्यूटर रैम का उपयोग करने की अनुमति देता है।[50]

FPGAs के लिए अन्य उपयोगों में शामिल हैं:

- अंतरिक्ष ( radiation hardening[51] के साथ )

- हार्डवेयर सुरक्षा मॉड्यूल[52](Hardware security modules)

सुरक्षा

हार्डवेयर सुरक्षा के विषय में एफपीजीए (FPGAs) के पास एएसआईसी (ASICs) या सुरक्षित माइक्रोप्रोसेसरों की तुलना में फायदे और नुकसान दोनों हैं। FPGAs का लचीलापन, निर्माण के दौरान दुर्भावनापूर्ण संशोधनों के जोखिम को कम कर देता है।[53] पहले कई FPGAs के लिए, डिज़ाइन बिटस्ट्रीम (bitstream) को उजागर किया गया था, जबकि FPGA इसे बाहरी मेमोरी (आमतौर पर हर पावर-ऑन पर) से लोड करता है। सभी प्रमुख FPGA विक्रेता अब डिजाइनरों को बिटस्ट्रीम एन्क्रिप्शन (bitstream encryption) और प्रमाणीकरण जैसे सुरक्षा समाधानों की व्यवस्था प्रदान करते हैं। उदाहरण के लिए, Altera और Xilinx एक बाहरी फ्लैश मेमोरी में संग्रहीत बिटस्ट्रीम के लिए AES एन्क्रिप्शन (256-बिट तक) की पेशकश करते हैं।

FPGAs जो अपने कॉन्फ़िगरेशन को आंतरिक रूप से गैर-फ्लैश मेमोरी में संग्रहीत करते हैं, जैसे कि माइक्रोसेमी के प्रोएसिक 3 (ProAsic 3) या लैटिस के XP2 प्रोग्रामेबल डिवाइस जो बिटस्ट्रीम को उजागर नहीं करते हैं और जिन्हे एन्क्रिप्शन की आवश्यकता नहीं होती है। इसके अलावा, लुकअप टेबल के लिए फ्लैश मेमोरी स्पेस एप्लिकेशन के लिए सिंगल इवेंट अपसेट (single event upset) सुरक्षा प्रदान करती है।[clarification needed] छेड़छाड़ प्रतिरोध की उच्च गारंटी चाहने वाले ग्राहक, माइक्रोसेमी जैसे विक्रेताओं के एक बार-लेखन (write-once) एंटीफ्यूज़ एफपीजीए (antifuse FPGA) का उपयोग कर सकते हैं।

अपने स्ट्रैटिक्स 10 (Stratix 10) एफपीजीएएस (FPGAs) और एसओसीएस (SOCs) के साथ, अल्टेरा (Altera) ने शारीरिक हमलों के खिलाफ उच्च स्तर की सुरक्षा प्रदान करने के लिए सुरक्षित डिवाइस मैनेजर और फिजिकल अस्वाभाविक फंक्शन्स (physical unclonable functions) को पेश किया।[54]

2012 में शोधकर्ताओं सर्गेई स्कोरोबोगाटोव (Sergei Skorobogatov) और क्रिस्टोफर वुड्स (Christopher Woods) ने प्रदर्शित किया कि कुछ एफपीजीए शत्रुतापूर्ण इरादे की दृष्टि असुरक्षित से हो सकते हैं। उन्होंने पाया कि नाजुक पिछले दरवाजे की भेद्यता सिलिकॉन में एक्टेल/माइक्रोसेमी प्रोएसिक 3 के हिस्से के रूप में निर्मित की गई थी, जो इसे कई स्तरों पर असुरक्षित बनाती है जैसे कि क्रिप्टो और एक्सेस कीज़ को रिप्रोग्रामिंग, अनएन्क्रिप्टेड बिटस्ट्रीम तक पहुंचना निम्न-स्तरीय सिलिकॉन सुविधाओं को संशोधित करना और कॉन्फ़िगरेशन डेटा निकालना|[55]

समरूप प्रौद्योगिकियां

ऐतिहासिक रूप से FPGAs धीमे, कम ऊर्जा कुशल रहे हैं और आम तौर पर उनके समकक्ष निश्चित अनुप्रयोग-विशिष्ट एकीकृत सर्किट (ASIC) की तुलना में कम कार्यक्षमता हासिल की है। 2006 के एक अध्ययन से पता चला है कि एफपीजीए पर लागू किए गए डिजाइनों को औसतन 40 गुना अधिक क्षेत्र की आवश्यकता होती है और 12 गुना अधिक गतिशील ऊर्जा की आवश्यकता होती है| यह एएसआईसी (ASIC) कार्यान्वयन की गति से एक तिहाई पर चलता है।[56] हाल ही में, FPGAs जैसे कि Xilinx Virtex-7 या Altera Stratix 5[57] महत्वपूर्ण रूप से कम ऊर्जा उपयोग, अधिक गति, कम सामग्री लागत, न्यूनतम कार्यान्वयन रियल-एस्टेट, और 'ऑन-द-फ्लाई' (on-the-fly) के लिए पुन: संयोजन के लिए संभावनाओं की वृद्धि करके संबंधित ASIC और ASSP ("एप्लिकेशन-विशिष्ट मानक भाग", जैसे कि एक स्टैंडअलोन USB इंटरफ़ेस चिप) को समाधान प्रस्तुत किया। एक डिज़ाइन जिसमें 6 से 10 ASICs शामिल थे, अब केवल एक FPGA का उपयोग करके प्राप्त किया जा सकता है।[56]FPGAs के लाभों में कमियों (bugs) को ठीक करने के लिए, पहले से ही ( in-field) तैनात होने पर फिर से प्रोग्राम करने की क्षमता और बाजार के लिए त्वरित पहुँच, गैर-आवर्ती इंजीनियरिंग लागतों को कम करना शामिल है। विक्रेता FPGA प्रोटोटाइपिंग के माध्यम से मध्य-मार्ग भी ले सकते हैं: FPGAs पर अपने प्रोटोटाइप हार्डवेयर को विकसित कर सकते हैं, लेकिन अपने अंतिम संस्करण को ASIC के रूप में निर्मित करें ताकि डिजाइन के प्रतिबद्ध होने के बाद इसे अब संशोधित नहीं किया जा सके। यह अक्सर नए प्रोसेसर डिजाइन के साथ भी होता है।[58] कुछ FPGAs में आंशिक पुन: कॉन्फ़िगरेशन की क्षमता होती है जो डिवाइस के एक हिस्से को फिर से प्रोग्राम किया जाता है, जबकि अन्य भाग काम करते रहते हैं।[59][60]

जटिल प्रोग्रामेबल लॉजिक डिवाइस (CPLDs) और FPGAs के बीच मुख्य अंतर उनकीसंरचना में हैं। CPLD में तुलनात्मक रूप से प्रतिबंधात्मक संरचना होती है जिसमें एक या एक से अधिक प्रोग्रामेबल सम-ऑफ-प्रोडक्ट्स ( sum-of-products) लॉजिक एरेज़ होते हैं, जो अपेक्षाकृत कम संख्या में क्लॉक्ड रजिस्टरों (registers) को फीड करते हैं। नतीजतन, CPLDs कम लचीले होते हैं, लेकिन अधिक पूर्वानुमानित देरी (timing delays) का लाभ होता है और a higher logic-to-interconnect ratio.[citation needed] मिलता हैं| दूसरी ओर, FPGA आर्किटेक्चर, इंटरकनेक्ट द्वारा प्रभावित होते हैं। यह उन्हें कहीं अधिक लचीला बनाता है (उन डिजाइनों की सीमा के संदर्भ में जो उन पर कार्यान्वयन के लिए व्यावहारिक हैं), लेकिन डिजाइन करने के लिए अधिक जटिल इलेक्ट्रॉनिक डिजाइन स्वचालन (EDA) सॉफ़्टवेयर की जटिल आवश्यकता है। व्यवहार में, FPGAs और CPLDS के बीच का अंतर अक्सर आकार में होता है क्योंकि FPGAs आमतौर पर CPLDs की तुलना में संसाधनों के मामले में बहुत बड़ा होता है। आमतौर पर केवल FPGAs में अधिक जटिल एम्बेडेड फ़ंक्शन जैसे कि एडेर (Adders) ,मल्टीवेर (Multiver) , मेमोरी (Memory) और सेरिअलिज़ेर /डेसेरिअलिज़ेर्स (Serializer/deserializers) होते हैं। एक और सामान्य अंतर यह है कि CPLDs में अपने कॉन्फ़िगरेशन को स्टोर करने के लिए एम्बेडेड फ्लैश मेमोरी होती है जबकि FPGAs को आमतौर पर बाहरी गैर-वाष्पशील मेमोरी (लेकिन हमेशा नहीं) की आवश्यकता होती है। जब डिज़ाइन को सरल इंस्टेंट-ऑन (लॉजिक पहले से ही पावर-अप पर कॉन्फ़िगर किया गया है) CPLDs की आवश्यकता होती है, को आमतौर पर पसंद किया जाता है। अधिकांश अन्य अनुप्रयोगों के लिए FPGAs आमतौर पर पसंद किए जाते हैं। कभी -कभी CPLDS और FPGAs दोनों का उपयोग एक ही सिस्टम डिज़ाइन में किया जाता है। उन डिजाइनों में, CPLDs आम तौर पर ग्लू लॉजिक (glue logic) फंक्शन करते हैं, और FPGA को बूट करने के साथ -साथ पूर्ण सर्किट बोर्ड के रीसेट और बूट अनुक्रम को नियंत्रित करने के लिए जिम्मेदार होते हैं। इसलिए, एप्लिकेशन की जरुरत के आधार पर एक ही डिज़ाइन में एफपीजीए और सीपीएलडी (CPLDs) दोनों का उपयोग करना विवेकपूर्ण हो सकता है।[61]

यह भी देखें

- एफपीजीए मेजेनाइन कार्ड (FPGA Mezzanine)

- एफपीजीए प्रोटोटाइप (FPGA prototyping)

- एचडीएल सिमुलेटर (HDL simulators) की सूची

- सिलिंक्स एफपीजीए (Xilinx FPGAs) की सूची

- वेरिलॉग (Verilog)

- सिस्टमवेरिलॉग (SystemVerilog)

- वीएचडीएल (VHDL)

- हार्डवेयर एक्सिलरेशन (Hardware acceleration)

संदर्भ

- ↑ 1.0 1.1 "FPGA Architecture for the Challenge". toronto.edu. University of Toronto.

- ↑ Simpson, P. A. (2015). FPGA Design, Best Practices for Team Based Reuse, 2nd edition. Switzerland: Springer International Publishing AG. p. 16. ISBN 978-3-319-17924-7.

- ↑ 3.0 3.1 3.2 "History of FPGAs". Archived from the original on April 12, 2007. Retrieved 2013-07-11.

- ↑ "In the Beginning". altera.com. 21 April 2015.

- ↑ 5.0 5.1 "XCELL issue 32" (PDF). Xilinx.

- ↑ 6.0 6.1 6.2 6.3 6.4 Cite error: Invalid

<ref>tag; no text was provided for refs namedfour - ↑ 7.0 7.1 Maxfield, Clive (2004). The Design Warrior's Guide to FPGAs: Devices, Tools and Flows. Elsevier. p. 4. ISBN 978-0-7506-7604-5.

- ↑ "Top FPGA Companies For 2013". sourcetech411.com. 2013-04-28.

- ↑ "Microsoft Supercharges Bing Search With Programmable Chips". WIRED. 16 June 2014.

- ↑ 10.0 10.1 "Project Catapult". Microsoft Research. July 2018.

- ↑ Maxfield, Max. "Xilinx UltraScale FPGA Offers 50 Million Equivalent ASIC Gates". www.eetimes.com. EE Times.

- ↑ 12.0 12.1 Dylan McGrath, EE Times, "FPGA Market to Pass $2.7 Billion by '10, In-Stat Says". May 24, 2006. Retrieved February 5, 2009.

- ↑ 13.0 13.1 "Global FPGA Market Analysis And Segment Forecasts To 2020 – FPGA Industry, Outlook, Size, Application, Product, Share, Growth Prospects, Key Opportunities, Dynamics, Trends, Analysis, FPGA Report – Grand View Research Inc". grandviewresearch.com.

- ↑ Dylan McGrath, EE Times, "Gartner Dataquest Analyst Gives ASIC, FPGA Markets Clean Bill of Health". June 13, 2005. Retrieved February 5, 2009.

- ↑ "Virtex-4 Family Overview" (PDF). xilinx.com. Retrieved 14 April 2018.

- ↑ Wisniewski, Remigiusz (2009). Synthesis of compositional microprogram control units for programmable devices. Zielona Góra: University of Zielona Góra. p. 153. ISBN 978-83-7481-293-1.[permanent dead link]

- ↑ "FPGA Architecture for the Challenge". toronto.edu. University of Toronto.

- ↑ "FPGA Signal Integrity tutorial". altium.com. Archived from the original on 2016-03-07. Retrieved 2010-06-15.

- ↑ Mike Thompson. "Mixed-signal FPGAs provide GREEN POWER"[permanent dead link]. EE Times, 2007-07-02.

- ↑ 2. CycloneII Architecture. Altera. February 2007

- ↑ "Documentation: Stratix IV Devices" (PDF). Altera.com. 2008-06-11. Archived from the original (PDF) on 2011-09-26. Retrieved 2013-05-01.

- ↑ Virtex-4 FPGA User Guide (December 1st, 2008). Xilinx, Inc.

- ↑ WO 1983001325, Genter, Mel & Potash, Hanan, "Digital device with interconnect matrix", issued 1981-09-29, assigned to Burroughs Corp. and Burroughs Machines Ltd.

- ↑ "Xilinx Inc, Form 8-K, Current Report, Filing Date Oct 19, 2011". secdatabase.com. Retrieved May 6, 2018.

- ↑ "Xilinx Inc, Form 10-K, Annual Report, Filing Date May 31, 2011". secdatabase.com. Retrieved May 6, 2018.

- ↑ Dean Takahashi, VentureBeat. "Intel connection helped chip startup Tabula raise $108M." May 2, 2011. Retrieved May 13, 2011.

- ↑ 27.0 27.1 Lawrence Latif, The Inquirer. "FPGA manufacturer claims to beat Moore's Law." October 27, 2010. Retrieved May 12, 2011.

- ↑ EDN Europe. "Xilinx adopts stacked-die 3D packaging Archived 2011-02-19 at the Wayback Machine." November 1, 2010. Retrieved May 12, 2011.

- ↑ Saban, Kirk (December 11, 2012). "Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity, Bandwidth, and Power Efficiency" (PDF). xilinx.com. Retrieved 2018-11-30.

- ↑ "Intel Custom Foundry EMIB". Intel.

- ↑ "Battle Over the FPGA: VHDL vs Verilog! Who is the True Champ?". digilentinc.com (in English). Retrieved 2020-12-16.

- ↑ "Why use OpenCL on FPGAs?". StreamComputing. 2014-09-16. Archived from the original on 2017-01-01. Retrieved 2015-07-17.

- ↑ 33.0 33.1 "All about FPGAs".

- ↑ Dillien, Paul (March 6, 2017). "And the Winner of Best FPGA of 2016 is..." EETimes. Archived from the original on January 5, 2019. Retrieved September 7, 2017.

- ↑ "Xilinx ISE Design Suite". www.xilinx.com. Retrieved 2018-12-01.

- ↑ "FPGA Design Software - Intel Quartus Prime". Intel (in English). Retrieved 2018-12-01.

- ↑ "Top FPGA Companies For 2013". SourceTech411 (in English). 2013-04-28. Retrieved 2018-12-01.

- ↑ "QuickLogic — Customizable Semiconductor Solutions for Mobile Devices". www.quicklogic.com (in English). QuickLogic Corporation. Retrieved 2018-10-07.

- ↑ "Achronix to Use Intel's 22nm Manufacturing". Intel Newsroom (in English). 2010-11-01. Retrieved 2018-12-01.

- ↑ "Tabula's Time Machine — Micro Processor Report" (PDF). Archived from the original (PDF) on 2011-04-10.

- ↑ Tabula to shut down; 120 jobs lost at fabless chip company Silicon Valley Business Journal

- ↑ "Intel to buy Altera for $16.7 billion in its biggest deal ever". Reuters. June 2015.

- ↑ "AMD to Acquire Xilinx, Creating the Industry's High Performance Computing Leader". October 2020.

- ↑ "Xilinx Inc, Form 8-K, Current Report, Filing Date Apr 26, 2006". secdatabase.com. Retrieved May 6, 2018.

- ↑ "Publications and Presentations". bdti.com. Archived from the original on 2010-08-21. Retrieved 2018-11-02.

- ↑ LaPedus, Mark. "Xilinx aims 65-nm FPGAs at DSP applications". EETimes.

- ↑ Alcaín, Eduardo; Fernández, Pedro R.; Nieto, Rubén; Montemayor, Antonio S.; Vilas, Jaime; Galiana-Bordera, Adrian; Martinez-Girones, Pedro Miguel; Prieto-de-la-Lastra, Carmen; Rodriguez-Vila, Borja; Bonet, Marina; Rodriguez-Sanchez, Cristina (2021-12-15). "Hardware Architectures for Real-Time Medical Imaging". Electronics (in English). 10 (24): 3118. doi:10.3390/electronics10243118. ISSN 2079-9292.

- ↑ Nagornov, Nikolay N.; Lyakhov, Pavel A.; Valueva, Maria V.; Bergerman, Maxim V. (2022). "RNS-Based FPGA Accelerators for High-Quality 3D Medical Image Wavelet Processing Using Scaled Filter Coefficients". IEEE Access. 10: 19215–19231. doi:10.1109/ACCESS.2022.3151361. ISSN 2169-3536. S2CID 246895876.

- ↑ Morgan, Timothy Pricket (2014-09-03). "How Microsoft Is Using FPGAs To Speed Up Bing Search". Enterprise Tech. Retrieved 2018-09-18.

- ↑ "Gigabyte's i-RAM: Affordable Solid State Storage". anandtech.com (in English). 2005-07-25. Retrieved 2020-12-16.

- ↑ "FPGA development devices for radiation-hardened space applications introduced by Microsemi". www.militaryaerospace.com. 2016-06-03. Retrieved 2018-11-02.

- ↑ "CrypTech: Building Transparency into Cryptography t" (PDF).

- ↑ Huffmire, Ted; Brotherton, Brett; Sherwood, Timothy; Kastner, Ryan; Levin, Timothy; Nguyen, Thuy D.; Irvine, Cynthia (2008). "Managing Security in FPGA-Based Embedded Systems". IEEE Design & Test of Computers. 25 (6): 590–598. doi:10.1109/MDT.2008.166. S2CID 115840.

- ↑ "EETimes on PUF: Security features for non-security experts – Intrinsic ID". Intrinsic ID. 2015-06-09.

- ↑ Skorobogatov, Sergei; Woods, Christopher (2012). "Breakthrough Silicon Scanning Discovers Backdoor in Military Chip". Cryptographic Hardware and Embedded Systems – CHES 2012. Lecture Notes in Computer Science. Vol. 7428. pp. 23–40. doi:10.1007/978-3-642-33027-8_2. ISBN 978-3-642-33026-1.

- ↑ 56.0 56.1 Kuon, Ian; Rose, Jonathan (2006). "Measuring the gap between FPGAs and ASICs" (PDF). Proceedings of the international symposium on Field programmable gate arrays – FPGA'06. New York, NY: ACM. pp. 21–30. doi:10.1145/1117201.1117205. ISBN 1-59593-292-5. Archived from the original (PDF) on 2010-06-22. Retrieved 2017-10-25.

- ↑ "ASIC, ASSP, SoC, FPGA – What's the Difference?". eetimes.com.

- ↑ Cutress, Ian (August 27, 2019). "Xilinx Announces World Largest FPGA: Virtex Ultrascale+ VU19P with 9m Cells". AnandTech.

- ↑ "AN 818: Static Update Partial Reconfiguration Tutorial: for Intel Stratix 10 GX FPGA Development Board". www.intel.com. Retrieved 2018-12-01.

- ↑ "Can FPGAs dynamically modify their logic?". Electrical Engineering Stack Exchange. Retrieved 2018-12-01.

- ↑ "CPLD vs FPGA: Differences between them and which one to use? – Numato Lab Help Center". numato.com. 2017-11-29.

अग्रिम पठन

- Sadrozinski, Hartmut F.-W.; Wu, Jinyuan (2010). Applications of Field-Programmable Gate Arrays in Scientific Research. Taylor & Francis. ISBN 978-1-4398-4133-4.

- Wirth, Niklaus (1995). Digital Circuit Design An Introduction Textbook. Springer. ISBN 978-3-540-58577-0.

- Mitra, Jubin (2018). "An FPGA-Based Phase Measurement System". IEEE Transactions on Very Large Scale Integration (VLSI) Systems. IEEE. 26: 133–142. doi:10.1109/TVLSI.2017.2758807. S2CID 4920719.

- Mencer, Oskar et al. (2020). "The history, status, and future of FPGAs". Communications of the ACM. ACM. Vol. 63, No. 10. doi:10.1145/3410669

बाहरी संबंध

]

]